- •САПР Xilinx Foundation Series

- •ВХОД В СИСТЕМУ

- •Открытие нового проекта

- •ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ

- •Как задать размер листа и присвоить ему имя

- •ОСНОВНЫЕ ОПЕРАЦИИ

- •Выбор элемента

- •Перемещение элемента или фрагмента схемы

- •Удаление элемента

- •Присвоение имени элементу

- •Рисование цепи

- •Перемещение цепи

- •Удаление цепи

- •Присвоение имени цепи

- •Переименование цепи

- •Удаление имени цепи

- •Задание констант 0 и 1

- •ШИННЫЕ СОЕДИНЕНИЯ

- •Пример простого шинного соединения

- •Шинные контакты элемента

- •Правила соединений

- •Простые и сложные шины

- •Примеры шинных соединений

- •Редактирование изображения шины

- •Контроль соединений

- •Сохранение схемы

- •ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ ЭЛЕМЕНТОВ

- •СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ БАЗОВЫХ ЭЛЕМЕНТОВ

- •Создание макроэлемента

- •Выбор макроэлемента из библиотеки

- •Редактирование УГО макроэлемента

- •ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL

- •Ввод описания макроэлемента

- •Ввод описания архитектуры объекта с использованием Language Assistant

- •Сохранение документа

- •Проверка синтаксиса

- •Редактирование текста описания

- •Синтез макроэлемента

- •Создание VHDL-макроса

- •Выбор макроса из библиотеки

- •Редактирование УГО макроэлемента

- •Коррекция VHDL-описания макроэлемента

- •Автоматическое создание модели памяти

- •Редактирование начального состояния памяти

- •ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Окно моделирования схемы

- •Выбор контрольных точек схемы

- •Удаление контрольных точек из окна моделирования

- •Изменение порядка имен в окне моделирования

- •Задание входных воздействий

- •Задание синхросигналов

- •Как отсоединить генератор от внешнего входа схемы

- •Задание входных воздействий в окне моделирования

- •Выполнение моделирования схемы

- •Сохранение результатов моделирования

- •Моделирование макроэлемента

- •РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС

- •ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

- •Универсальный лабораторный стенд

- •Макроэлементы органов управления стенда

- •Подключение макроэлементов стенда к проекту

- •РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ

- •ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Измерение задержек на временной диаграмме

- •ЗАГРУЗКА ПРОЕКТА В ПЛИС

- •ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ

- •ВВЕДЕНИЕ В ЯЗЫК VHDL

- •ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL

- •Структура описания объекта проекта

- •Интерфейс объекта проекта

- •Синтаксис

- •Тип сигнала

- •О правилах записи программы

- •Описание архитектуры объекта

- •Синтаксис

- •Параллельные операторы

- •Стили описаний архитектур

- •Элементы потокового проектирования

- •Элементы поведенческого проектирования

- •VHDL-стандарты IEEE

- •Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned

- •Библиотеки и пакеты

- •Логические элементы

- •Триггеры

- •Мультиплексоры

- •Дешифратор

- •Сумматоры

- •Счетчики

- •Регистры

- •Исходные данные

- •Составление программной модели АЛУ

- •СПИСОК ЛИТЕРАТУРЫ

Рис. 82. Этапы проектирования цифрового устройства на ПЛИС

ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

Перед размещением схемы на ПЛИС её необходимо надлежащим образом подготовить. Для этого следует определить, какие точки схемы будут выводиться на внешние контакты корпуса ПЛИС. Контакты корпуса ПЛИС уже распаяны на печатной плате универсального лабораторного стенда и выведены на его органы управления (генераторы, клавишные регистры и индикаторы). Поэтому подготовка схемы сводится к подключению органов управления стенда, которые в системе проектирования оформлены в виде макроэлементов. Таким образом, подготовка сводится к подключению данных макроэлементов к схеме с целью дальнейшего её размещения на ПЛИС.

Универсальный лабораторный стенд

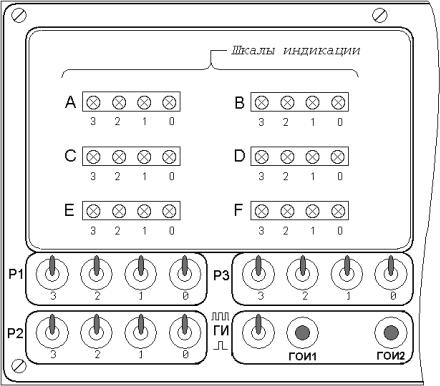

В практикумах по курсам «Схемотехника ЭВМ» и «Организация систем» используется только часть оборудования универсального стенда, а именно: ПЛИС FPGA XCS10-3PC84, клавишные регистры, генераторы и индикация. Часть лицевой панели стенда с используемыми органами управления приведена на рис. 83.

80

Рис. 83. Органы управления и индикации стенда

На стенде для задания воздействий на схему имеются:

•два генератора одиночных импульсов — ГОИ1 и ГОИ2, первый из них может работать в одном из двух режимов — либо в режиме одиночных импульсов, либо в режиме непрерывных импульсов; выбор режима осуществляется крайним левым переключателем (см. рис. 83);

•три клавишных регистра, используемых для задания постоянных значений.

Для целей контроля состояния схемы в процессе её отладки на стенде имеются шесть четырехразрядных светодиодных шкал, которые можно подключать к произвольным точкам схемы (см. рис. 83). Таким образом, можно одновременно наблюдать состояние схемы в 24 точках.

Макроэлементы органов управления стенда

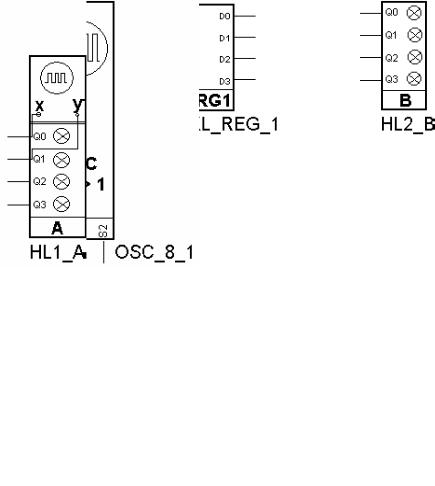

Перечисленные выше органы управления и индикации стенда в системе проектирования представлены в виде макроэлементов

(рис. 84).

Два генератора импульсов ГОИ1 и ГОИ2 представлены одним символом (см. рис. 84, а), которому присвоено имя GI_GOI.

Клавишные регистры (см. рис. 84, б) имеют обозначение

KL_REG_1, KL_REG_2 и KL_REG_3.

Пример условного графического обозначения четырехразрядных светодиодных шкал приведен на рис. 84, в). Макроэлементы светодиодных шкал имеют следующие имена: HL1_A, HL2_B, HL3_C, HL4_D, HL5_E, HL6_F.

Помимо перечисленных макроэлементов в системе проектирования имеется два альтернативных макроэлемента, представляющие осциллограф (рис. 85). Блок осциллографический цифровой BORDO 210 конструктивно выполнен в виде платы расширения ПЭВМ. Осциллограф подключен к внешним контактам корпуса ПЛИС. Через макроэлементы пользователь может подключить к осциллографу любые точки спроектированной схемы.

С помощью макроэлемента, имеющего имя OSC_8_1 (см. рис. 85, а), пользователь имеет возможность подключить для наблюдения на экране дисплея восемь точек своей схемы. Выбор

82

конкретной точки наблюдения на экране дисплея осуществляется подачей соответствующего кода на входы S2, S1, S0 (см. рис. 85, а). Это реализуется подключением к данным входам одого из клавишных регистров.

|

|

|

а |

б |

в |

Рис. 84. Условные графические обозначения макролементов управления и индикации стенда

|

|

|

а |

|

б |

Рис. 85. Условные графические обозначения осциллографа

83

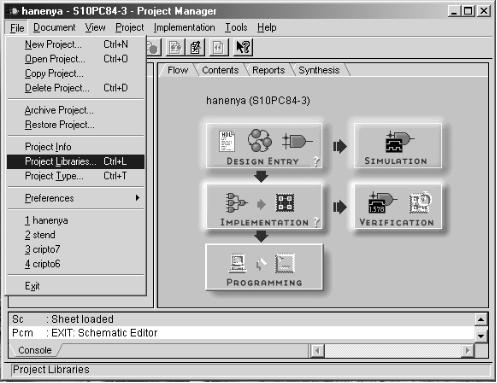

Рис. 86. Выбор окна Project Libraries