- •САПР Xilinx Foundation Series

- •ВХОД В СИСТЕМУ

- •Открытие нового проекта

- •ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ

- •Как задать размер листа и присвоить ему имя

- •ОСНОВНЫЕ ОПЕРАЦИИ

- •Выбор элемента

- •Перемещение элемента или фрагмента схемы

- •Удаление элемента

- •Присвоение имени элементу

- •Рисование цепи

- •Перемещение цепи

- •Удаление цепи

- •Присвоение имени цепи

- •Переименование цепи

- •Удаление имени цепи

- •Задание констант 0 и 1

- •ШИННЫЕ СОЕДИНЕНИЯ

- •Пример простого шинного соединения

- •Шинные контакты элемента

- •Правила соединений

- •Простые и сложные шины

- •Примеры шинных соединений

- •Редактирование изображения шины

- •Контроль соединений

- •Сохранение схемы

- •ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ ЭЛЕМЕНТОВ

- •СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ БАЗОВЫХ ЭЛЕМЕНТОВ

- •Создание макроэлемента

- •Выбор макроэлемента из библиотеки

- •Редактирование УГО макроэлемента

- •ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL

- •Ввод описания макроэлемента

- •Ввод описания архитектуры объекта с использованием Language Assistant

- •Сохранение документа

- •Проверка синтаксиса

- •Редактирование текста описания

- •Синтез макроэлемента

- •Создание VHDL-макроса

- •Выбор макроса из библиотеки

- •Редактирование УГО макроэлемента

- •Коррекция VHDL-описания макроэлемента

- •Автоматическое создание модели памяти

- •Редактирование начального состояния памяти

- •ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Окно моделирования схемы

- •Выбор контрольных точек схемы

- •Удаление контрольных точек из окна моделирования

- •Изменение порядка имен в окне моделирования

- •Задание входных воздействий

- •Задание синхросигналов

- •Как отсоединить генератор от внешнего входа схемы

- •Задание входных воздействий в окне моделирования

- •Выполнение моделирования схемы

- •Сохранение результатов моделирования

- •Моделирование макроэлемента

- •РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС

- •ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

- •Универсальный лабораторный стенд

- •Макроэлементы органов управления стенда

- •Подключение макроэлементов стенда к проекту

- •РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ

- •ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Измерение задержек на временной диаграмме

- •ЗАГРУЗКА ПРОЕКТА В ПЛИС

- •ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ

- •ВВЕДЕНИЕ В ЯЗЫК VHDL

- •ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL

- •Структура описания объекта проекта

- •Интерфейс объекта проекта

- •Синтаксис

- •Тип сигнала

- •О правилах записи программы

- •Описание архитектуры объекта

- •Синтаксис

- •Параллельные операторы

- •Стили описаний архитектур

- •Элементы потокового проектирования

- •Элементы поведенческого проектирования

- •VHDL-стандарты IEEE

- •Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned

- •Библиотеки и пакеты

- •Логические элементы

- •Триггеры

- •Мультиплексоры

- •Дешифратор

- •Сумматоры

- •Счетчики

- •Регистры

- •Исходные данные

- •Составление программной модели АЛУ

- •СПИСОК ЛИТЕРАТУРЫ

2.В этом окне щелкните кнопку Configure LogiBlox Symbol

(см. рис. 66). Появится окно Xilinx LogiBLOX Module Selector с

параметрами созданной памяти (рис. 67).

3.Щелкнув кнопку Edit в окне Xilinx LogiBLOX Module Selector, вы откроете файл задания начального состояния памяти

(см. рис. 64).

ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

Окно моделирования схемы

Открыть окно моделирования схемы можно одним из следующих способов:

щелкнуть мышью пиктограмму «Simulator»  на горизонтальной панели инструментов

на горизонтальной панели инструментов

редактора схем;

щелкнуть мышью пиктограмму «Simulation»

в окне Project Manager.

На рис. 68 приведено окно моделирования схемы Logic Simulator.

Панель инструментов

Строка меню

Поле имен |

Поле временных диаграмм |

Рис. 68. Окно моделирования схемы

67

Панель инструментов окна моделирования

Верхний ряд панели инструментов:

— загрузка временной диаграммы;

— cохранение временной диаграммы;

— печать временной диаграммы;

— открытие окна менеджера проектов;

— открытие окна редактора схем;

— задание частоты синхросигналов;

— выбор режима моделирования;

— возврат моделирования в нулевой момент времени;

— выполнение моделирования по шагам;

— выбор шага моделирования;

— останов моделирования при генерации схемы.

Нижний ряд панели инструментов:

— выключение шкалы времени в поле временных диаграмм;

— удаление всех временных диаграмм в окне моделирования;

— выключение/включение вставленного комментария на временной диаграмме;

— выключение/включение вставленного измерения временных интервалов;

— разгруппировка свернутой группы сигналов;

68

— выбор контрольных точек схемы;

— задание периодических входных воздействий;

— задание состояния сигнала;

— изменение масштаба шкалы времени.

— изменение масштаба шкалы времени.

Выбор контрольных точек схемы

Выбор контрольных точек предполагает выбор как внешних входов схемы, так и требуемых точек схемы для просмотра временных диаграмм.

1. Щелкните кнопку выбора контрольных точек на панели  инструментов окна моделирования.

инструментов окна моделирования.

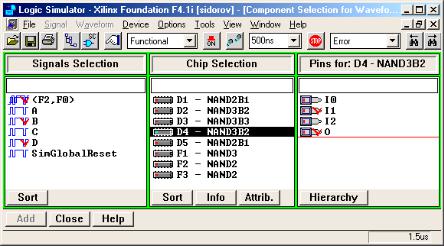

Появится окно выбора контролируемых точек (рис. 69). Окно имеет три колонки: Signals selection — колонка имен цепей и шин,

Chip selection — колонка имен элементов, Scan Hierarchy — ко-

лонка имен элементов, входящих в макроэлементы.

Рис. 69. Окно выбора контрольных точек

2. Выберите имя в левой колонке Signals selection, затем нажмите кнопку Add. Альтернативный способ — двойной щелчок на

69

имени цепи или шины. Выбранное имя будет помечено галочкой красного цвета (рис. 70).

3.Для просмотра временных диаграмм на контактах элемента дважды щелкните имя элемента в средней колонке Chip selection. После этого в правой колонке окна появится список контактов выбранного элемента и колонка сменит заголовок на Pins for: с указанием имени выбранного элемента (см. рис. 70).

4.Выберите двойным щелчком мыши контакт элемента в правом столбце окна. Выбранный контакт будет помечен галочкой (см.

рис. 70).

Рис. 70. Окно выбора контрольных точек элемента

5.Повторите пп. 3 — 4 для других элементов, временные диаграммы которых необходимо вывести на просмотр.

6.Нажмите кнопку Close, чтобы завершить операцию выбора контрольных точек схемы.

Удаление контрольных точек из окна моделирования

Выделите в поле имен окна моделирования имя сигнала, который хотите удалить и нажмите правую клавишу мыши. В появив-

70