- •Курс лекций «узлы цифровых эвм»

- •Оглавление

- •Регистры

- •Параллельные регистры

- •Счетчики

- •Узлы цифровых устройств Сумматор поmod2 (Исключающее или).

- •Синтез мажоритарного элемента.

- •Дешифраторы

- •Шифраторы

- •Сдвигатели

- •Мультиплексоры и демультиплексоры

- •Схемы сравнения двоичных чисел (Компараторы)

- •Преобразователи кодов

- •Распределители импульсов

- •Двоичные сумматоры

Двоичные сумматоры

Процесс двоичного суммирования описывается следующей таблицей истинности:

|

ai |

bi |

pi-1 |

si |

pi |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

К

арта

Карно для поразрядной суммыsiи переносаpiбудут иметь вид:

арта

Карно для поразрядной суммыsiи переносаpiбудут иметь вид:

Отсюда находим следующие дизъюнктивные нормальные формы:

![]() ,

,

![]() .(*)

.(*)

Найдём также конъюнктивные нормальные формы:

![]()

![]()

![]()

![]()

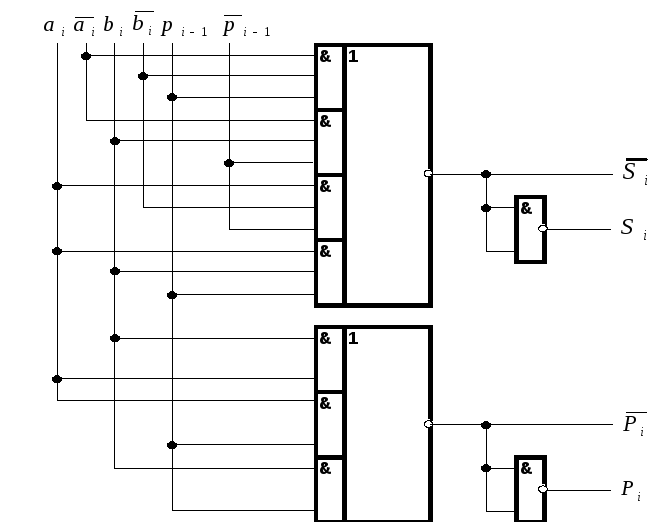

Н айденные

дизъюнктивные нормальные формы легко

реализуются на элементахИ-ИЛИ-НЕ:

айденные

дизъюнктивные нормальные формы легко

реализуются на элементахИ-ИЛИ-НЕ:

Очевидно, что прямые значения суммы и переноса здесь могут быть получены непосредственно с выходов элементов И-ИЛИ-НЕесли значения всех входных сигналов изменить на противоположные.

Схемы сумматоров, построенные непосредственно на основе найденных четырех уравнений, требуют как прямых, так и инверсных значений слагаемых. Однако можно найти логическое уравнение для суммы, в котором отсутствуют инверсные значения слагаемых и входного переноса. Дизъюнктивную нормальную форму для si дополним шестью нулевыми слагаемыми и получим:

Реализуем это уравнение и уравнение (*)на элементахИ-ИЛИ-НЕ:

П о

числу входов и по нагрузке на входные

сигналы эта схема экономичнее, чем

предыдущая. Если на её входы подать

инверсные значения входных сигналов,

то непосредственно с выходов элементовИ-ИЛИ-НЕможно получить прямые

значенияsiиpi.

о

числу входов и по нагрузке на входные

сигналы эта схема экономичнее, чем

предыдущая. Если на её входы подать

инверсные значения входных сигналов,

то непосредственно с выходов элементовИ-ИЛИ-НЕможно получить прямые

значенияsiиpi.

На структурных схемах одноразрядный двоичный сумматор обозначается так:

П олученные

ранее логические уравнения сумматора

преобразуем следующим образом:

олученные

ранее логические уравнения сумматора

преобразуем следующим образом:

![]()

д обавим

с учётом правила поглощения

обавим

с учётом правила поглощения

![]()

Отсюда следует, что схема одноразрядного двоичного сумматора может быть построена и на сумматорах по модулю 2:

![]()

П редыдущие

две схемы комбинационных сумматоров

были двухкаскадными, поэтому задержка

сигнала переносаpiв них

равна2tзср.

В схеме на сумматорах помодулю 2в цепи переноса использовано два

логических элемента, следовательно

здесь задержка распространения сигнала

переноса тоже равна2tзср.

редыдущие

две схемы комбинационных сумматоров

были двухкаскадными, поэтому задержка

сигнала переносаpiв них

равна2tзср.

В схеме на сумматорах помодулю 2в цепи переноса использовано два

логических элемента, следовательно

здесь задержка распространения сигнала

переноса тоже равна2tзср.

Схема N-разрядного комбинационного сумматора имеет вид:

Е сли

задержка сигнала переноса на одноразрядном

комбинационном сумматоре равна2tзср,

то максимальная длительность переходного

процесса вN-разрядном

комбинационном сумматоре равна2Ntзср.

Эта величина определяет максимальную

длительность микрооперации сложения.

Присинхронномпринципе работы

устройств ЭВМ длительность микрооперации

сложения независимо от наличия переносов

всегда берётся равной

сли

задержка сигнала переноса на одноразрядном

комбинационном сумматоре равна2tзср,

то максимальная длительность переходного

процесса вN-разрядном

комбинационном сумматоре равна2Ntзср.

Эта величина определяет максимальную

длительность микрооперации сложения.

Присинхронномпринципе работы

устройств ЭВМ длительность микрооперации

сложения независимо от наличия переносов

всегда берётся равной![]() ,

гдеk=1.11.25– коэффициент запаса, берётся из-за

нестабильности задержек в логических

элементах.

,

гдеk=1.11.25– коэффициент запаса, берётся из-за

нестабильности задержек в логических

элементах.

Случай суммирования с наличием переносов между всеми разрядами сумматора маловероятен. Считается, что в 40-разрядном сумматоре среднее количество соседних разрядов, охваченных переносом, в57раз меньше предельного значения. Поэтому быстродействие машины можно повысить, если использоватьасинхронныйпринцип сложения и за счёт контроля момента окончания переносов в сумматоре отказаться от запаса на время выполнения суммирования.

Особенность асинхронного сумматорасостоит в следующем.

Минимальная дизъюнктивная

нормальная форма для сигнала переноса

имеет вид:

![]() или:

или:![]() .

.

Функция, определяющая отсутствие переноса имеет вид:

![]()

Преобразуем:

Логическое выражение для сигнала окончания сложения в одном разряде сумматора будет иметь вид:

![]()

т.е. i=1, если в данном разряде сумматора сигнал переноса определён либо значениемp=1, либо значением=1.

С

i

М икрооперация

сложения заканчивается, если на выходах

всех разрядов сумматора сигналыiпринимают значение1, т.е. если

выполняется условие:

икрооперация

сложения заканчивается, если на выходах

всех разрядов сумматора сигналыiпринимают значение1, т.е. если

выполняется условие:

![]()

Для выработки сигнала

к сумматору

подключается элементИсNвходами. В самом неблагоприятном случае

длительность микрооперации сложения

равна предельному значению![]() Однако, в среднем время выполнения

операции оказывается значительно

меньше предельного значенияtслmax.

Выигрыш во времени здесь достигнут за

счёт увеличения аппаратурных затрат.

Однако, в среднем время выполнения

операции оказывается значительно

меньше предельного значенияtслmax.

Выигрыш во времени здесь достигнут за

счёт увеличения аппаратурных затрат.