- •Курс лекций «узлы цифровых эвм»

- •Оглавление

- •Регистры

- •Параллельные регистры

- •Счетчики

- •Узлы цифровых устройств Сумматор поmod2 (Исключающее или).

- •Синтез мажоритарного элемента.

- •Дешифраторы

- •Шифраторы

- •Сдвигатели

- •Мультиплексоры и демультиплексоры

- •Схемы сравнения двоичных чисел (Компараторы)

- •Преобразователи кодов

- •Распределители импульсов

- •Двоичные сумматоры

Узлы цифровых устройств Сумматор поmod2 (Исключающее или).

Сумматор по модулю 2 на два входа реализует функцию неравнозначности. Функция неравнозначности истинна, когда один её аргумент истинный, а второй ложный. Таблица истинности и условное обозначение сумматора по модулю 2 на два входа приведены ниже:

-

X1

x2

y

y

0

0

0

0

1

1

1

0

1

1

1

0

Из таблицы

истинности следует :

![]() .

.

Примеры сумматоров:

И

– ИЛИ

– ИЛИИ – ИЛИ – НЕ

Из

таблицы истинности находим

![]()

О тсюда

тсюда![]()

И - НЕ

![]()

добавим :

![]()

Исключающее ИЛИ (сумматор по модулю 2) выпускается в виде микросхем, например, К155ЛП5 – в одном корпусе четыре независимых элемента.

ИЛИ – НЕ

![]()

Таблица истинности и карта Карно функции суммы по модулю 2 для трех переменных:

-

x1

x2

x3

y

0

0

0

0

00

0

1

1

0

1

0

1

0

1

1

0

1

0

0

1

1

0

1

0

1

1

0

0

1

1

1

1

![]()

Сумма по модулю 2 от Nаргументов представляет собой функцию, которая истинна, если истинно нечетное число её аргументов (функция нечетности).

Построение функции нечетности непосредственно в соответствии с её ДНФ ограничивается возможностями системы элементов. Поэтому при построении схем формирования нечетности используют последовательное включение сумматоров по модулю 2.

Синтез мажоритарного элемента.

Для примера рассмотрим трехвходовый мажоритарный элемент. Выходной сигнал такого элемента совпадает с большинством входных сигналов, как это следует из таблицы истинности:

|

x1 |

x2 |

x3 |

|

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

Отсюда находим логическое уравнение трехвходового мажоритарного элемента:

![]()

Реализуем его на логических элементах И-НЕ, для этого запишем в виде:

![]()

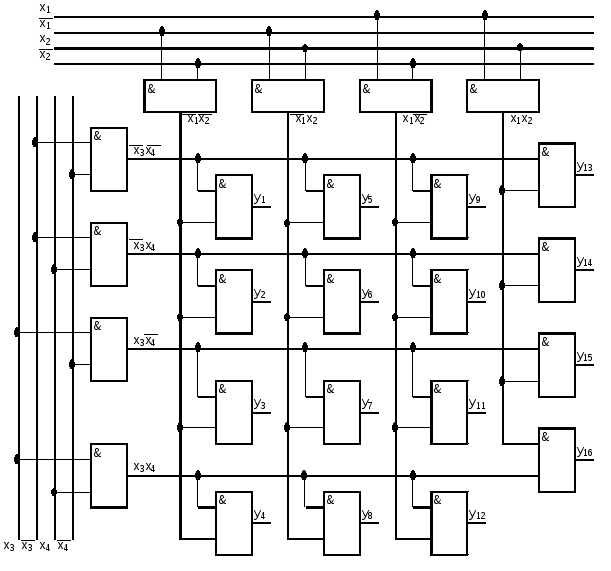

Дешифраторы

Дешифраторы и шифраторы принадлежат к числу преобразователей кодов. С понятием шифрации связано представление о сжатии данных; с понятием дешифрации – обратное преобразование.

Полным дешифратором называют комбинационную схему, имеющую nвходов и2nвыходов, которая реализует2nлогических функций:

![]() ,

,

![]() ,

,

![]() ,

,

![]() ,

,

![]() ,

где

,

где![]() .

.

Каждая логическая

функция

![]() является конституентой единицы.

является конституентой единицы.

Д ешифратор

(DC-decoder)

преобразует двоичный код в код«1 из

N».

ешифратор

(DC-decoder)

преобразует двоичный код в код«1 из

N».

Условное обозначение дешифратора:

По способу организации дешифрации слова дешифраторы классифицируют на прямоугольные (матричные), пирамидальные и ступенчатые (каскадные).

Таблица истинности для 4-х входного полного дешифратора:

|

x1 |

x2 |

x3 |

x4 |

y1 |

y2 |

y3 |

y4 |

y5 |

y6 |

y7 |

y8 |

y9 |

y10 |

y11 |

y12 |

y13 |

y14 |

y15 |

y16 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Логические выражения для выходных сигналов будут иметь вид:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

В матричном (прямоугольном) дешифраторе

они реализуются следующим образом:

матричном (прямоугольном) дешифраторе

они реализуются следующим образом:

Матричные дешифраторы просты, однако при большом nтребуются элементы с большим коэффициентом разветвления по выходу.

Пирамидальные дешифраторы состоят из нескольких ступеней в которых каждая конституента образуется как конъюнкция одной из частичных конституент и одного из разрядов слова (в прямом или инверсном представлении), которые не использовались для её построения (Частичная конституента включает часть разрядов дешифруемого слова).

Количество ступеней пирамидального дешифратора Kст=n-1.

Требуемое число двухвходовых элементов И равно:

![]() .

.

Недостатком схемы пирамидального дешифратора является неравномерная нагрузка на входы, кроме того они требуют больше аппаратурных затрат, чем матричные.

Дешифраторы с большим числом входов строятся по матричному принципу, при этом синтезируются так называемые ступенчатые (каскадные) дешифраторы.

Многоступенчатые дешифраторы являются наиболее экономичными. Принцип их построения состоит в следующем. Дешифрируемое слово разбивается на две группы. Затем каждая группа снова разбивается на две группы и так до тех пор, пока в каждой группе останется не больше трёх разрядов исходного слова. На основании такой разбивки можно осуществить синтез схемы и определить основные характеристики многоступенчатой схемы дешифратора.

П ример

разбивки десятиразрядного и

тринадцатиразрядного двоичного слова:

ример

разбивки десятиразрядного и

тринадцатиразрядного двоичного слова:

Например, схема трехступенчатого дешифратора на 8 входов и 256 выходов имеет вид:

В некоторых случаях функцией дешифратора является выделение менее чем 2nнаборов, т.е.m<2n. При этом предполагается, что(2n-m)наборов либо не могут существовать, либо значения сигналов на выходе дешифратора при поступлении на вход любого из(2n-m)наборов безразлично, т.е. наборы несущественны.

Дешифратор n-разрядного двоичного кода с числом выходовm<2nназывается неполным дешифратором. При построении схемы неполного дешифратора несущественные наборы могут использоваться для упрощения схемы дешифратора.

Пусть, например,

дешифратор четырехразрядного двоичного

кода

![]() используется для выделения шести

наборов:

используется для выделения шести

наборов:

|

0000 |

|

|

0101 |

|

|

1001 |

|

|

1010 |

|

|

1100 |

|

|

1111 |

|

Остальные десять наборов являются несущественными.

Н анесём

все наборы на карту Карно:

анесём

все наборы на карту Карно:

Доопределим карту Карно и получим:

|

|

|

|

|

|

|

|

С хема

дешифратора в этом случае будет иметь

вид:

хема

дешифратора в этом случае будет иметь

вид:

y

y