- •Системы потенциальных элементов на биполярных транзисторах

- •Элементы на униполярных транзисторах.

- •Генераторы и одновибраторы

- •В обоих схемах резисторы r1,r2,r должны удовлетворять тем же требованиям. Для плавного изменения параметров последовательности импульсов в схему генератора вводят переменные резисторы:

- •Асинхронные триггеры

- •Первая минимальная форма

- •Нанесём значения ина объединённую карту Карно Заключим в скобки установившиеся сочетания пар и

- •Вторая минимальная форма. Доопределим функцию в двух нижних строках таблицы нулями

- •Третья минимальная форма.

- •Четвёртая минимальная форма.

РИП

Литература: Угрюмов Е.П. «Элементы и узлы ЭЦВМ» М. ВШ. 1976г.

Угрюмов Е. П. «Проектирование элементов и узлов ЭВМ» М. ВШ. 1987

1. История развития элементной базы ВТ (самостоятельно)

2. Понятие о системах элементов.

Система элементов – типовой набор элементов, достаточный для реализации любых схем заданного класса.

В настоящее время в ВТ используется 3 типа систем полупроводниковых элементов.

а) Системы импульсно-потенциальных элементов (СИПЭ)

старейшая, перешла от ламповых схем.

обладает большой функциональной способностью.

дает малый расход элементов при построении узлов ЭВМ.

Однако:

характерно довольно большое число типов элементов.

применение конденсаторов и трансформаторов, что затрудняет изготовление в виде ИС.

б) Система потенциальных элементов (СПЭ) сейчас наиболее распространена, а в интегральной электронике она доминирует.

в) Система динамических элементов (СДЭ) начала получать распространение в последнее время в связи с появлением элементов на МОП транзисторах, обладающих важными достоинствами.

3. Основные характеристики логических элементов.

температурный диапазон

надёжность

стоимость

функциональные возможности логического элемента характеризуются выполняемой им операцией или набором логических операций.

коэффициент разветвления n– число входов последующих элементов, которые могут управляться от выхода данного элемента.

коэффициент объединения m– число входов, которое может иметь данный элемент.

Величины nиmограничиваются условиями сохранения нормального электрического режима элемента, а также быстродействием, которое снижается из-за емкости.

нагрузочная способность - определяется в общем случае током который может быть отдан элементом во внешние цепи (нагрузку). В частности, в случае однородных нагрузок, нагрузочная способность оценивается коэффициентом разветвления n.

быстродействие определяется временем перехода элемента из состояния “0” в “1” и обратно.

Переходные процессы изменения состояния элемента состоят из этапов задержки и формирования фронта или спада сигнала.

Длительности задержек и фронтов характеризуют динамические свойства логических элементов. Однако чаще всего быстродействие элементов оценивают одной характеристикой – средним временем задержки. Причём отсчёт ведут как правило на уровне 0,5 от установившегося значения сигнала.

Так как длительности переходных процессов при включении и выключении элемента в общем случае не равны, то рассчитывают среднее время задержки сигнала на элемент. При формировании спада время задержки составит: tз′=tз сп+tсп/2, а время задержки при формировании фронта:tз′′=tз ф+tф/2. Среднее время задержки на элемент составит:

tз ср.= (tз′+tз′′)/2. Экспериментально среднее время задержки удобно определять в цепочке последовательно включенных элементов, число которых должно быть чётным, чтобы число включений оказалось равным числу выключений. Это время можно также определить и с помощью «кольцевого теста». В этом случае чётное число инвертирующих элементов соединяют в кольцо, что создаёт схему генератора импульсов. По частоте генерации может быть вычисленоtз ср.

Потребляемая мощность определяется средним током потребляемым элементом от источника питания. СтатическаяPст= (P0 +P1)/2; полная – в динамическом режиме, зависит от частоты переключения из-за токов в ёмкостных цепях.

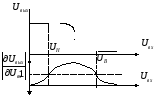

Помехоустойчивость. Различают: статическуюпомехоустойчивость, когда помеха

рассматривается как длительно существующий

уровень потенциала;динамическую

помехоустойчивость, когда помеха

рассматривается как импульс определённой

длительности. Устойчивость элемента к

воздействию длительной помехи меньше,

чем к воздействию кратковременной

помехи при одинаковых их динамических

амплитудах. Поэтому допустимая величина

напряжения помехи, которая ещё не

вызывает сбоев при работе элемента,

зависит от длительности помехи:

Кривая 1 соответствует элементу с меньшим быстродействием, чем 2.

Динамическую помехоустойчивость чётко определить очень трудно. В настоящее время принято оценивать только статическую помехоустойчивость. Величина допустимых статических помех зависит от характеристики «выход-вход» рассматриваемого элемента, т.е. от его амплитудной передаточной характеристики. От логических элементов не требуют точной передачи уровней сигналов. Для кодирования двоичных цифр достаточно получить сигнал; находящийся в довольно широкой зоне отображения нуля или единицы. Чтобы определить допустимую ширину зон отображения двоичных цифр, рассмотрим амплитудную передаточную характеристику инвертора Uвых=f(Uвх). Примем прямое обозначение уровней логических сигналов: «1» ~U1; «0» ~U0– близкой к «0». Для идеального инвертора передаточная характеристика имеет вид:

Эта характеристика является наилучшей, так как даже при значительных отклонениях входных сигналов от номинальных значений U0

и U1выходная

величина сохраняет требуемое значение.

В этом случае ширина зон отображения

нуля и единицы составляет половину

перепада выходного сигнала. В реальных

амплитудных передаточных характеристиках

эти зоны сужаются, т.к. ограничены

напряжениямиUниUв. Такое

ограничение вызвано тем, что для

устойчивой работы сложных логических

цепей требуется, чтобы в зоне отображения

«0» и «1» дифференциальный коэффициент

передачи элементов по напряжению не

достигал единицы. В противном случае

цепи с положительными обратными связями

могут самопроизвольно изменить состояние.

Из-за разброса параметров элементов

схем одного типа амплитудные передаточные

характеристики образуют некоторую

зону, в которой будут лежать все

характеристики.

Здесь можно найти величину допустимых помех, не нарушающих нормальное логическое функционирование элементов. Интервал Uн-U0 maxопределяет помехоустойчивость элемента к положительным помехам. Отрицательная помеха для нулевого входа не опасна. Т.о. максимально допустимая положительная помеха ∆U+= Uн-U0 max, а максимально допустимая отрицательная помеха ∆U-=U1 min-Uв.

Абсолютные значения этих помех нормируют по перепаду напряжения и получают значения относительной помехоустойчивости: A+= ∆U+/(U1-U0),

A-= ∆U-/(U1-U0).

Системы потенциальных элементов на биполярных транзисторах

Классификация:

РТЛ – резисторно-транзисторная логика.

РКТЛ – резисторно-конденсаторная транзисторная логика.

ДТЛ – диодно-транзисторная логика.

ТТЛ – транзисторно-транзисторная логика.

ТЛПТ (ЭСЛ) – транзисторная логика с переключением тока. Основана на принципе коммутации токов, обеспечивающем ей максимальное быстродействие.

ТЛИП – транзисторная логика с инжекционным питанием, рассчитана на реализацию БИС.

Системы элементов РТЛ.

Основой системы элементов РТЛ Iявляется ячейка ИЛИ-НЕ:

На выходе будет «1» только тогда, когда на всех входах «0».

Z=X1+X2+…+Xm(с инверсией). Операция Пирса обладает логической полнотой. Из двух ячеек ИЛИ-НЕ составляют статический триггер:

Собственно триггер собран на Т1и Т2. Для запуска триггера введены два дополнительных Т3и Т4. При подаче «1» на вход Т3он насыщается, и независимо от состояния Т1снижает потенциал точкаадо величиныUк н

что запирает Т2. Транзистор Т4в это время заперт, т.к. сигналы установки одновременно по обоим входам никогда не подаются. При запертых Т2и Т4ток резистораRидёт в цепь базы Т1насыщая его. Теперь снятие сигнала запуска уже не изменит состояния триггера. Главная трудность в реализации схем на РТЛI– это разброс токов (неодинаковых характеристик транзисторов, в разные моменты времени количество включенных транзисторов неодинаково). Для частичного выравнивания токов следует выбиратьR>Rк. Но при этом снижается быстродействие (уменьшается ток базы). На практике обычно выбираютR= (0,1~0,5)Rк

Типовая схема логического элемента РТЛ IIимеет вид:

Если

на всех входах «0», то Tзакрыт. Если на всех входах «1», то Т

обязательно должен быть открыт. Т.е.

схема выполняет операцию порогового

типа:

где Т – положительное число, порог.

При T= 1 элемент выполняет операцию ИЛИ-НЕ, а при Т=mоперацию

И-НЕ. При нечётном числе входов и Т = (m+1)/2 элемент выполняет операцию мажоритирования с инверсией.

Для расчёта статических состояний и переходных характеристик эта схема может быть сведена к схеме обычного инвертора с резисторными цепями управления. Быстродействие элементов РТЛ IIневелико (сильно насыщен транзистор, токи базы малы из-за наличия в цепях базы больших сопротивлений).

Система элементов РКТЛ.

Отличаются от РТЛ наличием конденсаторов, шунтирующих базовые резисторы R. Эти конденсаторы ускоряют переходные процессы в элементах, и позволяют увеличиватьR. Из-за наличияCРКТЛ распространены в гибридных схемах. РКТЛ и РТЛ применяют в устройствах где не требуется высокое быстродействие но желательны малая потребляемая мощность и низкая стоимость.

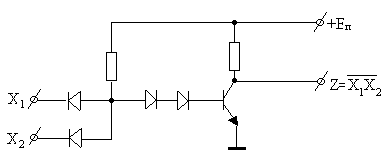

Диодно-транзисторная логика.

Диодно-транзисторная логика имела широкое распространение в середине 60-х годов.

Схема основного логического элемента диодно-транзисторной логики имеет вид:

В последнее время появилась реальная возможность того, что элементы диодно-транзисторной логики снова найдут широкое применение благодаря современной технологии получения так называемых горизонтальных диодов из поликристаллического кремния и поликремниевых резисторов, располагающихся не в поверхностном слое кристалла, а на поверхности окисла. Активные площади диода при этом составляют всего несколько квадратных микрометров, а расположение транзисторов и диодов с резисторами в разных слоях ( одних над другими ) делает элементы весьма компактными. Времена переключения диодов очень малы из-за малых времен жизни не основных носителей. При минимальном технологическом размере 4 мкм возможно получение времени задержки распространения сигнала около 1,5 нс при потреблении мощности в 0,5 мВт и плотности упаковки около 400 элементов на 1 квадратный миллиметр.

В СБИС сегодня применяются элементы диодно-транзисторной логики с диодами Шотки: ( фирма IBM ).

Такие элементы при Кразв.=1, m=3 иСн=0,4 пФ имеют задержки в 2,7 нс.

Базовый элемент ТТЛ.

( Появились в начале 1960-х годов ).

_____Базовым считают элемент с наиболее простой структурой, на основе которого легко создаются другие электронные схемы этого вида микросхем.

С простым инвертором:

_____При рассмотрении работы базового логического элемента И-НЕ сделаем следующие технически оправданные допущения:

- падение напряжения на p-n переходах транзисторов и диодов, смещенных в прямом направлении, т.е. проводящих, неизменно и равно 0,7 В;

- падение напряжения на переходе коллектор-эмиттер насыщенного транзистора пренебрежимо мало;

- напряжение на входе, превышающее 2 В, принято за высокий уровень и считается логической единицей. В действительности Uвх>=2,4 В. Разность 0,4 В называется "шумовым иммунитетом" и характеризует устойчивость логического элемента к внешним помехам;

- напряжение на входе ниже 0,8 В принято за низкий уровень и считается логическим нулем. В действительности Uвх.<=0,4 В. Разность 0,4 В также характеризует помехоустойчивость.

Рассмотрим два случая работы элемента.

1.На все входы элемента И-НЕ подано напряжение высокого уровня. На эмиттерах транзистора Т1 высокое напряжение, на базу через резисторR1 подано напряжениеUп=+5В, а напряжение на коллекторе равно +1,4 В, так какT2 иТ3насыщены. В этих условиях переходы эмиттер-база смещены в обратном направлении, а переход база-коллектор - в прямом, что соответствует инверсному включению транзистора. При таком включении коэффициент усиления по току очень мал. Этим объясняется тот факт, что ток, протекающий через каждый вход невелик, не превышает 40 мкА и обычно равен 10 мкА. Через переход база-коллектор транзистораТ1 протекает ток:

который является базовым током Т2. Такого тока достаточно для насыщения транзистораТ2. Напряжение на коллектореТ2при этом будет +0,7 В. Оно запирает транзисторТ4, причем для большей гарантии добавлен диод Д. Таким образом выходной ток логического элемента равен коллекторному току открытого транзистораТ3. Для элементов с обычной нагрузочной способностью максимальный выходной токI0вых=16 mA. В рассмотренном случае входной и выходной токи "втекают" в логический элемент.

2. На один из входов или на все входы элемента И-НЕ подано напряжение низкого уровня.

Теперь транзистор Т1 включен нормально. Один из его эмиттеров (Б) имеет более низкий потенциал, чем потенциал базы. Переход база-эмиттер смещен в прямом направлении. Ток этого эмиттера является в сущности входным. Его значение определяется сопротивлением резистораR1и не превышает 1,6 мА. ТранзисторыT2иТ3заперты, т.к. переход база-коллекторТ1смещен в обратном направлении. Резистор утечкиR3предохраняет транзисторТ3от отпирания начальным током транзистораТ2. Протекающим через резисторR2током отпирается транзисторТ4но при этом не насыщается. ЕслиI1вых<=2,3 mA, выходное напряжение высокого уровняU1вых>2,4 В, т.е. превышает минимальное допустимое. Итак, в этом случаеIвх. max=1,6 mA, Iвых max=2,3 mA, причем входной и выходной токи "вытекают" из логического элемента._____ТранзисторыТ2, Т3иТ4образуют так называемый сложной инвертор. В каждом состоянии элемента один из двух выходных транзисторов –Т3илиТ4- отперт. Благодаря этому выходное сопротивление логического элемента в обоих состояниях достаточно мало. Тем самым обеспечивается быстрый заряд и разряд паразитных емкостей, которые могут быть на выходе. Следовательно, обеспечивается высокое быстродействие и возможность подключения к выходу до 10 входов от микросхем той же серии. Во время переключения транзисторовТ3иТ4из одного состояния в другое ток, потребляемый логическим элементом от источника питания, резко возрастает.

Причина в том, что при

переключениях оба транзистора в течении

весьма короткого времени бывают отперты

одновременно и ток в цепи питания

ограничен только резистором R4.

Помимо роста потребления энергии

возможно появление помех в шинах питания.

Поэтому в цепи питания рекомендуется

применять фильтры: конденсаторы емкостью

0,01-0,10 мкФ с малой индуктивностью вводов,

подключаемые непосредственно между

шиной питания и общей шиной.

Вблизи разъема ставится конденсатор >=0,1 мкФ на каждую микросхему, а по площади платы на 5-10 микросхем >=0,002 мкФ на каждую микросхему.

Если в логическом элементе И-НЕ задействованы не все входы, то на неиспользуемых входах надо поддерживать напряжение высокого уровня, оставлять входы свободными нежелательно. Хотя открытые входы ТТЛ-элемента ведут себя подобно входам, на которые подано напряжение высокого уровня, пользоваться этим обстоятельством не следует, так как растет вероятность воздействия различных помех, т.е. снижается помехоустойчивость схемы. Обыкновенно неиспользуемые входы подключают через резистор R=1,0-3,3 кОм к шине питания. В этом случае допускается объединять до 10 входов. До 30 входов можно объединять в схеме со стабилитроном.

Можно также соединять эти входы с действующими, соблюдая нормы нагрузки выхода предыдущего каскада, либо с выходом отдельного логического элемента И-НЕ, входы которого заземлены - так называемого генератора логической еденицы.

_____В элементах транзисторно-транзисторной логики Шотки (ТТЛШ), в отличие от элементов ТТЛ, вместо обычных транзисторов используются транзисторы Шотки, в которых параллельно коллекторному переходу включен диод Шотки, что приводит к исключению режима насыщения открытого транзистора и тем самым к ускорению его запирания, а значит к увеличению быстродействия. По быстродействию ТТЛШ вышли на второе место после элементов типа ЭСЛ. Схема базового элемента ТТЛШ:

Особенность транзисторов Шотки,связанная с отсутствием у них режима насыщения - повышенное значение напряжения на открытом транзисторе ( около 0,3 В ).

Элементы эмиттерно-связанной логики.

Элементы ЭСЛ - наиболее быстродействующие из изготавливаемых на основе кремния. Эти элементы строятся на токовых ключах следующего вида: (ТЛПТ)

Ток Iэ=constпод воздействием входного сигнала Х переключается в одно из плеч цепи. На базу транзистораТ2подается постоянное опорное напряжениеUоп, а напряжение на базе транзистораТ1выше опорного при X=1 и ниже, если X=0, т.е. уровни напряженийU1вхиU0вхзнакопеременны относительноUопи расположены симметрично относительно него. Связанные через общую точку эмиттеров транзисторыТ1иТ2влияют друг на друга - увеличение тока одного из них ведет к уменьшению тока другого. Для практически полного переключения тока из одного плеча в другое достаточно перепада входного сигнала

U1вх-U2вх=2Uоколо 350 - 400 мВ. Для обеспечения необходимой помехоустойчивости элементов и уменьшения влияния изменений температуры на режим схемы перепад входного напряжения несколько увеличивают, но и в этом случае он остается в пределах долей вольта.

Быстродействие токового ключа очень велико:

- в транзисторах отсутствует режим н+асыщения;

- перепады напряжений малы; - в связи с небольшими перепадами выходного напряжения может быть мало сопротивление Rk, что уменьшает постоянные времени перезаряда нагрузочных емкостей.

По абсолютным значениям уровни выходных сигналов отличаются смещением в сторону "плюса" ( без этого нельзя осуществить ненасыщенный режим работы транзисторов ). Следовательно, невозможно непосредственное каскадирование этих схем. Для снижения уровней выходных сигналов и приведения их к уровням входных сигналов используются эмиттерные повторители, что вместе с тем обеспечивает малые выходные сопротивления, позволяющие быстро перезаряжать нагрузочные емкости.

Базовый логический элемент ЭСЛ образуется при замене входного транзистора T1токового ключа группой параллельно включенных транзисторов. Источник опорного напряжения состоит из делителяR3иR6и эмиттерного повторителя наТ4. ДиодыД1иД2обеспечивают температурную компенсацию уходов параметров схемы.

Иногда ( серия К500 ) входы схемы соединены компактными высокоомными резисторами (R=50 к) с источником питания, что позволяет не подключать неиспользуемые входы элемента к каким-либо внешним потенциалам. Если данный вход используется, то влияние на его режим резистора R очень мало из-за высокоомности резистора. Сопротивления, входящие в схемы выходных эмиттерных повторителей сделаны внешними, чтобы уменьшить рассеяние мощности в корпусе микросхемы и иметь различные варианты реализации выходных цепей. Обычно R7=R8=(0,32) k.При передаче сигнала по согласованным по волновому сопротивлению линиям, когда требуется малое выходное сопротивление схемы,R7=R8=(50100) Ом и чтобы не создавался недопустимо большой ток выходного эмиттерного повторителя, это сопротивление подключается к пониженному напряжению (-2В). Цепь общей точки для логической части схемы и выходных эмиттерных повторителей во избежание помех со стороны последних выполняются раздельно, что условно показано на рисунке. Приведенная схема выполняет операцию ИЛИ-НЕ и ИЛИ, что повышает ее функциональную гибкость._____Быстродействие и энергия переключения логических элементов улучшается с уменьшением логического перепада и напряжения питания. Это достигается в элементах ЭСЛ путем исключения выходных эмиттерных повторителей. При этом нарушается согласованность потенциалов и транзисторы входят в насыщение, но при малых логических перепадах степень насыщения мала и не оказывает существенного влияния на переходные процессы и в целом быстродействие повышается. Из-за малого логического перепада малосигнальные элементы (МЭСЛ) имеют низкую помехоустойчивость, а из-за отсутствия эмиттерных повторителей - пониженные коэффициенты разветвления. Все это затрудняет их использование, но внутри БИС создаются условия, когда применение МЭСЛ возможно и целесообразно._____Одно из достоинств элементов ЭСЛ - постоянство потребляемого тока ( токи в цепях не прерываются, а лишь коммутируются из одной ветви в другую).