Шины.PCI,.USB.и.FireWire

.pdf

ства: памяти, ввода/вывода, конфигурационное и сообщений. Новое (по сравне$ нию с PCI) пространство сообщений (Message Space) используется для передачи в виде пакетов «внеполосных» сигналов PCI: прерываний по линиям INTx, управле$ ния потреблением и т. п. Таким образом реализуются «виртуальные провода». Порт PCI Express содержит передатчик, приемник и узлы, необходимые для сборки$раз$ борки пакетов.

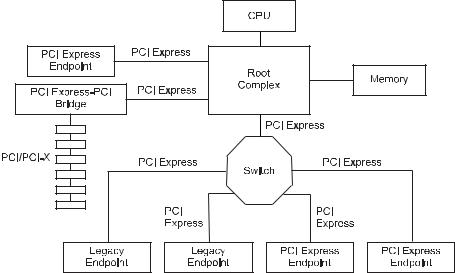

Пример топологии средств ввода/вывода, иллюстрирующий архитектуру PCI Express, приведен на рис. 8.1. Центральным элементом архитектуры является кор невой комплекс (Root Comlex), соединяющий иерархию ввода/вывода с центром — процессором (одним или несколькими) и памятью. Корневой комплекс может иметь один и более портов PCI Express, каждый из них определяет свой домен иерар хии (hierarchy domain). Каждый домен состоит из одной конечной точки (Endpoint) или суб иерархии — нескольких конечных точек, связанных коммутаторами. Воз$ можность непосредственных равноранговых коммуникаций между элементами разных доменов обязательной не является, но может присутствовать в конкрет$ ных реализациях. Для обеспечения прозрачных равноранговых коммуникаций в корневом комплексе должны присутствовать коммутаторы. Возможность взаи$ модействия центрального процессора с любым устройством любого домена безус$ ловна, как и возможность обращения любого устройства к памяти. Корневой ком$ плекс должен генерировать запросы к конфигурационному пространству — его роль аналогична главному мосту PCI. Корневой комплекс может генерировать запросы ввода/вывода как запросчик; он может генерировать и блокированные (Locked) запросы, требующие непрерываемого исполнения. Корневой комплекс не должен поддерживать блокированные запросы как исполнитель (Completer) — это предот$ вращает «заклинивание» ввода/вывода.

Рис. 8.1. Топология «фабрики» PCI Express

Конечная точка (Endpoint) — это устройство, способное инициировать и/или исполнять транзакции PCI Express от своего имени или от имени устройства не$PCI Express (например, хост контролера USB). Конечная точка должна быть видима в одном из доменов иерархии. Конечная точка должна иметь заголовок конфигурационного пространства типа 0 (см. главу 5) и отвечать как исполнитель на конфигурационные запросы. В качестве механизма сигнализации прерываний все конечные точки используют MSI. В PCI Express рассматриваются два типа конечных точек: «наследники» (Legacy) и новые точки, построенные по идеоло$ гии PCI Express. К «наследным» точкам имеется ряд послаблений:

в плане адресации памяти они могут и не поддерживать более 4 Гбайт;

ввод/вывод может не быть абсолютно перемещаемым (из пространства ввода/ вывода в пространство памяти) с помощью регистров базового адреса (BAR), так что могут потребоваться транзакции обращения к пространству ввода/вывода (транзакции к памяти предпочтительнее);

диапазон занимаемых адресов может быть менее 128 байт (требования к грани$ цам были жестко сформированы в PCI$X);

конфигурационное пространство может не быть расширенным (оставаться в пределах 256 байт);

программная модель может требовать использования блокированных запросов к устройству (но не от него).

Коммутатор (Switch) имеет несколько портов PCI Express. Логически он пред$ ставляет собой несколько виртуальных мостов PCI$PCI, соединяющих порты ком$ мутатора со своей внутренней локальной шиной. Виртуальный мост PCI описы$ вается конфигурационными регистрами с заголовком типа 1 (см. главу 5). Порт, ведущий к вершине иерархии, называется восходящим (upstream port) — через него коммутатор конфигурируется как набор мостов PCI. Коммутатор транслирует между портами пакеты всех типов, основываясь на адресной информации, акту$ альной для пакета данного типа. Коммутатор не распространяет блокированные запросы со своих нисходящих портов. Арбитраж между портами коммутатора мо$ жет учитывать виртуальные каналы и, соответственно, взвешенно распределять пропускную способность. Коммутатор не имеет права разбивать пакеты на более мелкие (аналог этого права имеется в мостах PCI).

Мост PCI Express–PCI соединяет иерархию шин PCI/PCI$X с «фабрикой» ввода/ вывода — корневым комплексом или коммутаторами PCI Express.

Конфигурирование «фабрики» осуществляется либо со 100% совместимостью с конфигурационным механизмом PCI 2.3, либо с использованием расширенного конфигурационного пространства PCI$X. Каждое соединение PCI Express с помощью виртуальных мостов отображается в виде логической шины PCI со своим номером. Логические устройства отображаются в конфигурационном пространстве как устройства PCI, каждое из которых может иметь 1–8 функций со своим набором конфигурационных регистров.

Архитектурная модель PCI Express

Архитектура PCI Express разделена на три уровня:

уровень транзакций (Transaction Layer) — верний уровень архитектуры, отве$ чающий за сборку и разборку транзакционных пакетов TLP (Transaction Layer Packets). Эти пакеты используются для транзакций чтения и записи, а также сообщения о событиях некоторых типов. Каждый пакет TLP имеет уникальный идентификатор, который позволяет направить ответный пакет его отправите$ лю. В TLP используются различные форматы адресации, зависящие от типов транзакций. Пакет может иметь атрибуты отмены слежения за когерентностью NS (No Snoop) и «расслабленной» упорядоченности RO (Relaxed Ordering). Каж$ дая транзакция, требующая ответа, выполняется в виде расщепленной (см. PCI$X в главе 2). Уровень транзакций отвечает и за управление потоком, реализован$ ное на основе механизма кредитов;

канальный уровень (Data Link Layer), промежуточный в стеке, первым делом отвечает за управление связью, обнаружение ошибок и организации повторных передач, до успеха или признания отказа соединения. К пакетам, полученным от уровня транзакций, канальный уровень добавляет номера пакетов и конт$ рольные коды. Канальный уровень и сам является генератором и получателем пакетов DLLP (Data Link Layer Packet), используемых для управления соеди$ нением;

физический уровень изолирует канальный от всех подробностей передачи сиг$ налов. Он состоит из двух субблоков. Логический субблок при передаче выпол$ няет распределение данных по линиям, скремблирование, кодирование по схеме 8B/10B, кадрирование и преобразование в последовательный код. При приеме выполняются обратные действия. Дополнительные символы, обеспечиваемые кодированием 8B/10B, используются для служебной сигнализации. Логичес$ кий субблок отвечает и за согласование соединения, инициализацию и т. п. Элек трический субблок отвечает за электрическое согласование, синхронизацию, обнаружение приемника. Уровневая модель, принятая в PCI Express, позволя$ ет, не затрагивая остальных уровней, заменить физический уровень или его субблоки, когда появятся более эффективные схемы кодирования и сигнализа$ ции. Интерфейс между физическим и канальным уровнем зависит от реализа$ ции этих компонентов и выбирается их разработчиком. Интерфейс физическо$ го уровня четко специфицирован, что обеспечивает возможность соединения устройств разного происхождения. Для тестирования на соответствие электри$ ческим параметрам достаточно подключить устройство PCI Express к специаль$ ному тестеру.

Программная совместимость с PCI/PCI X

Программная модель PCI Express совместима с PCI в следующих аспектах:

обнаружение, нумерация и конфигурирование устройств PCI Express выпол$ няются тем же конфигурационным ПО, что используется в PCI (PCI$X 2.0);

существующие ОС загружаются без каких$либо модификаций;

драйверы существующих устройств поддерживаются без каких$либо модифи$ каций;

конфигурирование и разрешение новых функциональных возможностей PCI Express выполняется по общей идее конфигурирования устройств PCI.

Качество обслуживания и виртуальные каналы

В PCI Express имеется поддержка дифференцированных классов по качеству об служивания (QoS), обеспечивающая следующие возможности:

выделять ресурсы соединения для потока каждого класса (виртуальные кана$ лы);

конфигурировать политику по QoS для каждого компонента;

указывать QoS для каждого пакета;

создавать изохронные соединения.

Для поддержки QoS применяется маркировка трафика: каждый пакет TLP имеет трехбитное поле метки класса трафика TC (Traffic Class). Это позволяет разли$ чать передаваемые данные по типам, создавать дифференцированные условия пе$ редачи трафика для разных классов. Порядок исполнения транзакций соблюдается в пределах одного класса, но не между разными классами. Для дифференцирова$ ния условий передачи трафика разных классов в коммутирующих элементах PCI Express могут создаваться виртуальные каналы. Виртуальный канал VC (Virtual Channel) представляет собой физически обособленные наборы буферов и средств маршрутизации пакетов, которые загружаются только обработкой трафика своего виртуального канала. На основе номеров виртуальных каналов и их приоритетов производится арбитраж при маршрутизации входящих пакетов. Каждый порт, поддерживающий виртуальные каналы, выполняет отображение пакетов опреде$ ленных классов на соответствующие виртуальные каналы. При этом на один ка$ нал может отображаться произвольное число классов. По умолчанию весь трафик маркируется нулевым классом (TC0) и передается дежурным каналом (VC0). Вир$ туальные каналы вводятся по мере необходимости.

Сигнализация прерываний и управление энергопотреблением

Основной метод сигнализации прерываний в PCI Express — с помощью передачи сообщений (MSI), причем с 64$битной адресацией (32$битная разрешена только для «наследных» устройств). Однако ради обеспечения программной совмести$ мости устройство может использовать и эмуляцию прерываний через INTx#, пере$ давая эти запросы с помощью специальных пакетов. Получателем пакетов сигна$ лизации прерываний, как MSI, так и эмуляции INTx#, как правило, является контроллер прерываний, расположенный в корневом комплексе. Сигнализация

INTx# производится пакетами класса TC0. Прерывания MSI при использовании виртуальных каналов должны использовать класс трафика, соответствующий клас$ су трафика данных, к которым относятся данные прерывания. Иначе возможно нарушение синхронизации из$за относительной неупорядоченности трафика раз$ ных классов. Синхронизации можно добиваться и теми же средствами, что и в PCI/ PCI$X — чтением (пусть даже нулевой длины) через коммутатор (мост). Такой прием неизбежен, если прерывания относятся к данным нескольких разных клас$ сов (виртуальных каналов).

Сигнализация событий управления энергопотреблением возможна в двух вариан$ тах: пакетная эмуляция сигнала PME# (аналогично эмуляции INTx#) и естественная сигнализация PCI Express с помощью соответствующих сообщений. При эмуля$ ции PME# идентификация источника сигнала выполняется последовательным чте$ нием конфигурационных регистров устройств, способных генерировать этот сигнал. Естественная сигнализация гораздо удобнее: идентификатор устройства$источника присутствует в сообщении.

Расширенное управление потреблением и бюджетом мощности (PM — power mana$ gement) означает:

возможность идентификации способностей к PM каждой функции;

возможность перевода функции в указанное состояние потребления;

возможность получения информации о текущем состоянии потребления функ$ ции;

возможность генерации запроса пробуждения при выключенном основном пи$ тании;

возможность последовательного включения устройств.

«Горячее» подключение

«Горячее» подключение и замена устройств могут выполняться с использованием как существующих механизмов (PCI Hot$Plug и Hot$Swap, см. главу 6), так и есте$ ственных для PCI Express, не требующих дополнительных сигналов. Стандартная модель горячего подключения оперирует следующими элементами:

индикатор питания слота, запрещающий извлечение/установку карты (мига$ ние указывает на процесс перехода в обесточенное состояние);

индикатор внимания, указывающий на проблемы, связанные с устройством в данном слоте (мигание индикатора используется для поиска нужного слота);

ручной фиксатор карты;

датчик состояния ручного фиксатора, позволяющий системному ПО обнару$ жить открытый замок;

электромеханическая блокировка, не позволяющая извлекать карту при вклю$ ченном питании. Специального сигнала для управления блокировкой не пре$ дусмотрено; если блокировка имеется, то она должна срабатывать прямо от питания порта;

кнопка Внимание (Attention) для запроса операции «горячего» подключения;

программный интерфейс пользователя, позволяющий запросить «горячее» под$ ключение;

система нумерации слотов, позволяющая визуально определить требуемый слот.

Надежность передачи и целостность данных

Для обеспечения надежности транзакций и целостности данных применяется CRC$контроль всех транзакций и управляющих пакетов. Запросчик считает тран$ закцию выполненной по получении подтверждающего сообщения от исполнителя (подтверждение отсутствует только для записей, отправленных в основную па$ мять). Обработка ошибок в минимальном варианте аналогична PCI, причем обна$ руженные ошибки отображаются в конфигурационных регистрах функций (в ре$ гистре состояния). Расширенные возможности сообщения об ошибках дают исходную информацию для развитых процедур изоляции отказов и восстановле$ ния, а также мониторинга и регистрации (logging) ошибок. Ошибки делятся на три группы, что позволяет использовать адекватные процедуры восстановления:

исправимые (correctable) ошибки — автоматически вызывающие аппаратную процедуру восстановления (повтора) и не требующие программного вмешатель$ ства для нормального исполнения транзакции;

неисправимые фатальные (Fatal) ошибки — требующие для надежного возоб$ новления работы выполнения сброса, в результате которого могут пострадать транзакции, не имеющие прямого отношения к ошибке;

неисправимые не фатальные (Non$fatal) ошибки — не требующие сброса для возобновления работы. В результате этих ошибок могут быть потеряны лишь несколько транзакций, затронутых ошибкой.

Верхние уровни архитектуры PCI Express

Два верхних уровня — канальный и уровень транзакций — определяют основные функциональные возможности взаимодействия компонентов в системе.

Транзакции и форматы пакетов

Весь трафик в PCI Express оформлен в виде пакетов, из которых прикладной инте$ рес представляют пакеты уровня транзакций — TLP. Каждый пакет TLP начина$ ется с заголовка, за которым может следовать поле данных и, дополнительно, поле «дайджеста» (Digest) — 32$битного CRC$кода. Длина всего пакета перечисленных полей кратна двойному слову (DW, 32 бит). Заголовок пакета содержит следую$ щие обязательные поля:

поле формата Fmt[1:0], задающее вид пакета: бит 0 — длина заголовка (0 —3 DW, 1 — 4 DW), бит 1 — присутствие поля данных (0 — нет данных);

поле типа Type[4:0], определяющее назначение пакета (тип транзакции, табл. 8.1);

поле класса трафика TC[2:0];

признак «дайджеста» TD: единичное значение указывает на применение 32$бит$ ного CRC$кода в конце пакета, защищающего все поля пакета, не изменяемые в процессе его путешествия через коммутаторы PCI Express. Этот дополнитель$ ный контроль применяют для особо важных случаев; для обычных транзакций ограничиваются CRC$контролем канального уровня;

признак ошибки данных EP, которым сообщается, что при чтении передаваемых данных произошла ошибка и данные могут быть недействительными (poisoned data);

длина поля данных Length[9:0] (количество двойных слов, 000…01 — 1, 111…111 —1023 DW, 000…000 — 1024 DW.

Таблица 8.1. Пакеты транзакций PCI Express

Мнемоника |

Fmt |

Type |

Назначение |

|

[1:0] |

[4:0] |

|

|

|

|

|

MRd |

00 |

0 0000 |

Memory Read Request, запрос чтения памяти |

|

01 |

|

|

MRdLk |

00 |

0 0001 |

Memory Read Request Locked, запрос блокированного |

|

01 |

|

чтения памяти |

MWr |

10 |

0 0000 |

Memory Write Request, запрос записи в память (с данными) |

|

11 |

|

|

IORd |

00 |

0 0010 |

I/O Read Request, запрос чтения ввода/вывода |

IOWr |

10 |

0 0010 |

I/O Write Request, запрос записи ввода/вывода |

|

|

|

(с данными) |

CfgRd0 |

00 |

0 0100 |

Configuration Read Type 0, конфигурационное чтение типа 0 |

CfgWr0 |

10 |

0 0100 |

Configuration Write Type 0, конфигурационная запись типа 0 |

CfgRd1 |

00 |

0 0101 |

Configuration Read Type 1, конфигурационное чтение типа 1 |

CfgWr1 |

10 |

0 0101 |

Configuration Write Type 1, конфигурационная запись типа 1 |

Msg |

01 |

1 0 rrr |

Message Request, запрос сообщения без данных, |

|

|

|

rrr определяет механизм маршрутизации |

MsgD |

11 |

1 0 rrr |

Message Request with data payload, запрос сообщения |

|

|

|

с данными, rrr определяет механизм маршрутизации |

Cpl |

00 |

0 1010 |

Completion without Data, завершение без данных, |

|

|

|

используется в ответ на IOWr и CfgWr, а также при |

|

|

|

завершении любого блокированного чтения с ошибкой |

CplD |

10 |

0 1010 |

Completion with Data, завершение с данными, |

|

|

|

используется в ответ на запросы чтения |

CplLk |

00 |

0 1011 |

Completion for Locked Memory Read without Data, |

|

|

|

ошибочное завершение блокированного чтения памяти |

CplDLk |

10 |

0 1011 |

Completion for Locked Memory Read, завершение |

|

|

|

блокированного чтения памяти |

|

|

|

|

Идентификатором транзакции является идентификатор устройства$запросчика в совокупности с 8$битным тегом; дескриптор транзакции содержит еще и атрибу$ ты транзакции (RO и NS), а также класс трафика TC. Тег используется только для транзакций, требующих пакета завершения. По умолчанию запросчик может дер$ жать незавершенными до 32 транзакций, так что из 8$битного тега используются лишь 5 бит. Однако можно разрешить и расширенное использование тега, когда будут использоваться все 8 бит (до 256 незавершенных запросов).

В зависимости от типа транзакций в пакетах применяются различные форматы адреса и маршрутизации. Адрес задается с точностью до выровненного двойного слова (биты [1:0] = 00). Для всех транзакций, несущих данные (кроме сообщений), один из байтов заголовка несет битовые признаки действительности байтов в пер$ вом и последнем двойном слове поля данных (в середине подразумевается дей$ ствительность всех байтов). Таким образом пакет может нести произвольное чис$ ло смежных байтов, начиная с произвольного адреса.

Транзакции с памятью могут быть как с коротким (32$битным), так и с длинным (64$битным) адресом. Сочетания адреса и длины транзакции не должны вызывать пересечение границы 4$килобайтных страниц. Транзакции записи в память вы$ полняются как отправленные (posted write), на них не требуется ответа.

Транзакции ввода/вывода сохранены в PCI Express для совместимости с PCI/PCI$ X и старым ПО; от этого типа транзакций планируется избавиться. В этих транзакциях используется 32$битный адрес и передается лишь одно двойное сло$ во данных.

Конфигурационные транзакции адресуются и маршрутизируются по идентифика$ тору устройства; в этих транзакциях используется 32$битный адрес и передается лишь одно двойное слово данных. Идентификатор устройства имеет формат, ис$ пользуемый для PCI: 8$битное поле номера шины, 5$битное поле номера устрой ства и 3$битное поле номера функции.

Транзакции сообщений маршрутизируются в зависимости от поля rrr: 000 — к корневому комплексу, 001 — по адресу, 010 — по идентификатору, 011 — широ$ ковещание от корневого комплекса, 100 — локальное сообщение (не идет дальше приемника), 101 — собираются и маршрутизируются к корневому комплексу. В сообщении один байт отводится под код сообщения, и ряд сообщений обходится без поля данных. Сообщения с rrr = 100 только изменяют состояние приемника (так, например, реализуются нижеописанные виртуальные провода INTx#). Вари$ ант маршрутизации с rrr = 101 используются для одного из типов сообщений уп$ равления потреблением: коммутатор пошлет такое сообщение на восходящий порт, только получив их со всех нисходящих портов. Сообщения используются для эму$ ляции проводных прерываний, оповещения о событиях управления энергопотреб$ лением и ошибках, а также для коммуникаций между устройствами.

Для эмуляции прерываний по INTx# (четырех виртуальных проводов) используют$ ся 8 кодов сообщений (по четыре на установку и по четыре на снятие каждого сигнала). Коммутаторы (и корневой комплекс) должны отслеживать состояние виртуальных проводов на каждом из нисходящих портов, учитывая приходы сообщений от соответствующих устройств (циклическое чередование четырех

линий INTx#, как в PCI, сохраняется). В соответствии с этими состояниями по функ$ ции ИЛИ формируется состояние виртуальных проводов восходящего порта, и по изменению состояний генерируются соответствующие сообщения. Для эмуляции разделяемых прерываний сообщение на установку запроса передается на восходя$ щий порт по приходу первого (для данного провода) сообщения установки от нис$ ходящего порта. Если до прихода сообщения о снятии запроса для того же провода придет сообщение об установке запроса от другого порта, то это сообщение на вос$ ходящий порт не транслируется. Сообщение о снятии запроса будет послано на восходящий порт только по получении сообщений о снятии запросов для данного провода со всех нисходящих портов, ранее сообщивших об установке запроса. Кор$ невой комплекс выполняет аналогичные задачи и, наконец, доводит виртуальные сиг$ налы до реального контроллера прерываний. Таким образом, пакеты сообщений по$ зволяют «объединить» виртуальные провода INTx# устройств всех логических шин.

Передача пакетов и пропускная способность соединения

Пакеты TLP, с помощью которых выполняются транзакции, поступают на каналь$ ный уровень. Основная задача канального уровня — обеспечить надежную достав$ ку пакетов TLP. Для этого канальный уровень при передаче обрамляет пакет TLP своим заголовком, содержащим 12$битный последовательный номер TLP, и 32$бит$ ным полем LCRC (CRC канального уровня). Таким образом, канальный уровень к каждому пакету TLP добавляет 6 байт накладных расходов. На каждый пакет TPL передатчик должен получить положительное подтверждение Ack — пакет каналь$ ного уровня DLLP (Data Link Layer Packet). Если подтверждение не приходит, то механизм тайм$аута заставляет передатчик повторить посылку пакета. Предусмот$ рен и пакет отрицательного подтверждения Nak, вызывающий повторную пере$ дачу без ожидания.

Пакеты DLLP имеют длину 6 байт: 4$байтная информационная часть и 16$битный CRC$код. Кроме подтверждений TLP пакеты DLLP используются для управле$ ния потоком, а также для управления энергопотреблением связи.

Физический уровень вводит свое обрамление передаваемых пакетов: перед нача$ лом пакета передается специальный символ STP (для TLP$пакета) или SDP (для DLLP$пакета), после пакета — символ END. Эти специальные символы отличают$ ся от символов, представляющих данные после кодирования 8B/10B.

Рассмотрев структуры пакетов, можно оценить «скорострельность» базового со$ единения PCI Express (разрядность 1 бит, скорость 2,5 Гбит/с). Возьмем самую короткую транзакцию — запись двойного слова в пространство ввода/вывода. Со$ ответствующий пакет TLP имеет длину 4 DW (3DW заголовок и 1 DW данных) — 16 байт; на канальном уровне к нему добавится 6 байт, так что на кодирование 8B/ 10B поступит 22 восьмибитных символа. К ним добавятся еще 2 символа обрамле$ ния физического уровня — итого 24. В линию будет передано 24×10 = 240 бит, что при скорости 2,5 Гбит/с займет 96 нс канала прямого направления. Вспомним, что

транзакция записи в порт требует подтверждения — встречного пакета TLP дли$ ной 3DW, который после канального и физического обрамлений вырастет до 20 символов — 200 бит, занимающие 80 нс встречного канала. Теперь учтем ка$ нальные пакеты подтверждений приема каждого TPL (6$байтные Ack) — с физи$ ческим обрамлением по 8 символов (80 бит). Они в каждом канале займут по 32 нс. Итак, в прямом канале транзакций записи в порт занимает 96 + 32 = 128 нс (0,128 мкс), в обратном — 80 + 32 = 112 нс. Если подсчитать максимальную ско$ рость передачи данных при непрерывных записях в порт, получаем V = 4/0,128 = = 31,25 Мбайт/с. При этом будет занят и встречный канал с коэффициентом заг$ рузки 112/128 = 0,875. Результат по скорости близок к возможностям стандарт$ ной шины PCI (32 бит/33 МГц), в которой такая транзакция потребует четырех тактов шины. Чтение ввода/вывода на PCI Express даст те же результаты (на PCI результат будет хуже из$за «лишнего» такта на «пируэт»).

Теперь возьмем самый выгодный (в состязаниях по производительности) вариант транзакции: запись в память пакета 1024 двойных слов (с короткой 32$битной ад$ ресацией). Для этого требуется лишь один пакет TPL (транзакция завершения не требуется) длиной (3 + 1024) двойных слова = 4108 байт. К нему на канальном и физическом уровнях добавится 6 + 2 = 8 символов, что составит 4116×10 =

= 41160 бит ≈ 16,5 мкс. При этом скорость передачи данных составляет 4096/16,5 ≈

≈248 Мбайт/с — это уже уровень производительности PCI 32/66 МГц при длин$ ных пакетных передачах. Загрузка встречного канала подтверждениями каналь$ ного уровня в этом случае пренебрежимо мала. Скорость чтения из памяти будет немного ниже, поскольку каждая транзакция чтения состоит из двух пакетов TLP — запроса чтения (3 или 4 двойных слова) и пакета завершения с данными дли$ ной (3 + N) двойных слова. При большой длине пакета относительная доля допол$ нительных трех DW будет невеликой.

Если встречный канал удается загрузить полезным трафиком, то можно говорить об удвоении пропускной способности PCI Express за счет возможности работы

вполном дуплексе. Однако в примере с записью в порт ввода/вывода о таком уд$ воении речи быть не может, поскольку встречный канал загружен довольно плот$ но. Если пересчитать полезную скорость на один сигнальный контакт разъема, то

всамом выгодном полнодуплексном варианте получим 248×2/4 = 124 Мбайт/с на контакт. Для сравнения можно взять вариант PCI$X533, обеспечивающий пико$ вую скорость записи, приближающуюся к 533×4 = 2132 Мбайт/с. В операциях чте$ ния памяти PCI$X выглядит гораздо скромнее — пиковая скорость всего 533 Мбайт/с. При этом используется около 50 сигнальных контактов (не считая многочислен$ ных земляных), так что на каждый контакт приходится примерно по 10–40 Мбайт/с. В порте AGP при той же пиковой скорости сигналов еще больше, так что заявле$ ния о высокой эффективности использования контактов в PCI Express имеют под собой основу. Полный дуплекс ни в PCI/PCI$X, ни в AGP невозможен.

Напомним, что данные подсчеты производились для базового соединения (x1, 1 ли$ ния); увеличив число линий до 32 бит (x32), можно получить максимальную ско$ рость записи в память 248×32 = 7936 Мбайт/с. А если брать полную загрузку полно$ дуплексного соединения, то PCI Express может обеспечить суммарную пропускную