Шины.PCI,.USB.и.FireWire

.pdfПри этом пропускная способность BW = N×Y/T, интервал T принят 1 мкс. Размер блока V может принимать значение 32, 64, 128 или 256 байт; для транзакций чте$ ния, длина которых может принимать те же значения, изохронный блок передает$ ся за одну транзакцию. Длина транзакций записи может быть 32 или 64 байт, так что один блок будет передаваться за 1, 2 или 4 транзакции. В зависимости от мощности подсистемы памяти порт AGP может выдерживать изохронный трафик, достаточный для различных применений:

видеозахват (в настольных ПК): 128 Мбайт/с, N = 2, L = 2, Y = 64;

видеоредактирование: 320 Мбайт/с, N = 5, L = 2, Y = 64;

поток 1 канала HDTV: 384 Мбайт/с, N = 3, L = 10, Y = 128;

поток 2 каналов HDTV (в мощных рабочих станциях): 640 Мбайт/с, N = 5, L = 10, Y = 128.

Новые команды AGP для изохронных транзакций включают:

ISOCH Read (0011) — изохронное чтение, в поле LLL — код длины: 000 — 32 байт, 001 — 64, 010 — 128, 011 — 256 байт;

ISOCH Write/Unfenced (0110) — изохронная запись с беспорядочным заверше$ нием, в поле LLL — код длины: 000 — 32 байта, 001 — 64 байт;

ISOCH Write/Fenced (0111) — изохронная запись с упорядочным завершением, в поле LLL — код длины: 000 — 32 байта, 001 — 64 байт;

ISOCH Align (1110) — чтение временного сдвига относительно изохронного пе$ риода.

Новые коды состояния порта AGP включают:

100 — чтение изохронных данных;

101 — запись изохронных данных.

Конфигурационные регистры AGP

Конфигурирование устройств с интерфейсом AGP выполняется так же, как и обыч$ ных устройств PCI, — через обращения к регистрам конфигурационного простран$ ства (см. главу 5). При этом карты AGP не требуют внешней линии IDSEL — у них внутренний сигнал разрешения доступа к конфигурационным регистрам соеди$ нен с линией AD16, так что обращение к конфигурационным регистрам AGP обес$ печивается при AD16 = 1.

В процессе инициализации процедура POST только распределяет системные ре$ сурсы, но операции AGP оставляет запрещенными. Работу AGP разрешает загру$ женная ОС, предварительно установив требуемые параметры AGP: режим обмена, поддержку быстрой записи, адресации свыше 4 Гбайт, способ подачи и допусти$ мое число запросов. Для этого параметры устройств считываются из регистра состо$ яния AGP, а согласованные параметры записываются в регистр команд AGP, распо$ ложенный в конфигурационном пространстве. Параметры настройки порта задаются через конфигурационные регистры чипсета системной платы (главного моста).

В конфигурировании системы с AGP фигурируют две функции со своими конфи$ гурационными пространствами:

собственно порт AGP (Core Logic), являющийся целевым устройством в тран$ закциях AGP;

графический адаптер, являющийся инициатором транзакций AGP.

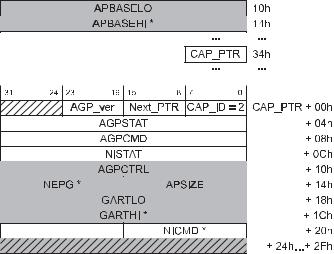

Их специфические конфигурационные регистры (рис. 7.4) частично совпадают по назначению; серым цветом на рисунке помечены регистры, актуальные лишь для порта; звездочкой отмечены необязательные регистры.

Рис. 7.4. Специфические конфигурационные регистры порта и карты AGP |

Регистр APBASELO (только в порте) задает местоположение апертуры AGP:

биты [31:22] задают адрес;

биты [21:4] всегда нулевые (размер апертуры не может быть меньше 4 Мбайт);

бит 3 = 1 — признак возможности предвыборки;

биты [2:1] задают разрядность адреса: 00 — 32 бита, 10 — 64 бита (используется и APBASEHI).

Положение остальных регистров определяется значением CAP_PTR, который ука$ зывает адрес регистра NCAPID.

Регистр NCAPID (в порте и адаптере) содержит номер версии спецификации AGP:

биты [31:24] — резерв;

биты [23:20] — старшая цифра версии;

биты [19:16] — младшая цифра;

биты [15:8] — NEXT_PTR, указатель на следующий блок свойств (или ноль);

биты [7:0] — CAP_ID = 02, идентификатор AGP;

Регистр состояния AGP — AGPSTAT (в порте и адаптере) сообщает основные воз$ можности AGP: допустимое число запросов в очередях, поддержку внеполосной адресации, быстрой записи, адресации свыше 4 Гбайт, режимы 1x, 2x, 4x, 8x:

биты [31:24] — RQ (только для порта), допустимое суммарное число запросов, находящихся в очередях: 0 — 1 команда, 255 — 256 команд;

биты [23:18] — резерв (0);

бит 17 — ISOCH SUPPORT — поддержка изохронных обменов (AGP 3.0);

бит 16 — резерв;

биты [15:13] — ARQSZ (только для порта), указание оптимального размера (Opt_Rq_Size) запроса к графическому адаптеру, Opt_Rq_Size = 2^(ARQSZ + 4). Введены в AGP 3.0;

биты [12:10] — Cal_Cycle (только AGP 3.0), период калибровки: 000 — 4 мс, 001 — 16 мс, 010 — 64 мс, 011 — 256 мс, 111 — калибровка не требуется, осталь$ ные значения зарезервированы;

бит 9 — SBA, поддержка внеполосной подачи команд (в AGP 3.0 — резерв);

бит 8 — ITA_COH, обеспечение когерентности при обращении акселератора че$ рез апертуру (при единичном бите когерентности в соответствующем вхожде$ нии GART);

бит 7 — GART64B, поддержка 64$битных элементов GART;

бит 6 — htrans# (только AGP 3.0), трансляция запросов хоста через апертуру: 0 — при обращениях хоста в диапазоне апертуры адрес транслируется через GART, 1 — хост не посылает запросов в диапазоне апертуры;

бит 5 — Over4G, поддержка адресации памяти свыше 4 Гбайт;

бит 4 — FW, поддержка быстрой записи;

бит 3 — AGP3.0_MODE, режим работы: 0 — AGP 1.0/2.0, 1 — AGP 3.0;

биты [2:0] — RATE, поддерживаемые скорости обмена по AD и SBA. В режиме AGP 2.0: бит 0 — 1x, бит 1 — 2x, бит 2 — 4x. В режиме AGP 3.0: бит 0 — 4x, бит 1 — 8x.

Регистр команд AGP — AGPCMD (в порте и адаптере) служит для разрешения этих свойств и содержит следующие поля:

биты [31:24] — RQ_DEPTH, задание глубины очереди команд;

биты [23:16] — резерв (0);

биты [15:13] — PARQSZ (только AGP 3.0), задание оптимального размера (Opt_Rq_Size) запроса, к которому должен стремиться мастер AGP, Opt_Rq_Size = = 2 ^ (PARQSZ + 4);

биты [12:10] — PCAL_Cycle (только AGP 3.0), задание периода цикла калибровки;

бит 9 — SBA_ENABLE, установка внеполосной подачи команд;

бит 8 — AGP_ENABLE, разрешение операций AGP;

бит 7 — GART64B, разрешение использования 64$битных элементов GART;

бит 6 — резерв;

бит 5 — 4G, разрешение адресации памяти свыше 4 Гбайт (двухадресных цик$ лов и посылок 4$го типа по SBA);

бит 4 — FW_Enable, разрешение быстрой записи;

бит 3 — резерв (0);

биты [2:0] — DATA_RATE, установка режима обмена (должен быть установлен лишь один бит). В AGP 2.0: бит 0 — 1x, бит 1 — 2x, бит 2 — 4x. В AGP 3.0: бит 0 — 4x, бит 1 — 8x, бит 3 — резерв.

Регистр NISTAT (в порте и адаптере) определяет возможности изохронных пере$ дач (только в AGP 3.0):

биты [31:24] — резерв (0);

биты [23:16] — MAXBW, максимальная пропускная способность устройства (сум$ марная для асинхронных и изохронных передач) в единицах по 32 байта за 1 мкс;

биты [15:8] — ISOCH_N, максимальное число изохронных транзакций за период 1 мкс;

биты [7:6] — ISOCH_Y, поддерживаемые размеры изохронных передач: 00 — 32, 64, 128, 256 байт; 01 — 64, 128, 256 байт; 10 —128, 256 и более байт, 11 — 256 байт;

биты [5:3] — ISOCH_L, максимальная задержка изохронных передач в единицах мкс (1–5);

бит 2 — резерв;

биты [1:0] — Isoch-ErrorCode, код ошибки изохронного обмена (00 — нет оши$ бок): для порта 01 — переполнение очереди изохронных запросов; для карты 01 — «переопустошение» буфера чтения, 10 — переполнение буфера записи.

Регистр NICMD (в порте и адаптере) управляет изохронными передачами (только

вAGP 3.0):

биты [15:8] — PISOCH_N, максимальное число изохронных транзакций за пери$ од 1 мкс (для карты);

биты [7:6] — PISOCH_Y, размер изохронных передач: 00 — 32, 64, 128, 256 байт; 01 — 64, 128, 256 байт; 10 —128, 256 и более байт, 11 — 256 байт;

биты [5:0] — резерв.

Регистр AGPCTRL (в порте) управляет собственно портом AGP:

биты [31:10] — резерв;

бит 9 — CAL_CYCLE_DIS, запрет циклов калибровки;

бит 8 — APERENB, разрешение работы через апертуру;

бит 7 — GTLBEN, разрешение работы буферов TLB, ускоряющих трансляцию адресов через GART (если они имеются в порте);

биты [6:0] — резерв.

Регистр APSIZE (в порте) задает размер апертуры:биты [15:12] — резерв;

биты [11:8, 5:0] — APSIZE, 111…111 — 4 Мбайт, 111…110 — 8 Мбайт, 11110…0 — 256 Мбайт, 000…000 — 4096 Мбайт;

биты [7:6] = 00.

Регистр NEPG (в порте AGP 3.0) задает размер страницы, описываемой в GART, из списка поддерживаемых:

биты [15:12] — SEL, выбранный размер страниц (2 ^ (SEL + 12));

биты [11:0] — битовая карта поддержки страниц разного размера: единица в бите N означает поддержку страниц размером (2 ^ (N + 12)). Бит 6 всегда единич$ ный — поддержка страниц размером 4 кбайт обязательна для всех портов AGP.

Регистры GARTLO[31:12] и GARTHI (в порте) задают начальный адрес таблицы GART.

Слоты и карты AGP

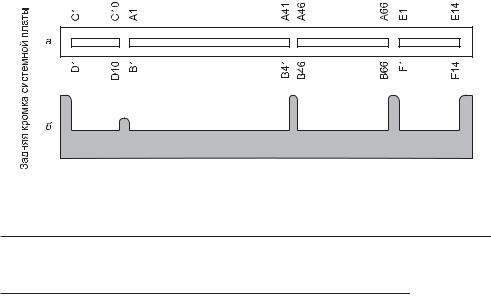

Графический адаптер с интерфейсом AGP может быть встроен в системную плату, а может располагаться и на карте расширения, установленной в слот AGP. Внешне карты с портом AGP похожи на PCI (рис. 7.5), но у них используется разъем повы$ шенной плотности с «двухэтажным» (как у EISA) расположением ламелей. Сам разъем находится дальше от задней кромки платы, чем разъем PCI.

Рис. 7.5. Слоты AGP: a — 3,3 В; б — 1,5 В; в — универсальные

Порт AGP может использовать три возможных номинала питания интерфейсных схем (Vddq): 3,3 В (для 1x и 2x), 1,5 В (для 2x и 4x) и 0,8 В (для 8x). Сигналы RST# и CLK всегда 3$вольтовые. На слотах и картах имеются механические ключи, пре$ дотвращающие ошибочные подключения:

слот и карта AGP 1.0 используют напряжение 3,3 В; они имеют ключи на месте контактов 22–25 (перегородка в слоте, рис. 7.5, а, вырез на разъеме карты);

слот и карта AGP 2.0 используют напряжение 1,5 В, они имеют ключи на месте контактов 42–45;

универсальный слот AGP 2.0 (3,3 В/1,5 В) не имеет перегородок, а универсаль$ ная карта имеет оба выреза. Универсальная системная плата узнает о номинале питания буферов установленной карты по сигналу TYPEDET# — на картах 3,3 В контакт свободен, на картах 1,5 В и универсальных — заземлен. Универсальная карта узнает о номинале питания буферов по уровню напряжения на контактах Vddq (3,3 или 1,5 В). Таким образом и обеспечивается согласование режима кар$ ты и системной платы;

слот и карта AGP 3.0 используют напряжение 0,8 В, но по ключам они аналогичны 1,5$вольтовым слотам и картам (ключи на месте контактов 42–45). Карта узнает порт AGP 3.0 по заземленной линии MB_DET# (в порте AGP 2.0 он свободен);

универсальный слот AGP 3.0 может работать с картой 8x (напряжение 0,8В) и AGP 2.0 (4х, 1,5 В). Здесь напряжение 0,8 В и режим 8x выбираются логикой порта и карты.

Для работы в режимах 2x/4x/8x приемникам требуется опорное напряжение Vref. Его номинал для 3,3 В составляет 0,4×Vddq, для 1,5 В — 0,5×Vddq, для 0,8 В — 0,233×Vddq. Опорное напряжение для приемников генерируется на стороне пере$ датчиков. На контакт A66 (Vrefgc) графическое устройство подает сигнал для пор$ та, на контакт B66 (Vrefcg) порт (чипсет) подает напряжение для устройства AGP.

При передаче в режиме 8x применяется динамическое инвертирование данных на шине AD. Сигнал DBI_LO указывает на инверсию линий AD[15:0], DBI_HI — на ин$ версию AD[31:0]. Решение об изменении состояния инверсии принимается сравне$ нием выводимой информации с информацией предыдущего такта: если число пе$ реключаемых линий в соответствующей половине AD более 8, то соответствующий сигнал DBI_xx меняет состояние на противоположное. Таким образом, на каждой половине шины AD одновременно будет переключаться не более 8 сигнальных ли$ ний, что позволяет уменьшить броски тока. Для режима 8x применяется автома$ тическая калибровка приемопередатчиков, позволяющая согласовать их парамет$ ры с линией и партнером. Калибровка производится как статически (при начальном запуске), так и динамически в процессе работы, чтобы компенсировать уход пара$ метров из$за изменения температуры.

В табл. 7.1 приведено назначение контактов слота AGP применительно к версии 3.0, в скобках приведены назначения контактов для AGP 1.0 и 2.0. Из$за двух ключей на универсальной карте AGP 2.0 теряется пара контактов для подачи питания VCC3.3, и их остается только 4, что ограничивает потребляемый ток (допустимый ток для каждого контакта — 1 А). На универсальной карте AGP 2.0 также нет дополни$ тельного питания 3,3Vaux, используемого для питания цепей формирования сиг$ нала PME# в режиме «сна».

Таблица 7.1. Назначение контактов порта AGP

Ряд B |

№ |

Ряд A |

Ряд B |

№ |

Ряд A |

OVRCNT# |

1 |

12V |

Vddq |

34 |

Vddq |

5.0V |

2 |

TYPEDET# |

AD21 |

35 |

AD22 |

продолжение

Таблица 7.1 (продолжение)

Ряд B |

№ |

Ряд A |

|

Ряд B |

№ |

Ряд A |

|

|

|

|

|

|

|

5.0V |

3 |

Резерв |

|

AD19 |

36 |

AD20 |

USB+ |

4 |

USB– |

|

GND |

37 |

GND |

GND |

5 |

GND |

|

AD17 |

38 |

AD18 |

INTB# |

6 |

INTA# |

|

C/BE2# |

39 |

AD16 |

CLK |

7 |

RST# |

|

Vddq |

40 |

Vddq |

REQ# |

8 |

GNT# |

|

IRDY# |

41 |

FRAME# |

VCC3.3 |

9 |

VCC3.3 |

|

Ключ 1,5 В (3,3Vaux) |

42 |

Ключ 1,5 В (Резерв) |

ST0 |

10 |

ST1 |

|

Ключ 1,5 В (GND) |

43 |

Ключ 1,5 В (GND) |

ST2 |

11 |

MB_DET#3 |

|

Ключ 1,5 В (Резерв) 44 |

Ключ 1,5 В (Резерв) |

|

RBF# |

12 |

DBI_HI (PIPE#) |

|

Ключ 1,5 В (VCC3.3) |

45 |

Ключ 1,5 В (VCC3.3) |

GND |

13 |

GND |

|

DEVSEL# |

46 |

TRDY# |

DBI_LO 3 |

14 |

WBF# |

|

Vddq |

47 |

STOP# |

SBA0 |

15 |

SBA1 |

|

PERR# |

48 |

PME# |

VCC3.3 |

16 |

VCC3.3 |

|

GND |

49 |

GND |

SBA2 |

17 |

SBA3 |

|

SERR# |

50 |

PAR |

SB_STBF (SB_STB) |

18 |

SB_STBS (SB_STB#1) |

|

C/BE1# |

51 |

AD15 |

GND |

19 |

GND |

|

Vddq |

52 |

Vddq |

SBA4 |

20 |

SBA5 |

|

AD14 |

53 |

AD13 |

SBA6 |

21 |

SBA7 |

|

AD12 |

54 |

AD11 |

Резерв (ключ 3,3 В) |

22 |

Резерв (ключ 3,3 В) |

|

GND |

55 |

GND |

GND (ключ 3,3 В) |

23 |

GND (ключ 3,3 В) |

|

AD10 |

56 |

AD9 |

3,3Vaux (ключ 3,3 В) |

24 |

Резерв (ключ 3,3 В) |

|

AD8 |

57 |

C/BE0# |

VCC3.3 (ключ 3,3 В) |

25 |

VCC3.3 (ключ 3,3 В) |

|

Vddq |

58 |

Vddq |

AD31 |

26 |

AD30 |

|

AD_STBF0 (AD_STB0) |

59 |

AD_STBS0 (AD_STB0#1) |

AD29 |

27 |

AD28 |

|

AD7 |

60 |

AD6 |

VCC3.3 |

28 |

VCC3.3 |

|

GND |

61 |

GND |

AD27 |

29 |

AD26 |

|

AD5 |

62 |

AD4 |

AD25 |

30 |

AD24 |

|

AD3 |

63 |

AD2 |

GND |

31 |

GND |

|

Vddq |

64 |

Vddq |

AD_STBF1 (AD_STB1) |

32 |

AD_STBS1 (AD_STB1#1) |

|

AD1 |

65 |

AD0 |

AD23 |

33 |

C/BE3# |

|

Vrefcg2 |

66 |

Vrefgc2 |

|

||||||

|

|

|

|

|

|

|

1 Инверсные стробы отсутствуют на картах и слотах 3,3 В (там нет режима 4x/8x). 2 Опорное напряжение не требуется для слотов и карт 1x.

3 Только в AGP 3.0.

Кроме собственно AGP в порте AGP заложены сигналы шины USB, которую пред$ полагается заводить в монитор (линии USB+, USB– и сигнал OVRCNT#, которым сооб$ щается о перегрузке по току линии питания + 5 В, выводимой в монитор).

Сигнал PME# относится к интерфейсу управления энергопотреблением (Power Management Interface). При наличии дополнительного питания 3,3Vaux этим сиг$ налом карта может инициировать «пробуждение».

Спецификация AGP Pro описывает более мощный коннектор, позволяющий в 4 раза повысить мощность, подводимую к графической карте. При этом сохраняется од$ носторонняя совместимость: карты AGP могут устанавливаться в слот AGP Pro, но не наоборот. В настоящее время от коннектора AGP Pro отказались, а для пода$ чи питания на графическую карту используется дополнительный кабель с разъ$ емом.

Коннектор AGP Pro имеет дополнительные контакты с обеих сторон обычного коннектора AGP (рис. 7.6) для линий GND и питания 3,3 и 12 В, назначение этих контактов приведено в табл. 7.2. Для правильной установки обычной карты со сто$ роны задней кромки системной платы дополнительная часть слота AGP Pro за$ крывается съемной пластмассовой заглушкой. Карта AGP Pro может также ис$ пользовать 1–2 соседних слота PCI: чисто механически (как точки опоры и место), как дополнительные коннекторы для подачи питания, как функциональные кон$ некторы PCI. Потребности в дополнительном питании и креплении взаимосвяза$ ны: высокопроизводительные карты потребляют большую мощность, для отвода которой требуются мощные (и тяжелые) радиаторы и вентиляторы. К счастью, про$ гресс в технологии изготовления микросхем приводит к улучшению соотношения «мощность/производительность», так что задача питания и крепления графиче$ ского адаптера несколько упростилась.

Рис. 7.6. Коннектор карты AGP Pro (показан ключ питания карты 1,5 В): а — вид сверху; б — профиль ключей

Таблица 7.2. Дополнительные контакты коннектора AGP Pro

Цепь |

Контакты |

VCC3.3 |

C1, C3, D1…D8 |

GND |

C2, C4…C8, E3…E14 |

продолжение

Таблица 7.2 (продолжение)

Цепь |

Контакты |

VCC12 |

F3…F14 |

PRSNT1# |

D10 |

PRSNT2# |

D9 |

Резерв |

C9, C10, E1, E2, F1, F2 |

|

|

В совокупности карта AGP Pro может потреблять до 110 Вт мощности, забирая ее по шинам питания 3,3 В (до 7,6 А) и 12 В (до 9,2 А) с основного разъема AGP, дополнительного разъема питания AGP Pro и одного$двух разъемов PCI. Карты AGP Pro большой мощности (High Power, 50–110 Вт) занимают 2 слота PCI, малой (Low Power, 25–50 Вт) — 1 слот. Соответственно скобка крепления к задней пане$ ли ПК у них имеет утроенную или удвоенную ширину. Кроме того, карты имеют крепеж к передней стенке ПК. На дополнительном разъеме цепь PRSNT1# служит признаком наличия карты (контакт заземлен), а PRSNT2# — признаком потребляе$ мой мощности (до 50 Вт — контакт свободен, до 110 Вт — заземлен).

PCI Express

PCI Express — новая архитектура соединения компонентов, введенная под эгидой PCI SIG, известная и под названием 3GIO (3$Generation Input$Output, ввод/вы$ вод 3$го поколения). Здесь шинное соединение устройств с параллельным интер$ фейсом заменено на двухточечные последовательные соединения с использовани$ ем коммутаторов. В этой архитектуре сохраняются многие программные черты шины PCI, что обеспечивает плавность миграции от PCI к PCI Express. В архитек$ туре появились новые возможности: управление качеством обслуживания (QoS), потреблением и бюджетом связей. Протокол PCI Express отличается малыми на$ кладными расходами и малыми задержками выполнения транзакций.

PCI Express позиционируется как универсальная архитектура ввода/вывода для компьютеров разных классов, телекоммуникационных устройств и встроенных систем. Высокая пропускная способность достигается при цене, соизмеримой с PCI и ниже. Сфера применения — от соединений между микросхемами на плате до межплатных разъемных и кабельных соединений. Высокая пропускная способность на контакт соединения позволяет минимизировать число соединительных контак$ тов. Малое число сигнальных линий позволяет применять малогабаритные конст$ руктивы. Универсальность дает возможность использования единой программной модели для всех форм$факторов. Спецификация PCI Express Base specification Revision 1.0a опубликована в апреле 2003 года.

Элементы и топология соединений PCI Express

Соединение PCI Express (PCI Express Link) — это пара встречных симплексных ка$ налов, соединяющих два компонента. По этим каналам передаются пакеты, несу$ щие команды и данные транзакций, сообщения и управляющие посылки. Канал может быть образован одной или несколькими линиями передачи сигналов (Lane); применение нескольких линий позволяет масштабировать пропускную способ$ ность канала. В PCI Express с помощью пакетного протокола реализуются все тран$ закции чтения и записи, используемые в PCI, причем в расщепленном варианте. Таким образом, здесь фигурируют запросчик транзакции (Requester) и исполни тель транзакции (Completer). В PCI Express рассматриваются четыре простран