Шины.PCI,.USB.и.FireWire

.pdfТаблица 6.10 (продолжение)

№ |

|

Тип интерфейса |

|

|

|

|

№ |

Тип интерфейса |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 бит |

|

|

|

32 бита |

|

|

16 бит |

|

|

32 бита |

||

|

|

Mem |

|

I/O+Mem |

ATA |

|

CardBus |

|

|

Mem |

I/O+Mem |

ATA |

CardBus |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

26 |

|

A3 |

|

|

A3 |

|

|

CAD23 |

|

60 |

Резерв |

INPACK# |

DMARQ |

CREQ# |

27 |

|

A2 |

|

|

A2 |

DA2 |

|

CAD24 |

|

61 |

REG# |

REG# |

DMACK# |

CCBE3# |

28 |

|

A1 |

|

|

A1 |

DA1 |

|

CAD25 |

|

62 |

BVD2 |

SPKR# |

DASP# |

CAUDIO |

29 |

|

A0 |

|

|

A0 |

DA0 |

|

CAD26 |

|

63 |

BVD1 |

STSCHG# |

PDIAG# |

CSTSCHG |

30 |

|

D0 |

|

|

D0 |

DD0 |

|

CAD27 |

|

64 |

D8 |

D8 |

DD8 |

CAD28 |

31 |

|

D1 |

|

|

D1 |

DD1 |

|

CAD29 |

|

65 |

D9 |

D9 |

DD9 |

CAD30 |

32 |

|

D2 |

|

|

D2 |

DD2 |

|

Резерв |

|

66 |

D10 |

D10 |

DD10 |

CAD31 |

33 |

|

WP |

|

|

IOIS16# |

|

|

CCLKRUN# |

|

67 |

CD2# |

CD2# |

CD2# |

CCD2# |

34 |

|

GND |

|

|

GND |

GND |

|

GND |

|

68 |

GND |

GND |

GND |

GND |

|

|

|

|

|

|

|

|

|

|

|||||

Таблица 6.11. Назначение сигналов карт памяти и ввода вывода |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сигнал |

I/O |

Назначение |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A[10:0] |

|

I |

Линии шины адреса |

|

|

|

|

|

||||||

BVD1, BVD2 |

I/O |

Battery Volt Detection — идентификаторы батарейного питания |

|

|||||||||||

STSCHG# |

I/O |

(IO) Сигнализация хосту о смене состояния RDY/BSY# и Write Protect. |

||||||||||||

|

|

|

|

|

Использование этого сигнала контролируется регистром управления |

|||||||||

|

|

|

|

|

и состояния карты Card Config and Status Register |

|

|

|||||||

SPKR# |

|

O |

(IO) Дискретный аудиовыход (на динамик) |

|

|

|

||||||||

CD1#, CD2# |

O |

Card Detect — сигналы обнаружения (заземлены на карте), по которым хост |

||||||||||||

|

|

|

|

|

определяет, что карта полностью вставлена в слот |

|

|

|||||||

CE1#, CE2# |

I |

(IO, Mem) Card Enable — выбор (разрешение) карты и определение |

||||||||||||

|

|

|

|

|

разрядности передачи. Сигнал CE2# всегда относится к нечетному байту, |

|||||||||

|

|

|

|

|

CE1# — к четному или нечетному, в зависимости от A0 и CE2#. С помощью |

|||||||||

|

|

|

|

|

этих сигналов 8 битный хост может обмениваться с 16 битными картами |

|||||||||

|

|

|

|

|

по линиям D[7:0] |

|

|

|

|

|

|

|

||

D[15:0] |

|

I/O |

Шина данных (у 8 битных сигналы D[15:8] отсутствуют) |

|

|

|||||||||

INPACK# |

O |

(IO) Input Acknowledge — подтверждение ввода, ответ карты на сигнал IORD# |

||||||||||||

|

|

|

|

|

(по этому сигналу хост открывает свои буферы данных) |

|

|

|||||||

IORD# |

|

I |

Строб команды чтения портов |

|

|

|

|

|

||||||

IOWR# |

|

I |

Строб команды записи портов (данные должны фиксироваться |

|

||||||||||

|

|

|

|

|

по положительному перепаду) |

|

|

|

|

|

||||

OE# |

|

I |

Чтение данных из памяти, конфигурационных регистров и CIS |

|

||||||||||

RDY/BSY# |

I |

Готовность карты к обмену данными (при высоком уровне) |

|

|||||||||||

IREQ# |

|

O |

Запрос прерывания (низким уровнем) |

|

|

|

||||||||

INTRQ |

|

O |

Запрос прерывания (высоким уровнем) |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сигнал |

I/O |

Назначение |

REG# |

I |

Выбор памяти атрибутов (Mem). Для карт IO сигнал должен быть активен |

|

|

в циклах команд ввода вывода. В режиме ATA пассивен (соединен с Vcc |

|

|

на стороне хоста) |

RESET |

I |

Сброс (высоким уровнем) |

VS1#, VS2# |

O |

Voltage Sense — сигналы определения номинала питания. Заземленный |

|

|

сигнал VS1# означает способность чтения карты при питании 3,3 В |

WAIT# |

O |

Запрос (низким уровнем) на продление цикла обращения |

WE# |

I |

Строб записи в память и конфигурационные регистры (в ATA |

|

|

не используется, соединяется хостом с Vcc) |

WP |

O |

Write Protect — защита от записи (для карт памяти), запись в память |

|

|

возможна при низком уровне |

IOCS16# |

O |

Разрешение 16 битного обмена |

|

|

|

Интерфейс карт памяти и ввода$вывода прост — он практически совпадает с ин$ терфейсом статической асинхронной памяти. Карта выбирается сигналами CE#, действующими одновременно с установленным адресом. Чтение памяти и конфи$ гурационных регистров выполняется по сигналу OE#, запись — по сигналу WE#. Признаком, разделяющим в этих обращениях основную память и конфигураци$ онные регистры, принадлежащие области памяти атрибутов карты, является сиг$ нал REG#, действующий одновременно с CE# и адресом. Для обращения к портам ввода$вывода служат отдельные сигналы IORD# и IOWR#; во время их действия дол$ жен быть активен и сигнал REG#. В процессе обращения к портам карта может вы$ дать признак возможности 16$битных обращений сигналом IOSC16# (как на шине ISA). Чтение порта устройство должно подтверждать сигналом INPACK#, устанав$ ливаемым и снимаемым картой по сигналу CE#. Благодаря этому сигналу хост мо$ жет убедиться в том, что он читает не пустой слот.

Для мультимедийных карт имеется возможность переключения интерфейса в спе$ циальный режим ZV Port (Zoomed Video), в котором организуется отдельный двух$ точечный интерфейс передачи данных между картой и хост$системой. По смыслу интерфейс напоминает коннектор VFC графических карт — выделенная шина для передачи видеоданных, не связанная с остальными шинами (и не загружающая их), но имеет иной протокол. В режиме ZV Port адресные линии A[25:4], а также линии BVD2/SPKR#, INPACK# и I0IS16# получают иное назначение — по ним переда$ ются видеоданные и 4 цифровых аудиоканала. Для обычного интерфейса остают$ ся лишь 4 адресные линии, позволяющие адресоваться к 16 байтам общей памяти и атрибутов карты.

Интерфейс порта ZV соответствует временным диаграммам CCIR601, что позво$ ляет декодеру NTSC в реальном времени доставлять видеоданные с карты в эк$ ранный буфер VGA. Видеоданные могут поступать на карту как с внешнего видео$ входа, так и с декодера MPEG.

Карты имеют специальное выделенное пространство памяти атрибутов, в котором находятся конфигурационные и управляющие регистры карты, предназначенные

для автоконфигурирования. Стандартом описан формат информационной струк туры карты (Card Information Structure, CIS). Карты могут быть многофункцио$ нальными (например, комбинация модема и сетевого адаптера). В спецификации MFPC (Multiple Function PC Cards) для каждой функции предусматриваются от$ дельные конфигурационные регистры и определяются правила разделения (со$ вместного использования) линии запроса прерывания.

Для устройств внешней памяти стандарт описывает форматы хранения данных, совместимые с FAT MS$DOS, а также ориентированные на флэш$память как ос$ новной носитель информации. Для непосредственного исполнения модулей ПО, хранящихся в ПЗУ карты, имеется спецификация XIP (eXecute In Place), описываю$ щая программный интерфейс вызова этих модулей (вместо загрузки ПО в ОЗУ).

Стандарт описывает программный интерфейс сервисов карт (Card Services), обес$ печивающий унификацию взаимодействия его клиентов (драйверов, прикладного ПО и утилит) с устройствами. Имеется также и интерфейс сервисов сокета (Socket Services), с помощью которого выполняются операции, связанные с обнаружением фактов подключения$отключения карт, их идентификации, конфигурирования питания и аппаратного интерфейса.

В стандарте имеются описания специфических особенностей, свойственных двум организациям, ведущим стандарт PC Card:

PCMCIA описывает автоиндексируемую массовую память (AIMS) для хране$ ния больших массивов данных (изображений, мультимедийных данных) на блочно$ориентированных устройствах. Имеется также спецификация 15$кон$ тактного экранированного разъема для подключения модемов и адаптеров ло$ кальной сети (15$pin Shielded Modem I/O connector) и 7$контактного для под$ ключения модемов (7$pin Modem I/O connector);

JEDIA для карт памяти предлагает формат файлов Small Block Flash Format, упрощающий файловую систему. Формат SISRIF (Still Image, Sound and Related Information Format) предназначен для записи изображений и звука на карты памяти. Имеется и спецификация для карт динамической памяти.

PCI в инструментальных системах: cPCI и PXI

Для устройств промышленного назначения в начале 1995 года был принят стан$ дарт Compact PCI. Шина Compact PCI (cPCI) разрабатывалась на основе специ$ фикации PCI 2.1. Этот стандарт принят Организацией производителей промыш$ ленных компьютеров PCIMG (PCI Industrial Computer Manufacturers Group). Шина отличается поддержкой большого количества слотов: 8 против 4 в обычной PCI. Как и PCI, шина поддерживает 32$битный и 64$битный обмен. Шина облада$ ет всеми возможностями автоконфигурирования, присущими PCI. Кроме того, шина дает возможность программного прочтения «географического адреса» моду$ ля. Географическая адресация дает дополнительную возможность идентификации физического местоположения модуля (хотя его можно определить и по номерам

шины и устройства, пользуясь стандартными конфигурационными функциями PCI). Конструктивно платы Compact PCI представляют собой еврокарты высотой 3U (100×160 мм) с двумя коннекторами (J1 и J2) или 6U (233,35×160 мм) с 4–5 коннекторами (J1…J5). На шасси разъемы обозначаются P1…P5; платы (модули) устанавливаются с шагом 20,32 мм (0,8 дюйма). Одно посадочное место (слот), как правило крайнее левое, отводится под системный модуль, остальные — под периферийные. В системный слот устанавливается контроллер шины, на который возлагаются функции арбитража и синхронизации. На его коннекторе шиной ис$ пользуется большее число контактов, чем на остальных. Вид шасси и модулей Compact PCI приведен на рис. 6.5, на рисунке видно символическое обозначение места контроллера (номер системного слота — в треугольнике, периферийных — в круге). На шасси может быть несколько сегментов cPCI — независимых шин; если требуется, связь между ними организуется через модули$мосты, устанавливаемые в слоты. В каждом сегменте должен быть собственный контроллер шины.

Рис. 6.5. Конструктив Compact PCI: а — шасси; б — вид полноразмерного модуля; в — варианты модулей

Коннекторы — 7$рядные экранированные штырьковые разъемы с шагом 2 мм между контактами, на кросс$плате — вилка, на модулях — розетки. Поскольку модули (и разъемы) обычно устанавливаются вертикально, ряды удобнее назвать колон$ ками, что и подразумевается ниже. Из 7 колонок контактов (z, a, b, c, d, e, f) только 5 (a–e) используются для сигнальных цепей, а колонки z и f — только для экрана (соединяются с шиной GND)1. Контакты коннекторов имеют разную длину: более длинные контакты цепей питания при установке модуля соединяются раньше, а при вынимании разъединяются позже, чем сигнальные. Такое решение позволяет про$ изводить «горячую» замену модулей. Собственно шина использует только кон$

1 В спецификации разъемы называют и 5$рядными.

некторы J1 и J2, плотно примыкающие друг к другу (они могут выглядеть как еди$ ный 47$позиционный разъем). Контакты J1 используются для сигналов 32$битной шины PCI; периферийная 32$битная плата может и не иметь разъема J2. Ряды 12– 14 используются как ключи для вариантов с уровнями сигналов 5В/3,3В. Здесь возможны универсальные платы, но не допускаются универсальные шасси. Разъем J2 используется по$разному: системный контроллер использует его для сигналов арбитража и синхронизации, разводящихся по периферийным слотам радиально. На периферийных платах он может и отсутствовать. В 64$разрядных системах J2 используется для расширения шины; в 32$разрядных он может использоваться для сигналов ввода$вывода, разводящихся через шасси. На этот же разъем выведены сигналы географической адресации (которые можно и не использовать). Назначе$ ние контактов разъемов J1 и J2 Compact PCI версии 2.1 приведено в табл. 6.12. Разъемы J3…J5 отводятся для прикладного использования. Конструкция коннек$ торов позволяет применять для них специфические модификации (например, с разделяющим экраном и механическими ключами). В шине предусматривается наличие независимых источников питания + 5 В, + 3,3 В и ± 12 В.

Таблица 6.12. Назначение контактов разъема cPCI

Разъем, |

№ |

Ряд |

|

|

|

|

контакт |

|

a |

b |

C |

d |

e |

|

|

|

|

|

|

|

J2 |

22 |

GA4 |

GA3 |

GA2 |

GA1 |

GA0 |

|

21 |

CLK6 |

GND |

RSV |

RSV |

RSV |

|

20 |

CLK5 |

GND |

RSV |

GND |

RSV |

|

19 |

GND |

GND |

RSV |

RSV |

RSV |

|

18 |

BRSVP2A18 |

BRSVP2B18 |

BRSVP2C18 |

GND |

BRSVP2E18 |

|

17 |

BRSVP2A17 |

GND |

PRST# |

REQ6# |

GNT6# |

|

16 |

BRSVP2A16 |

BRSVP2B16 |

DEG# |

GND |

BRSVP2E16 |

|

15 |

BRSVP2A15 |

GND |

FAL# |

REQ5# |

GNT5# |

|

14 |

AD35 |

AD34 |

AD33 |

GND |

AD32 |

|

13 |

AD38 |

GND |

V(I/O) |

AD37 |

AD36 |

|

12 |

AD42 |

AD41 |

AD40 |

GND |

AD39 |

|

11 |

AD45 |

GND |

V(I/O) |

AD44 |

AD43 |

|

10 |

AD49 |

AD48 |

AD47 |

GND |

AD46 |

|

9 |

AD52 |

GND |

V(I/O) |

AD51 |

AD50 |

|

8 |

AD56 |

AD55 |

AD54 |

GND |

AD53 |

|

7 |

AD59 |

GND |

V(I/O) |

AD58 |

AD57 |

|

6 |

AD63 |

AD62 |

AD61 |

GND |

AD60 |

|

5 |

C/BE5# |

GND |

V(I/O) |

C/BE4# |

PAR64 |

|

4 |

V(I/O) |

BRSVP2B4 |

C/BE7# |

GND |

C/BE6# |

|

|

|

|

|

|

|

Разъем, |

№ |

Ряд |

|

|

|

|

контакт |

|

a |

b |

C |

d |

e |

|

|

|

|

|

|

|

|

3 |

CLK4 |

GND |

GNT3# |

REQ4# |

GNT4# |

|

2 |

CLK2 |

CLK3 |

SYSEN# |

GNT2# |

REQ3# |

|

1 |

CLK1 |

GND |

REQ1# |

GNT1# |

REQ2# |

J1 |

25 |

5V |

REQ64# |

ENUM# |

3.3V |

5V |

|

24 |

AD1 |

5V |

V(I/O) |

AD0 |

ACK64# |

|

23 |

3.3V |

AD4 |

AD3 |

5V |

AD2 |

|

22 |

AD7 |

GND |

3.3V |

AD6 |

AD5 |

|

21 |

3.3V |

AD9 |

AD8 |

M66EN |

C/BE0# |

|

20 |

AD12 |

GND |

V(I/O) |

AD11 |

AD10 |

|

19 |

3.3V |

AD15 |

AD14 |

GND |

AD13 |

|

18 |

SERR# |

GND |

3.3V |

PAR |

C/BE1# |

|

17 |

3.3V |

IPMB_SCL |

IPMB_SDA |

GND |

PERR# |

|

|

|

(SDONE)1 |

(SBO#)1 |

|

|

|

16 |

DEVSEL# |

GND |

V(I/O) |

STOP# |

LOCK# |

|

15 |

3.3V |

FRAME# |

IRDY# |

BD_SEL# |

TRDY# |

|

|

|

|

|

(GND)2 |

|

|

12–14 |

Зона ключа |

|

|

|

|

|

11 |

AD18 |

AD17 |

AD16 |

GND |

C/BE2# |

|

10 |

AD21 |

GND |

3.3V |

AD20 |

AD19 |

|

9 |

C/BE3# |

IDSEL |

AD23 |

GND |

AD22 |

|

8 |

AD26 |

GND |

V(I/O) |

AD25 |

AD24 |

|

7 |

AD30 |

AD29 |

AD28 |

GND |

AD27 |

|

6 |

REQ# |

GND |

3.3V |

CLK |

AD31 |

|

5 |

BRSVP1A5 |

BRSVP1B5 |

RST# |

GND |

GNT# |

|

4 |

IPMB_PWR |

HEALTHY# (GND)1 |

V(I/O) |

INTP |

INTS |

|

|

(BRSVP1A4)1 |

|

|

|

|

|

3 |

INTA# |

INTB# |

INTC# |

5V |

INTD# |

|

2 |

TCK |

5V |

TMS |

TDO |

TDI |

|

1 |

5V |

12V |

TRST# |

+12V |

5V |

|

|

|

|

|

|

|

1 Назначение в скобках — для старых версий.

2 На системном слоте — GND.

В основном сигналы Compact PCI совпадают с сигналами обычной шины PCI (см. табл. 2.1 на стр. 41), назначение специфических сигналов приведено в табл. 6.13.

Таблица 6.13. Специфические сигналы шины Compact PCI

Сигнал |

Назначение |

BD_SEL# |

Сигнал от модуля о том, что он установлен в слот и питание подано |

|

(подается через один из укороченных контактов, который соединяется |

|

после всех основных) |

BRSVxxxx |

Зарезервированные на будущее сигналы, шинно разведенные |

|

по слотам; xxxx обозначает позиционный номер контакта |

|

(BRSVP1A4 — на контакте A4 разъема P1) |

CLK[0:6], GNT#[0:6], |

Сигналы, радиально разводящиеся от разъема J2 системного слота |

REQ#[0:6] |

к периферийным (сигналы CLK0, GNT0# и REQ0# расположены |

|

на местах CLK, GNT# и REQ# разъема J1) |

DEG# |

Предупреждение о деградации питания |

ENUM# |

Все аппаратные модули установлены, можно производить нумерацию |

|

и конфигурирование устройств |

FAL# |

Отказ питания |

GA0 GA4 |

Географический адрес. Коммутацией на «землю» для каждого слота |

|

задается его двоичный географический адрес на шасси |

SMB_SDA, SMB_SCL, |

Сигналы шины SMBus (только на системном слоте) |

SMB_ALERT# |

Сигнал прерывания по шине SMBus |

HEALTHY# |

Сигнал от модуля, что он получает нормальное питание (PwrGood) |

|

и сигнал его сброса снят |

INTP, INTS |

Прерывания от первичного и вторичного контроллеров IDE |

IPMB_PWR, |

Батарейное питание шины IPMB (Independent Platform Management |

|

Bus, независимая последовательная шина управления платформой) |

IPMB_SCL, IPMB_SDA |

Синхронизация и данные шины IPMB |

PRST# |

Push Button Reset, сигнал от кнопки «Сброс» |

RSV |

Резерв на будущее |

SYSEN# |

Идентификация системного слота (на системном слоте контакт |

|

заземлен, что позволяет модулю опознать установку в это место) |

UNC |

Не подключен |

|

|

На базе шины Compact PCI фирмой National Instruments разработана специфика ция PXI (PCI eXtensions for Instrumentation — расширение PCI для инструмен$ тальных систем) в тех же конструктивах. По сравнению с cPCI в PXI более жестко определяется местоположение модулей. На шасси левый слот отводится для кон троллера шины, следующий за ним — для контроллера синхронизации (его номер пишут в ромбе), остальные — для периферийных модулей. При необходимости кон$ троллер может расширяться влево, занимая дополнительные слоты, разъемы ко$ торых не связаны с общей шиной.

В шине PXI часть контактов J2/P2, определенных в Compact PCI как резервные, предназначаются для организации дополнительных локальных шин и синхрони$ зации. Резервными остались только PXI_BRSVA15 и PXI_BRSVB4, разведенные по всем

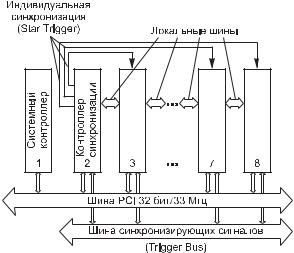

слотам шасси. Топологию соединений на шасси PXI иллюстрирует рис. 6.6. На$ значение контактов J2 для периферийных модулей, системного контроллера и кон$ троллера синхронизации приведено в табл. 6.14–6.16. Специфические сигналы шины PXI имеют обозначения, начинающиеся с префикса PXI_. Назначение кон$ тактов J1 см. в табл. 6.12.

Рис. 6.6. Топология соединений в PXI

В инструментальных системах зачастую требуется синхронизация разных моду$ лей, для этого в PXI имеются специальные сигнальные линии. Шина синхронизи рующих сигналов Trigger Bus (8 линий) PXI_TRIG[0:7] объединяет все слоты одного сегмента PXI, за исключением системного. Кроме того, имеются 13 линий индиви дуальной синхронизации (Star Trigger), звездообразно соединяющих слот контрол$ лера синхронизации с остальными периферийными слотами всего шасси (может распространяться и на два сегмента PXI). Каждая из линий PXI_STAR[0:12] слота контроллера синхронизации соединяется с линией PXI_STAR своего слота. Развод$ ка линий обеспечивает идентичность задержек, вносимых ими в распространение сигнала между слотом контроллера синхронизации и периферийными слотами. Линии PXI_TRIG[0:7] и PXI_STAR[0:12] могут использоваться двояко: как для подачи команд запуска модулям от контроллера синхронизации, так и для сообщения модулями своего состояния (зависит от приложения шасси). Для прецизионной синхронизации имеется сигнал опорной частоты 10 МГц PXI_CLK10, который шас$ си синхронно (со сдвигом не более 1 нс) доставляет ко всем слотам. Для каждого слота предоставляется отдельный выход буфера; источником сигнала может быть как шасси, так и контроллер синхронизации (через сигнал PXI_CLK10_IN).

Локальные шины в PXI предназначены для связи соседних пар слотов. Локальные шины объединяют смежные слоты попарно (исключая слот системного контрол$ лера), образуя цепочку устройств (daisy chain). Каждая локальная шина имеет

13 линий, соединяющих цепи PXI_LBR[0:12] левого слота с цепями PXI_LBL[0:12] пра$ вого слота пары. Линии могут использоваться как для цифровых, так и аналого$ вых (до 48 В, 200 мА) сигналов. Цепи PXI_LBR[0:12] последнего (самого правого) слота могут выводиться на внешний разъем шасси. Для слота контроллера син$ хронизации линии PXI_LBL[0:12] недоступны — их контакты заняты звездообраз$ ными сигналами синхронизации.

Кроме механических и электрических характеристик PXI определяет ПО моду$ лей: основной ОС считается Windows NT/2000/9x, и модули должны поставлять$ ся с соответствующими драйверами. Это экономит время, необходимое для си$ стемной интеграции. В качестве средств разработки ПО предлагается использовать пакеты LabVIEW, LabWindows/CVI фирмы National Instruments; Visual Basic, Visual C/C++ от Microsoft и Turbo C/C++ от Borland. Модули PXI совместимы с шиной Compact PCI, а модули Compact PCI — с шиной PXI. Однако все преиму$ щества спецификации реализуются только при установке модулей PXI в шину PXI.

Таблица 6.14. Разъем J2/P2 PXI для периферийного слота

Контакт |

а |

b |

с |

d |

e |

22 |

GA4 |

GA3 |

GA2 |

GA1 |

GA0 |

21 |

PXI_LBR0 |

GND |

PXI_LBR1 |

PXI_LBR2 |

PXI_LBR3 |

20 |

PXI_LBR4 |

PXI_LBR5 |

PXI_LBL0 |

GND |

PXI_LBL1 |

19 |

PXI_LBL2 |

GND |

PXI_LBL3 |

PXI_LBL4 |

PXI_LBL5 |

18 |

PXI_TRIG3 |

PXI_TRIG4 |

PXI_TRIG5 |

GND |

PXI_TRIG6 |

17 |

PXI_TRIG2 |

GND |

RSV |

PXI_STAR |

PXI_CLK10 |

16 |

PXI_TRIG1 |

PXI_TRIG0 |

RSV |

GND |

PXI_TRIG7 |

15 |

PXI_BRSVA15 |

GND |

RSV |

PXI_LBL6 |

PXI_LBR6 |

|

|

|

|

|

|

Ряды 5–14 как у Compact PCI |

|

|

|

|

|

|

|

|

|

|

|

4 |

V(I/O) |

PXI_BRSVB4 |

C/BE7# |

GND |

C/BE6# |

3 |

PXI_LBR7 |

GND |

PXI_LBR8 |

PXI_LBR9 |

PXI_LBR10 |

2 |

PXI_LBR11 |

PXI_LBR12 |

UNC |

PXI_LBL7 |

PXI_LBL8 |

1 |

PXI_LBL9 |

GND |

PXI_LBL10 |

PXI_LBL11 |

PXI_LBL12 |

|

|

|

|||

Таблица 6.15. Разъем J2/P2 PXI для системного слота |

|

|

|||

|

|

|

|

|

|

Контакт |

а |

b |

c |

d |

e |

|

|

|

|

|

|

22 |

GA4 |

GA3 |

GA2 |

GA1 |

GA0 |

21 |

CLK6 |

GND |

RSV |

RSV |

RSV |

20 |

CLK5 |

GND |

RSV |

GND |

RSV |

19 |

GND |

GND |

SMB_SDA |

SMB_SCL |

SMB_ALERT# |

18 |

PXI_TRIG3 |

PXI_TRIG4 |

PXI_TRIG5 |

GND |

PXI_TRIG6 |

17 |

PXI_TRIG2 |

GND |

PRST# |

REQ6# |

GNT6# |

|

|

|

|

|

|

Контакт |

а |

b |

c |

d |

e |

16 |

PXI_TRIG1 |

PXI_TRIG0 |

DEG# |

GND |

PXI_TRIG7 |

15 |

PXI_BRSVA15 |

GND |

FAL# |

REQ5# |

GNT5# |

|

|

|

|

|

|

Ряды 5–14 как у Compact PCI |

|

|

|

|

|

|

|

|

|

|

|

4 |

V(I/O) |

PXI_BRSVB4 |

C/BE7# |

GND |

C/BE6# |

3 |

CLK4 |

GND |

GNT3# |

REQ4# |

GNT4# |

2 |

CLK2 |

CLK3 |

SYSEN# |

GNT2# |

REQ3# |

1 |

CLK1 |

GND |

REQ1# |

GNT1# |

REQ2# |

|

|

||||

Таблица 6.16. Разъем J2/P2 PXI для слота контроллера синхронизации |

|

||||

|

|

|

|

|

|

Контакт |

a |

b |

c |

d |

е |

|

|

|

|

|

|

22 |

GA4 |

GA3 |

GA2 |

GA1 |

GA0 |

21 |

PXI_LBR0 |

GND |

PXI_LBR1 |

PXI_LBR2 |

PXI_LBR3 |

20 |

PXI_LBR4 |

PXI_LBR5 |

PXI_STAR0 |

GND |

PXI_STAR1 |

19 |

PXI_STAR2 |

GND |

PXI_STAR3 |

PXI_STAR4 |

PXI_STAR5 |

18 |

PXI_TRIG3 |

PXI_TRIG4 |

PXI_TRIG5 |

GND |

PXI_TRIG6 |

17 |

PXI_TRIG2 |

GND |

RSV |

PXI_CLK10_IN |

PXI_CLK10 |

16 |

PXI_TRIG1 |

PXI_TRIG0 |

RSV |

GND |

PXI_TRIG7 |

15 |

PXI_BRSVA15 |

GND |

RSV |

PXI_STAR6 |

PXI_LBR6 |

|

|

|

|

|

|

Ряды 5–14 как у Compact PCI |

|

|

|

|

|

|

|

|

|

|

|

4 |

V(I/O) |

PXI_BRSVB4 |

C/BE7# |

GND |

C/BE6# |

3 |

GND |

PXI_LBR8 |

PXI_LBR9 |

PXI_LBR10 |

|

2 |

PXI_LBR12 |

UNC |

PXI_STAR7 |

PXI_STAR8 |

|

1 |

GND |

PXI_STAR10 |

PXI_STAR11 |

PXI_STAR12 |

|

|

|

|

|

|

|