umm_7154

.pdfется (бит b равен 0). Если строка пропускается (бит b равен 1), то команда выполняется за два машинных цикла, потому что требуется очистка конвейера. Проверка бита 2 в регистре STATUS (флаг Z) выполняется строкой:

btfss STATUS, 2

BTFSC f, b (Bit Test File, Skip if Clear) – пропустить следующую команду, если бит b в регистре f равен 0. Команда выполняется за один машинный цикл, когда следующая строка не пропускается (бит b равен 1). Если строка пропускается (бит b равен 0), то команда выполняется за два машинных цикла, потому что требуется очистка конвейера. Проверка бита 2 в регистре STATUS (флаг Z) выполняется строкой:

btfsc STATUS, 2

INCFSZ f, d (INCrement File, Skip if Zero) – увеличить содержимое регистра на 1 (инкрементирование) и пропустить следующую строку при нулевом результате. Для 8-разрядного микроконтроллера нулевой результат при инкрементировании получается, если прибавить 1 к h’FF’. Команда выполняется за два машинных цикла, когда следующая за ней строка пропускается. За один цикл, если пропуск строки отсутствует. Результат инкрементирования сохраняется либо в f (при d = 1), либо в W (при d = 0).

incfsz h’20’, 1

DECFSZ f, d (DECrement File, Skip if Zero) – уменьшить содержимое регистра f на 1 (декрементирование) и в случае равенства его нулю пропустить следующую команду. Команда выполняется за один машинный цикл, когда следующая строка не пропускается. Если строка пропускается, то команда выполняется за два машинных цикла. Результат декрементирования сохраняется либо в f (при d = 1), либо в W (при d = 0).

decfsz h’20’, 1

NOP (No OPeration) – отсутствие операции. Команда не изменяет состояние системы, но при ее выполнении счетчик команд PC увеличивается на 1, поскольку при этом производится выборка следующей команды из памяти программ. Основное назначение команды – реализация коротких задержек. Команда не имеет операндов.

61

3.12. Прочие команды

CLRWDT (CLeaR WatchDog Timer) – сброс сторожевого таймера, данная команда не имеет операндов.

SLEEP – перевод микроконтроллера в режим энергосбережения. Команда не имеет операндов.

3.13. Программные управляющие конструкции

Программа любой сложности может быть реализована с помощью трех базовых управляющих структур: последовательности, ветвления и цикла. Последовательность обеспечивает преобразование или перемещение данных, ветвление осуществляет выбор одной из двух альтернатив в зависимости от истинности или ложности некоторого условия. Цикл применяется, когда требуется выполнить одно и то же преобразование более одного раза.

Конструкция ветвления организуется с помощью команд:

–BTFSC f, b;

–BTFSS f, b;

–INCFSZ f, d;

–DECFSZ f, d.

Например, если требуется по-разному обработать данные при наличии и отсутствии сигнала на выводе RB0, то используется следующая конструкция ветвления:

btfss PORTB, RB0 |

;если на выводе RB0 присутствует 1, |

пропустить строку |

|

goto M0 |

|

goto M1 |

|

… |

|

M0: … |

;выполнять, если RB0 = 0 |

… |

|

M1: … |

;выполнять, если RB0 = 1 |

Циклы в зависимости от наличия условия выхода делятся на условные и безусловные. Выход из безусловного цикла не предусмотрен логикой работы программы и используется для бесконечного выполнения определенной последовательности команд.

62

Однако выход из бесконечного цикла возможен, например по сигналу прерывания. Пример организации безусловного цикла:

M: goto M

Условные циклы выполняются до тех пор, пока некоторое условие истинно. Условие проверяется перед выполнением (цикл с предусловием), либо после выполнения (цикл с постусловием) тела цикла. Если условие изначально ложно, то цикл с предусловием не выполнится. Цикл с постусловием обязательно выполняется хотя бы один раз. Следующий цикл с предусловием завершается, когда содержимое рабочего регистра равно 0 (проверяется состояние флага Z):

loop: |

btfsc STATUS, Z |

|

goto exit |

|

decf h’20’ |

|

goto loop |

exit: … |

|

|

3.14. Директивы |

Директивы входят в состав исходного текста программы, но непосредственно не включаются в выходной код. Директивы используются для управления ассемблером, параметрами ввода-вы- вода и распределением данных.

#include <файл> – подключение дополнительного исходного файла к проекту, действие аналогично копированию полного текста файла в место расположения директивы.

ORG <адрес> – используется для указания адреса в памяти программ. Следующая за директивой команда будет размещена по указанному адресу. Если в тексте программы директива не встречается, команды размещаются последовательно с нулевого адреса.

__CONFIG <константа> – используется для установки битов конфигурации микроконтроллера.

<константа> EQU <значение> – присваивает указанное значение константе.

63

3.15.Организация памяти

Вмикроконтроллере PIC16F873A реализовано три вида памяти:

– оперативное запоминающее устройство (ОЗУ) – статическая

память данных, объемом 192 байта;

–Flash память программ, объемом 4096 строк, где размещается последовательность команд, составляющих программу;

–EEPROM энергонезависимая память, объемом 128 байт. Память данных и память программ имеют раздельные шины

адреса и данных, что позволяет выполнять параллельный доступ. Память программ (рис. 3.6) разделена на две страницы, – первая начинается со строки по адресу 0005 и заканчивается строкой с адресом 07FF, вторая страница включает диапазон строк с адресами 0800 по 0FFF. При сбросе микроконтроллера счетчик команд всегда очищается и переходит на вектор сброса, который расположен в строке 0000. Строка с адресом 0004 содержит вектор прерываний, переход к которому выполняется по сигналам разрешенных прерываний. Каждая строка содержит 14 двоичных разрядов. Таким образом, в одной строке размещается ровно одна команда. Счетчик команд содержит адрес выполняемой команды.

В 8-уровневый LIFO-стек значения счетчика команд заносятся при выполнении команд перехода (CALL) или обработке прерываний. Команды RETURN, RETFIE и RETLW загружают адрес из вершины стека обратно в счетчик команд. Младший байт счетчика команд PCL доступен для чтения и записи. Старший байт PCH, содержащий 8-12 биты счетчика команд, не доступен для чтения и записи. Все операции с регистром PCH происходят через дополнительный регистр PCLATH.

Так как в командах CALL, RETURN, RETFIE и RETLW для указания адреса перехода выделено всего 11 бит, что позволяет выполнять адресацию только внутри одной страницы. Для перехода между страницами соответствующим образом должен быть установлен 3-й бит регистра PCLATH.

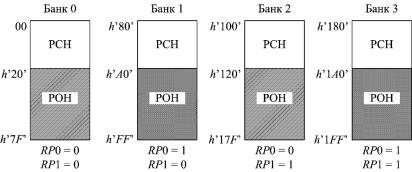

Память данных (рис. 3.7) разделена на четыре банка, которые содержат регистры специального назначения (РСН, SFR – Special Function Register) и регистры общего назначения (РОН, GPO – General Purpose Register).

64

Рис. 3.6. Организация памяти программ

65

Рис. 3.7. Организация памяти данных

Регистры специального назначения содержат биты управления и состояния периферийных устройств, эти регистры могут модифицироваться микроконтроллером. Все РСН и их адреса в памяти данных представлены на рис. 3.8. Ячейки РОН программист использует для хранения переменных и результатов промежуточных вычислений.

Для смены банка памяти используются последовательности команд:

для выбора банка 0: BCF STATUS, RP0 BCF STATUS, RP1

для выбора банка 1: BSF STATUS, RP0 BCF STATUS, RP1

для выбора банка 2: BCF STATUS, RP0 BSF STATUS, RP1

для выбора банка 3: BSF STATUS, RP0 BSF STATUS, RP1

В начале каждого банка (рис. 3.8) размещены регистры косвенной адресации, далее находится область памяти, в которой размещены регистры специального назначения. В конце каждого банка расположеныячейкиРОН,которыенаходятсяпоадресам20h…7Fh – банк 0, A0h…FFh – банк 1. Банки 2 и 3 не содержат РОН, но в них

66

Рис. 3.8. Регистры специальных функций

67

отображены РОН банков 0 и 1, т. е. при использовании области по адресам 120h…17Fh – фактически выполняется обращение к регистрам общего назначения нулевого банка памяти. А при использовании памяти по адресам 1A0h…1FFh выполняется обращение к регистрам общего назначения первого банка памяти.

Обращение к ОЗУ можно выполнить через регистр WREG или косвенно, записав адрес ячейки ОЗУ в регистр FSR, и выполнить обращение к регистру INDF. Например, если в FSR записано число h’20’, то в результате записи в регистр INDF числа 133 в ячейку h’20’ будет записано число 133:

MOVLW h’20’ MOVWF FSR MOVLW 133 MOVWF INDF

Чтобы получить содержимое ячейки h’21’ с помощью косвенной адресации следует в регистр FSR записать h’21’ и переписать INDF в рабочий регистр:

MOVLW h’21’ MOVWF FSR MOVF INDF, W

3.16. Параллельные порты

Порты используются для ввода информации от внешних устройств к микропроцессору и вывода информации от процессора к внешним устройствам. Параллельные порты могут одновременно передавать несколько бит информации.

Микроконтроллер PIC16F873A имеет три параллельных порта ввода-вывода: 6-ти разрядный порт A и два 8-ми разрядных порта B и C.

Выводы порта A мультиплексированы с входами аналоговоцифрового преобразователя и выходами компараторов. Выводы порта B – со схемой низковольтного программирования и с входом внешнего прерывания, а порта C – со схемами интервального таймера, широтно-импульсного модулятора, последовательной шины и последовательного порта.

Каналы портов ввода-вывода имеют отличия, которые заключаются в устройстве входного и выходного каскада.

68

Устройство каналов порта A показано на рис. 3.9. Каналы RA0- RA3, RA5 (рис. 3.9, а) в режиме вывода имеют вход с тремя состояниями, а по входу работают со стандартными уровнями ТТЛ. Каждый канал может индивидуально настраиваться как вход АЦП или цифровой вход-выход.

Выход с тремя состояниями реализован на двух МОП-транзи- сторах с разными типами проводимости. Транзистор P открывается нулем, транзистор N – единицей. Если оба транзистора закрыты, то выход находится в высокоимпедансном состоянии. Если открыт транзистор P, а N закрыт, то к выводу подключен высокий уровень сигнала. Когда транзистор N открыт, а P закрыт, к выводу подключена «земля».

После сброса микроконтроллера выводы RA0-RA3, RA5 настроены как каналы АЦП. Для использования их как линий вво- да-вывода, требуется подать 1 на инверсный вывод входного буфера, настроив биты PCFG0-PCFG3 в регистре ADCON1. Перед работой с каналами ввода-вывода требуется настройка направления передачи данных, которая выполняется следующим образом. На шине данных устанавливается значение 0 или 1, которое по сигналу WR TRIS переписывается на выход триггера TRIS. Если триггер TRIS установлен в 1, то на выходе элемента ИЛИ также появится 1, а на выходе И – 0. Таким образом, оба транзистора P и N окажутся закрытыми, а соответствующий канал будет настроен на ввод данных. При установке триггера TRIS в 0, состояние выходов элементов ИЛИ, И определяется триггером данных, т. е. соответствующий вывод настроен на вывод данных. Изначально все каналы настроены на ввод.

Канал RA4 (рис. 3.9, б) в режиме вывода имеет выход с открытым стоком, а в режиме ввода триггер Шмитта на входе. Линия RA4 также используется как вход внешних тактовых импульсов для таймера TMR0. Если на выходе Q̅ триггера TRIS низкий потенциал, то транзистор N закрыт, иначе состояние транзистора N определяется триггером данных.

Выход триггера данных канала RA4 мультиплексирован с компаратором C1. Аналогично с компаратором C2 мультиплексирован канал RA5. Управление мультиплексорами выполняется тремя младшими битами регистра (CMCON).

Чтение выполняется одновременно для каналов PORTA, которые настроены как цифровые входы-выходы. Значения считываются с выводов микросхемы независимо от настройки кана-

69

70

а |

б |

Рис. 3.9. Устройство каналов порта A:

а – RA0-RA3, RA5; б – RA4