umm_7154

.pdf

а |

б |

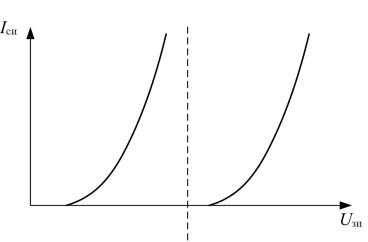

Рис. 2.25. Входная характеристика транзистора с плавающим затвором: а – при отсутствии заряда; б – при наличии заряда

Запись заряда в запоминающий элемент осуществляется инжекцией горячих электронов через слой оксида или туннелированием Фаулера-Нордгейма. Стирание хранящегося заряда (возврат транзистора в исходное состояние с низким порогом) осуществляется либо электрически – туннелированием Фаулера-Нордгейма, либо ультрафиолетовым облучением.

Инжекция горячих электронов – процесс переноса заряда через энергетический барьер, образованный тонким диэлектриком, за счет увеличения кинетической энергии электронов в канале между истоком и стоком транзистора. Электроны, обладая большим запасом кинетической энергии, пробивают слой диэлектрика, поэтому запись заряда на плавающий затвор приводит к быстрому разрушению запоминающего элемента.

Туннельный эффект Фаулера-Нордгейма состоит в том, что электрон может с конечной вероятностью проникнуть через потенциальный барьер (область пространства, для которой полная энергия частицы не превышает ее потенциальной энергии). Вероятность перехода через потенциальный барьер в значительной степени зависит от толщины потенциального барьера, которая определяется напряжением между затвором и истоком.

41

2.15.EPROM и OTP память

Вкачестве запоминающих элементов используются в основном транзисторы с плавающим затвором. EPORM память энергонезависима и позволяет многократное перепрограммирование пользователем. Программирование выполняется электрически, инжекцией горячих электронов. Для этого требуется высокое напряжение (30–40 В), что быстро разрушает полупроводниковые структуры микросхемы. Количество циклов перепрограммирования EPROM памяти составляет от 10 до 10 тыс. Стирание выполняется ультрафиолетовым облучением, для этого в корпусе микросхемы имеется кварцевое окно. После стирания окно заклеивают, чтобы избежать воздействия света на запоминающие элементы. Микросхемы EPROM, в корпусе которых не предусмотрено кварцевое окно, получили название OTP памяти. Такая память программируется однократно и не может быть стерта.

2.16.EEPROM память

Запоминающие элементы EEPROM схожи с EPROM элементами, но программируются и стираются электрическим путем за счет эффекта туннелирования электронов. При электрическом стирании, в отличие от ультрафиолетового облучения, можно стереть не все, а только некоторые ячейки. Количество циклов перезаписи достигает 105.

2.17. Flash-память

Устройство элементов аналогично EEPROM. Стирание flash памяти происходит достаточно большими блоками или одновременно для всей памяти, не предусмотрено стирание отдельных слов, в отличие от EEPROM памяти.

Как и для других полупроводников, размер элементов flash- памяти вносит наибольший вклад в стоимость устройства. По этой причине разработчики микросхем создали альтернативные структуры массивов памяти. Основные структуры flash-памяти: NOR (рис. 2.26, а) и NAND (рис. 2.26, б).

42

Рис. 2.26. Структуры flash-памяти:

а – NOR; б – NAND

Структура NOR (ИЛИ-НЕ) состоит из параллельно включенных транзисторов. При адресации все транзисторы в столбце закрыты, кроме одного, состояние которого определяется зарядом на плавающем затворе. Если транзистор закрыт, то на выходе запоминающего элемнта высокий уровень сигнала, а если открыт – появится низкий уровень. Такая организация обеспечивает возможность произвольного доступа к данным и побайтной записи.

В NAND (И-НЕ) структуре транзисторы соединены последовательно, образуют группы, которые объединяются в страницы, а страницы – в блоки. Обращение выполняется к целому блоку памяти. При выборе блока все транзисторы в столбце открыты, кроме одного, который может быть закрытым. В этом случае на выходе запоминающего устройства появляется 1.

Запись и стирание для структуры NAND выполняется быстрее при работе с большими массивами данных, кроме того достигается высокая плотность размещения NAND ячеек на кристалле. Но сигналы в структуре NAND в результате прохождения через несколько открытых транзисторов слабее, чем в NOR, что повышает требования к считывающим усилителям.

43

3.Микроконтроллер PIC16F873A

3.1.Общая характеристика PIC16F873A

Микроконтроллер PIC16F873A относится к среднему семейству восьмиразрядных микроконтроллеров PIC-micro, имеет гарвардскую RISC архитектуру. Микроконтроллеры семейства PIC16 различаются объемом внутренней памяти, а также набором и количеством периферийных устройств, но имеют одинаковое вычислительное ядро и одинаковую систему команд.

Микроконтроллеры PIC16F873A выпускаются в 28 выводных корпусах PDIP, SOIC, SSOP и QFP (рис. 3.1).

а |

б |

в |

Рис. 3.1. Корпуса микроконтроллеров:

а – PDIP; б – SOIC; в – QFP

Корпус PDIP (Plastic Dual In-line Package – пластиковый с двумя рядами выводов) представляет собой пластиковый прямоугольник с двумя рядами выводов по длинным сторонам, предназначенный для монтажа в отверстия печатной платы.

Корпус SOIC (Small-Outline Integrated Circuit – малогабаритная интегральная схема) также представляет собой прямоугольник с двумя рядами выводов и предназначен для поверхностного монтажа, габариты SOIC примерно в два раза меньше, чем у аналогичного PDIP корпуса.

Разновидностью SOIC является корпус SSOP (Shrink Small-Out- line Package – уменьшенный малогабаритный), имеющий еще меньшие габариты.

Корпус QFP (Quad Flat Package – квадратный тонкий) предназначен для поверхностного монтажа и представляет собой пластиковый квадрат, выводы которого расположены по периметру, за счет чего габариты корпуса меньше, чем у SSOP.

44

Назначение выводов микроконтроллера PIC16F873A для PDIP, SOIC и SSOP корпусов указано на рис. 3.2.

Рис. 3.2. Назначение выводов микросхемы PIC16F873A

Большинство выводов мультиплексировано, т. е. один вывод используется различными устройствами в зависимости от настроек.

Основные технические характеристики микроконтроллера PIC16F873A:

–количество машинных команд – 35;

–команды выполняются за 1 машинный цикл, за исключением команд перехода, которые выполняются за 2 цикла;

–тактовая частота до 20 МГц;

–объем FLASH памяти программ – 4096 14-разрядных слов;

–объем памяти данных – 192 байта;

–объем энергонезависимой памяти данных EEPROM – 128

байт;

–система прерываний включает 14 источников;

–8-уровневый аппаратный стек;

–прямой и косвенный режим адресации ячеек памяти данных;

–внутренняя схема сброса по включению питания (POR);

45

–сторожевой таймер WDT с собственным RC генератором;

–возможность программирования и отладки в готовом устройстве;

–широкий диапазон напряжений питания – от 2,0 до 5,5 В;

–малое энергопотребление – до 10 мА в рабочем режиме и

<1 мкА в режиме ожидания.

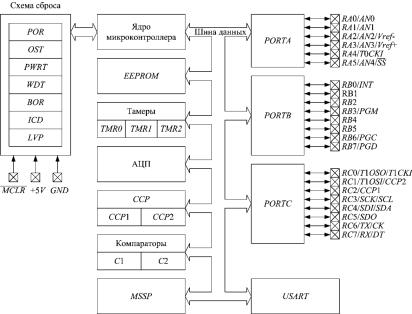

3.2. Структурная схема микроконтроллера

Микроконтроллер включает в себя вычислительное ядро и ряд периферийных модулей, связанных между собой 8-разрядной шинойданных.СтруктурнаясхемаPIC16F873A представленанарис.3.3.

Рис. 3.3. Структурная схема микроконтроллера PIC16F873A

Ядро микроконтроллера осуществляет выборку и исполнение команд из памяти программ, а также управление процессом вычисления.

46

Схема сброса (системный монитор) предназначена для приведения микроконтроллера в исходное состояние при включении электропитания (POR), просадке напряжения питания ниже заданного уровня (BOR), в случае зависания программы (WDT) или при подаче логического «0» на внешний вывод MCLR. Кроме того, схема сброса содержит таймер времени запуска тактового генератора (OST) и таймер времени установки напряжения питания (PWRT). Схема сброса также используется при внутрисхемной отладке управляющей программы (ICD) и при программировании микроконтроллера (LVP);

Параллельные порты ввода-вывода PORTA, PORTB и PORTC, предназначены для передачи воздействий объектам управления и получения информации от внешних устройств в параллельном виде. Порт А имеет шесть линий ввода-вывода (RA0...RA5), а порты В и С – по восемь (RB0...RB7 и RC0...RC7 соответственно). Большинство линий ввода-вывода имеют одну или две альтернативные функции и могут использоваться другими периферийными модулями.

Модуль последовательного порта ввода-вывода USART позволяет обмениваться информацией в последовательном виде с другими микропроцессорными системами через интерфейсы RS-232, RS-422 или RS-485.

Модуль ведущего синхронного последовательного порта (MSSP – Мaster Synchronous Serial Port), предназначен для передачи информации в последовательном виде, но в отличие от USART обмен выполняется внутри микропроцессорной системы. При этом используются интерфейсы SPI либо I2C.

Энергонезависимая память данных EEPROM служит для хранения данных, которые не должны стираться при выключении источника питания.

Три модуля таймеров TMR0, TMR1 и TMR2 позволяют аппаратно формировать интервалы времени. Таймеры TMR0 и TMR2 имеют 8-разрядный счетчик, а таймер TMR1 – 16-разрядный.

Модуль 10-разрядного аналого-цифрового преобразователя АЦП предназначен для преобразования аналоговых сигналов в цифровой вид.

Два модуля CCP (Capture, Compare, PWM) схем захвата, сравнения и широтно-импульсной модуляции (ШИМ) CCP1 и CCP2 могут работать в трех режимах. В режиме захвата модули позволяют сохранить в памяти микроконтроллера длительность вход-

47

ного сигнала. В режиме сравнения формируется сигнал на выходе микроконтроллера при достижении счетчиком таймера TMR1 определенного значения. В режиме ШИМ модуль ССР совместно с таймером TMR2 позволяет сформировать на выходе микроконтроллера импульсный широтно-модулированный сигнал.

Два аналоговых компаратора С1 и С2 позволяют производить попарное сравнение уровня четырех аналоговых сигналов.

3.3. Ядро микроконтроллера

Ядро микроконтроллера PIC16F873A состоит из блока выборки и блока исполнения (рис. 3.4).

Блок выборки выбирает команды из памяти программ и загружает их в конвейер. Адрес каждой извлекаемой команды задается счетчиком команд. Код операции, выделенный из кода команды, дешифратором активирует в требуемой последовательности соответствующие узлы исполнительного блока.

Основной элемент блока – это память программ, реализованная в виде ПЗУ. Память программ имеет страничную организацию, каждая страница содержит 2048 14-разрядных ячеек.

Счетчик команд (PC, Program Counter) представляет собой 13-разрядный регистр и используется для адресации (указания считываемой из памяти программ команды). Счетчик команд увеличивается на единицу после каждой выборки, а после сброса микроконтроллера обнуляется. Значение счетчика команд может быть изменено командами перехода или путем записи в младший байт счетчика команд.

Конвейер реализован в виде двух 14-разрядных регистров. В первом регистре хранится команда, только что считанная из памяти программ по адресу, определяемому счетчиком команд. Второй регистр подключен к дешифратору и содержит исполняемую

вданный момент команду. Такое решение позволяет осуществлять выборку команды одновременно с исполнением команды, выбранной в предыдущем цикле. Для команд, выполняющих переход к другому месту памяти программ, команда, находящаяся

впервом регистре конвейера, должна быть заменена на другую. Этот процесс называется сбросом конвейера и увеличивает время исполнения команды на один цикл.

48

49

Рис. 3.4. Ядро микроконтроллера PIC16F873A

Дешифратор команд представляет собой логическую схему, которая декодирует каждую команду и управляет передачей соответствующих адресов и данных на требуемые входы исполнительного блока, а также конфигурирует АЛУ.

Тактовый генератор задает последовательность выполнения внутренних микроопераций. В качестве времязадающего элемента используется внешний кварцевый резонатор, подключаемый к выводам OSC1 и OSC2 микроконтроллера. Максимальная тактовая частота работы микроконтроллера PIC16F873 составляет 20 МГц. Обычная команда (не изменяющая последовательность выполнения программы) выполняется за один машинный цикл. Машинный цикл состоит из 4 машинных тактов. Таким образом, максимальная производительность микроконтроллера составляет 4 миллиона операций в секунду.

Стек представляет собой блок из восьми 13-разрядных регистров, который подключен к счетчику команд и служит для запоминания адреса возврата из подпрограмм. Запись в стек происходит автоматически при выполнении команды вызова подпрограммы. Стек не доступен программно, нельзя записать в стек или считать его состояние.

Блок исполнения осуществляет извлечение данных из памяти данных или непосредственно из кода команды и выполняет обработку этого значения, используя АЛУ. Режим работы АЛУ определяется сигналами, формируемыми дешифратором команд. Результат выполнения операции помещается либо в рабочий регистр (W, WREG), либо обратно в память данных, перезаписывая исходное значение.

Основным элементом блока является АЛУ, которое осуществляет обработку данных, поступающих из двух источников. Одним из этих источников является 8-разрядный рабочий регистр. В качестве другого источника может выступать регистр данных или константа, которые содержатся в коде команды. В первом случае результат может быть помещен обратно в память, если бит d, содержащийся в команде, равен единице. Если бит d равен нулю, результат сохраняется в рабочий регистр (W, WREG).

Регистр состояния (STATUS) содержит три бита-флага, которые используются для указания свойств вычисленного результата. Флаг переноса (C, Carry) хранит бит переноса предыдущей операции сложения или инверсный бит заема при операции вычитания. Флаг десятичного переноса (DC, Digit Carry) устанавливается при

50