umm_7154

.pdf

1.4. Логические операции

Основными логическими операциями, реализуемыми микропроцессорами, являются операции И, ИЛИ, НЕ, исключающее ИЛИ.

Логическая операция И (конъюнкция, логическое умножение), обозначается знаком « ∙ » или « »:

F = X1 ∙ X2 ∙ X3 ∙ … ∙ Xn.

Логическая операция ИЛИ (дизъюнкция) обозначается знаком « + », « & » или « »:

F = X1 + X2 + X3 + … + Xn.

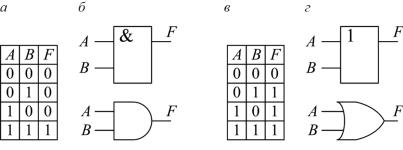

Таблица истинности для двух входных переменных и условное обозначение логической операции И представлены на рис. 1.1, а, б. Таблица истинности для операции ИЛИ двух переменных и условное обозначение представлены на рис. 1.1, в, г.

Рис. 1.1. Логические элементы И, ИЛИ:

а– таблица истинности И; б – условное обозначение элемента И

всхемах; в – таблица истинности ИЛИ; г – условное обозначение

элемента ИЛИ в схемах

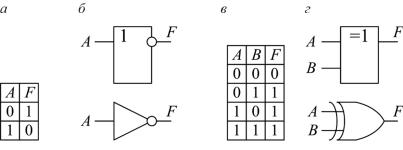

Логическая операция НЕ (инверсия) обозначается чертой над переменной, таблица истинности и условное обозначение представлены на рис. 1.2, а, б.

11

Рис. 1.2. Логические элементы НЕ, исключающее ИЛИ:

а– таблица истинности НЕ; б – условное обозначение элемента НЕ

всхемах; в – таблица истинности исключающее ИЛИ; г – условное обозначение элемента исключающее ИЛИ в схемах

Логическая операция исключающее ИЛИ (сложение по модулю 2) обозначается знаком « »:

F = X1 X 2 X 3 ... X n .

Таблица истинности и условные графические обозначения представлены на рис. 1.2, в, г.

1.5. Архитектура микропроцессорных систем

Архитектура микропроцессорной системы – абстрактное представление, отражающее ее структурную, схемотехническую и логическую организацию. Иными словами архитектура представляет собой совокупность идей, заложенных в микропроцессорную систему. Архитектурные особенности микропроцессорных систем характеризуются специальными терминами.

Первым фундаментальным трудом по архитектуре вычислительных машин считается работа Джона фон Неймана «Предварительное рассмотрение логической конструкции электронных вычислительных машин» («Preliminary discussion of the logical design of an electronic computing instrument»), впервые опубликованная в 1946 году. В работе систематизированы все накопленные к тому времени идеи и наработки, многие положения работы фон Неймана до сих пор актуальны.

12

Фон Нейман предложил структуру организации микропроцессорной системы с общей областью памяти для команд и данных, такую структуру называют архитектурой фон Неймана или принстонской архитектурой. Структура микропроцессорной системы с раздельными областями памяти для команд и данных носит название гарвардской архитектуры.

Взависимости от характеристик набора команд, архитектуры микропроцессоров делятся на RISC (Reduced Instruction Set Computer – компьютер с сокращенным набором инструкций) и CISC

(Complex Instruction Set Computer – компьютер с полным набором инструкций). Для CISC микропроцессоров характерно большое количество команд различной разрядности, выполняемых за разное число машинных циклов, RISC микропроцессоры характеризуются минимальным набором команд, занимающих одинаковое место в памяти, выполняемых за одинаковое время.

Впроцессе выполнения команд наиболее длительный этап – загрузка команд из памяти. Для повышения скорости выполнения программы команды вызываются из памяти заранее и помещаются в специальный регистр. Такой способ носит название конвейерной обработки команд. Таким образом, команда перед выполнением считывается не из памяти, а из регистра конвейера. Одновременно с выполнением команды в конвейер из памяти программ загружается следующая команда. В процессорах с высокой производительностью процесс выполнения команды делится на несколько этапов. В этом случае одновременно выполняется несколько команд в разной степени готовности, время на выполнение команд сокращается. Микропроцессоры, обладающие одним конвейером, имеют скалярную архитектуру. Микропроцессоры, с числом конвейеров более одного, имеют суперскалярную архитектуру.

Повышение скорости выполнения программы при конвейерной обработке достигается только тогда, когда точно известна следующая выполняемая команда. Любой процессор имеет ряд команд, называемых командами перехода, изменяющих последовательность выполнения программы. Время выполнения команд перехода увеличивается из-за необходимости очищать конвейер для загрузки команды по адресу, указанному командой перехода.

13

2. Элементы микропроцессорных систем

2.1. МОП-транзисторы

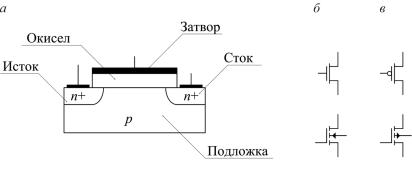

Основным элементом сверхбольших интегральных микросхем в настоящее время является полевой транзистор со структурой ме- талл-окисел-полупроводник (МОП-транзистор или MOS-FET – Metal-Oxide-Semiconductor Field-Effect Transistor). Принцип работы полевого транзистора впервые предложен Лилиенфельдом и Хейлом в начале 30-х годов прошлого века. Устройство и условные графические обозначения МОП-транзисторов представлены на рис. 2.1.

Рис. 2.1. МОП-транзистор:

а– устройство; б – условное обозначение n-МОП транзисторов;

в– условное обозначение p-МОП транзисторов

Транзистор состоит из полупроводниковой подложки p-типа, в которой сформированы две высоколегированные n-области – сток (source) и исток (drain). Металлический электрод, отделенный от подложки слоем окисла, называется затвором (gate).

Когда напряжение на затворе отсутствует, электрическая цепь исток-сток представляет собой два p-n перехода, включенных навстречу друг другу. При этом транзистор закрыт, ток в цепи равен току обратно смещенного перехода. Если на затвор подать положительный по отношению к подложке потенциал, то электроны подтягиваются к затвору, образуя между стоком и истоком прово-

14

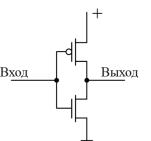

дящий канал, – транзистор открыт. Проводимость этого канала зависит от величины напряжения на затворе. Если изменить тип проводимости стока и истока, а на затвор подать отрицательный потенциал, то проводящий канал образуют дырки. В зависимости от типа проводящего канала транзисторы обозначаются n-МОП или p-МОП. Если соединить между собой затворы двух МОП транзисторов p- и n-типа, то получится элемент КМОП (CMOS), представляющий собой инвертор (рис. 2.2).

Рис. 2.2. КМОП-элемент

Высокий уровень сигнала на входе КМОП-пары открывает нижний транзистор, верхний транзистор при этом закрыт. На выходе появляется низкий уровень сигнала. Соответственно низкий уровень на входе открывает верхний транзистор, и на выходе появляется 1. Важное достоинство КМОП – малая мощность потребления, поскольку ток протекает через элемент только в процессе переключения.

2.2. Сумматоры

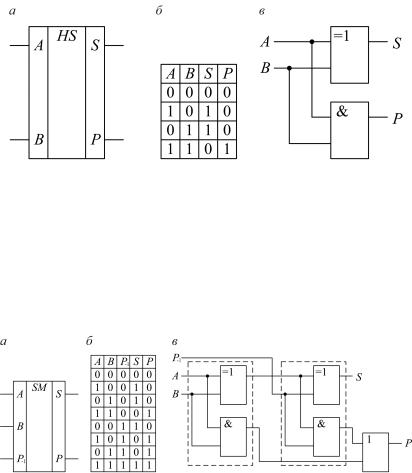

Сумматор – комбинационное устройство, предназначенное для выполнения операции арифметического сложения чисел. Сумматоры используются в операциях сложения и вычитания, а также составляют основу устройств умножения и деления. Простейший сумматор вычисляет сумму двоичных разрядов A и B, определяет признак переноса в старший разряд P. Такое устройство получило название двоичного одноразрядного полусумматора (рис. 2.3). Полусумматор не учитывает возможность переноса из младшего разряда P-1.

15

Рис. 2.3. Двоичный одноразрядный полусумматор:

а– условное обозначение; б – таблица истинности;

в– принципиальная схема

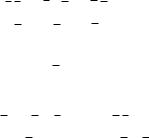

Как видно по таблице истинности, S реализуется как логическая функция Исключающее ИЛИ над входными операндами, а P – как функция И. Реализация полного двоичного одноразрядного сумматора представлена на рис. 2.4.

Рис. 2.4. Двоичный одноразрядный сумматор:

а– условное обозначение; б – таблица истинности;

в– принципиальная схема

Одноразрядные сумматоры имеют три входа и два выхода. Запишем в дизъюнктивной совершенной нормальной форме функции S и P по таблице истинности (рис. 2.4, б):

16

S = ABP−1 + ABP−1 + ABP−1 + ABP−1;

P = ABP−1 + ABP−1 + ABP−1 + ABP−1.

Если для S вынести P-1 и P−1 за скобки, а для P за скобки вынести AB, то получим

S = P−1(AB + AB) + P−1(AB + AB);

P= AB(P−1 + P−1 ) + P−1(AB + AB).

Впервых скобках выражения для S содержится функция равнозначности (Исключающее ИЛИ), во второй скобке инверсия функции равнозначности. Первая скобка выражения для P равна 1, вторая содержит функцию равнозначности. Таким образом, окончательно получим

|

|

|

|

|

|

S = P−1(A B) + P−1(A B) = A B P−1; |

(2.1) |

||||

|

|

P = AB + P−1(A B). |

(2.2) |

||

Схема полного сумматора, реализованного по полученным выражениям, состоит из двух схем полусумматоров (на рис. 2.4, в показано пунктиром) и элемента ИЛИ.

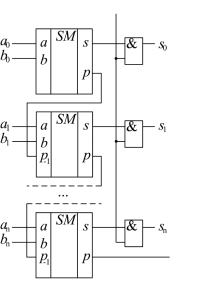

Сумматоры для сложения многоразрядных двоичных чисел строятся путем параллельного или последовательного соединения одноразрядных сумматоров.

В последовательных сумматорах слагаемые последовательно подаются на входы единственного одноразрядного сумматора, обрабатывающего операнды поочередно разряд за разрядом. Результаты суммирования последовательно считываются с соответствующего выхода, а выработанный перенос учитывается при сложении следующего разряда операндов. В результате сложения младшего разряда вырабатывается сумма и перенос, который запоминается на один такт. В следующем такте складываются вновь поступившие разряды с учетом сохраненного переноса из младшего разряда, и получается следующий разряд суммы и перенос. Суммирование выполняется аналогично для всех разрядов операндов.

При сложении n-разрядных двоичных чисел может использоваться каскадное соединение n одноразрядных сумматоров. По-

17

скольку переносы передаются от сумматора к сумматору, такая конфигурация называется сумматором с последовательным переносом. Сумматоры с последовательным переносом строятся как цепочка одноразрядных сумматоров, соединенных последовательно по цепям переноса (рис. 2.5).

Синхронизация

Выходной

перенос

Рис. 2.5. Параллельный сумматор с последовательным переносом

Все разряды операндов подаются на входы сумматора одновременно, но сигнал переноса из разряда в разряд формируется предыдущим одноразрядным сумматором, причем каждый последующий сумматор выполняет операцию после формирования результата во всех предыдущих разрядах. Поэтому длительность сложения пропорциональна количеству разрядов в слагаемых.

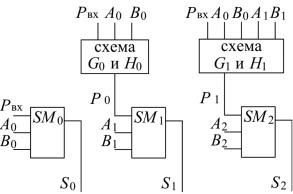

Задержка получения результата может быть сокращена за счет изменения схемы переноса. Идея заключается в вычислении переноса для каждого разряда по всем переменным, от которых зависит его наличие. Устройство, формирующее сигналы переноса непосредственно из значений входных переменных, называют блоком ускоренного переноса. Выход переноса одноразрядных сумматоров в этом случае не используется.

18

Разберем подробнее процедуру синтеза блока ускоренного переноса. Выполним замену переменных в выражении (2.2):

P = G + P–1H,

где G = AB – функция генерации;

H = A B – функция прозрачности.

Таким образом, выходной перенос появляется только в случаях, когда функция генерации равна 1, либо имеется входной перенос и функция прозрачности равна 1, либо выполняются оба условия. Функция генерации принимает единичное значение, если перенос на выходе данного разряда появляется независимо от наличия или отсутствия входного переноса. Функция прозрачности принимает единичное значение, если перенос на выходе данного разряда появляется только при наличии входного переноса. Другими словами, перенос либо генерируется самим разрядом, либо пропускается через него.

Функцию прозрачности обычно реализуют как логическую операцию ИЛИ, поскольку случай, когда оба входных операнда равны 1, учитывает функция генерации. Перенос на выходе младшего разряда можно вычислить следующим образом:

P0 = G0 + PвхH0.

Аналогичным образом для переноса P1 на выходе следующего разряда справедливо выражение

P1 = G1 + P0H1.

Подставив выражение для переноса на выходе младшего разряда, получим

P1 = G1 + G0H1 + PвхH1H0.

Структурная схема сумматора с параллельным переносом представлена на рис. 2.6.

19

Рис. 2.6. Структурная схема сумматора с параллельным переносом

Рассмотренные сумматоры с параллельным переносом имеют преимущества при числе складываемых разрядов от 4 до 8. При числе разрядов, меньше 4, преимущество имеют сумматоры с последовательным переносом, при числе разрядов, более 8, блок ускоренного переноса сильно усложняется. Для суммирования многоразрядных чисел применяются сумматоры с групповой структурой, в которых все разряды операндов делятся на группы.

2.3. Арифметико-логические устройства

Арифметико-логическое устройство (АЛУ, ALU – Arithme- tic-Logic Unit) представляет собой схему, выполняющую определенный набор арифметических и логических операций над входными данными в соответствии со значением на входах выбора режима. Основой АЛУ служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности и обеспечивающей выбор выполняемой операции. АЛУ – один из основных узлов любого микропроцессора.

Также АЛУ выпускаются в виде микросхем, например 74LS381 (К555ИП3), 74LS382, которые устроены аналогично АЛУ микропроцессоров.

Микросхема 74LS382, показанная на рис. 2.7, выполняет 8 операций над двумя 4-разрядными числами. Выполняемая операция задается трехразрядной комбинацией выбора режима S0S1S2 (рис. 2.7, а).

20