umm_7154

.pdf

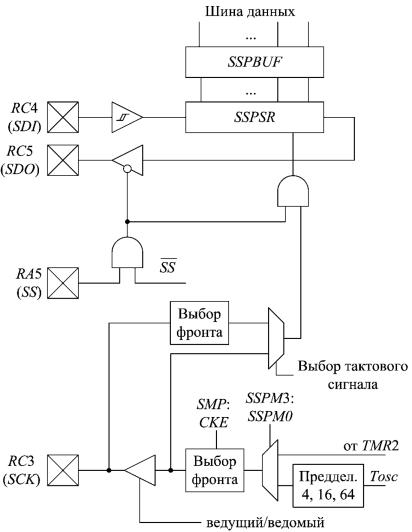

Рис. 3.18. Структурная схема модуля MSSP в режиме SPI

91

3.26. Модули захват/сравнение/ШИМ

Микроконтроллер PIC16F873A имеет два модуля CCP (Capture/Compare/PWM), осуществляющих захват содержимого TMR1, сравнение содержимого TMR1 с заданным числом, либо широт- но-импульсную модуляцию с помощью таймера TMR2.

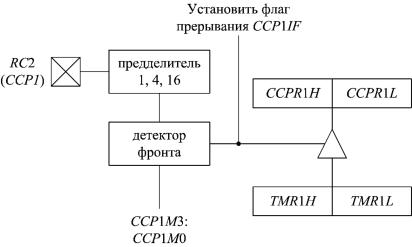

Структурная схема модуля CCP1 в режиме захвата представлена на рис. 3.19.

Рис. 3.19. Структурная схема модуля CCP в режиме захвата

Событие захвата может возникнуть по заднему фронту импульса на входе RC2 (CCP1), по переднему фронту импульса на входе, по каждому 4 переднему фронту импульса на входе, либо по каждому 16 переднему фронту импульса на входе. Выбор события, при котором происходит захват, осуществляется битами CCP1M0, CCP1M1, CCP1M2 и CCP1M3 в регистре CCP1CON. При возникновении события захвата данные из 16-разрядного регистра TMR1 копируются в регистры CCPR1H и CCPR1L. После чего устанавливается флаг CCP1IF в регистре PIR1 и выполняется прерывание, если оно разрешено.

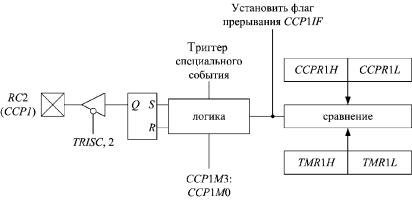

Структурная схема CCP1 в режиме сравнения представлена на рис. 3.20.

92

Рис. 3.20. Структурная схема модуля CCP в режиме сравнения

В момент совпадения значения, записанного в регистры CCPR1H и CCPR1L с числом в регистре TMR1, схема сравнения устанавливает флаг CCP1IF в регистре PIR1. В зависимости от режима работы, настраиваемого битами CCP1M0, CCP1M1, CCP1M2

иCCP1M3 в регистре CCP1CON, логическая схема воздействует на RS-триггер. Сигнал с выхода триггера поступает вывод RC2 (CCP1) микроконтроллера. Триггер специального события сбрасывает значения таймера TMR1 при каждом выполненном сравнении.

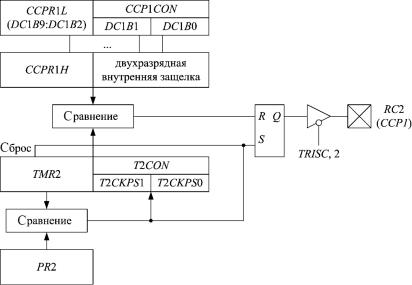

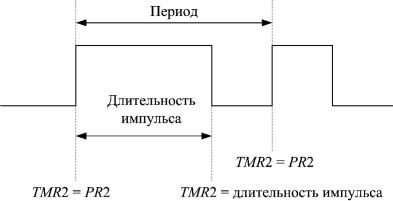

Режим ШИМ (PWM), также реализуемый с помощью модуля CCP, обеспечивает генерацию сигналов с широтно-импульсной модуляцией. Структурная схема CCP1 в ШИМ режиме представлена на рис. 3.21.

Таймер TMR2 вместе с предделителем образуют 10-разрядный счетчик, который формирует ШИМ сигнал. Его значение непрерывно сравнивается с содержимым регистра PR2, и при совпадении значений схема сравнения формирует сигнал сброса таймера. Параллельно функционирует контур сравнения, включающий в себя таймер, вторую схему сравнения и регистр CCPR1H. Обе схемы сравнения управляют RS-триггером, выход которого подключен к выводу RC2 (CCP1) микроконтроллера.

Когда значение регистра TMR2 сравнивается с числом, записанным в PR2, соответствующая схема сравнения сбрасывает TMR2

иустанавливает триггер в единичное состояние. На выводе RC2 (CCP1) появляется высокий логический уровень. Одновременно

93

Рис. 3.21. Структурная схема модуля CCP в режиме ШИМ

с этим содержимое CCPR1L переписывается в регистр CCPR1H,

акогда значение TMR2 сравнивается со значением CCPR1H, схема сравнения сбрасывает триггер и на выводе RC2 (CCP1) появляется низкий логический уровень. Изменяя значения в регистре CCPR1L можно управлять скважностью формируемых импульсов. Временная диаграмма работы модуля CCP в режиме ШИМ представлена на рис. 3.22.

При задании периода учитываются только 8 разрядов TMR2,

апри задании длительности импульса – все 10 разрядов TMR2 и предделителя, которые сравниваются с содержимым 10-разрядно- го регистра, образованного «склеиванием» содержимого регистра CCPR1H и двухразрядной внутренней защелкой. Если длительность импульса ШИМ больше периода, на выводе RC2 (CCP1) не будет устанавливаться сигнал низкого уровня.

94

Рис. 3.22. Временная диаграмма работы модуля CCP в режиме ШИМ

3.27. Модуль аналогово-цифрового преобразователя

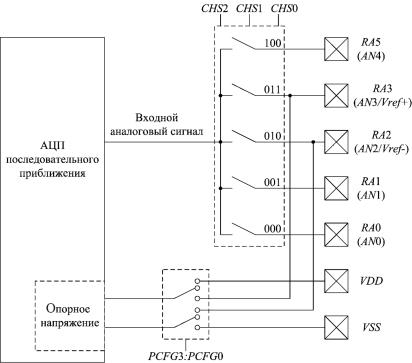

Микроконтроллер PIC16F873A имеет пятиканальный 10-раз- рядный аналогово-цифровой преобразователь (АЦП, ADC – Ana- log-to-Digital Converter), работающий по методу последовательного приближения. Структурная схема модуля АЦП представлена на рис. 3.23.

Измеряемое напряжение подается на аналоговые входы AN4, AN3, AN2, AN1 и AN0, совмещенные с выводами параллельного порта A. Выбор конкретного входа осуществляется мультиплексором, на управляющие входы которого подается комбинация, установленная битами CHS0, CHS1 и CHS2 регистра ADCON0. В качестве опорного напряжения, с величиной которого сравнивается входной аналоговый сигнал, используется напряжение питания микроконтроллера (VDD, VSS), либо напряжение от источника, подключенного к выводам Vref+ и Vref- микроконтроллера. Выбор источника опорного напряжения осуществляется битами

PCFG0…PCFG3 регистра ADCON1.

Преобразование начинается после установки в 1 бита GO/-DO- NE в регистре ADCON0. По окончании преобразования этот бит автоматически сбрасывается в 0, а бит ADIF в регистре PIR1 устанавливается в 1.

95

Рис. 3.23. Структурная схема модуля АЦП

Полученный после выполнения преобразования цифровой 10-разрядный код с выхода АЦП записывается в 16-разрядный регистр результата, состоящий из регистров ADRESH и ADRESL. Состояние бита ADFM регистра ADCON1 позволяет выравнивать результат слева (ADFM = 0) и справа (ADFM = 1). Выравнивание слева предполагает, что 8 старших разрядов результата размещаются в регистре ADRESH, а два оставшихся – в регистре ADRESL. При выравнивании справа младшие 8 бит помещаются в ADRESL, а два старших – в ADRESH.

96

4. Тенденции и перспективы развития микропроцессорной техники

4.1. Программируемые логические интегральные схемы

Программируемые логические интегральные схемы (ПЛИС) состоят из функциональных логических блоков, которые связаны в единое целое программируемой матрицей связей или системой межсоединений. Функциональные логические блоки содержат программируемую таблицу истинности, один или несколько триггеров и управляющие цепи. При разработке устройств выполняется конфигурация матрицы связей (межсоединений) для получения требуемой структуры устройства и программирование логических блоков. Конфигурационные данные хранятся в специально предназначенной для этого области памяти внутренней или внешней в зависимости от типа ПЛИС.

Широкое распространение получили сложные программируемые логические устройства (CPLD, Complex Programmable Logic Device) и программируемые пользователем вентильные матрицы (FPGA, Field Programmable Gate Arrays). Микросхемы CPLD имеют относительно простую структуру и внутреннюю область памяти для хранения конфигурации программируемой матрицы межсоединений. Микросхемы FPGA характеризуются регулярной структурой, за счет чего обладают близкой к максимальной степенью интеграции. Конфигурация FPGA хранится во внешней памяти.

Таким образом, микросхемы ПЛИС позволяют создавать цифровые автоматы практически любой сложности. Для разработки устройств на ПЛИС используются языки описания аппаратуры (например, Verilog, VHDL). Описания готовых устройств и отдельных функциональных модулей (Soft-ядра) представляют собой самостоятельный интеллектуальный продукт. Иначе говоря, существует отдельный рынок устройств, описанных на языках VHDL и Verilog.

Микропроцессоры, являясь цифровыми автоматами, также могут представлять собой Soft-ядра (Soft-микропроцессоры), разработанные на языках описания аппаратуры. Данный подход позволяет создавать на одной микросхеме устройство, содержащее микропроцессор, набор периферийных модулей и нестандарт-

97

ные цифровые автоматы. Конфигурация такого устройства может быть легко изменена.

Внастоящее время более 85% рынка ПЛИС делят компании Altera и Xilinx. По данным Xilinx, в 2012 году на долю Altera пришлось 39% рынка, а объемы Xilinx составили 49%.

4.2.Микросхемы FPGA Xilinx серии Spartan

Всемейство Spartan-6 входит 13 микросхем, плотность интеграции которых составляет от 3840 до 147443 эквивалентных логических ячеек.

Микросхемы ПЛИС Spartan-6 содержат конфигурируемые логические блоки (CLB, Configurable Logic Block), буферы ввода-вы- вода (IOB, Input/Output Buffers), 18 Кб блоки оперативной памяти, блоки цифровой обработки сигналов (ЦОС – DSP, Digital Signal Processing), блоки управления тактовой частотой (CMT, Clock Management Tile), контроллеры SDRAM памяти, высокоскоростной последовательный передатчик и контроллер PCI Express.

4.3.Микросхемы CPLD Altera серии MAX

Производимые компанией Altera микросхемы серии MAX-V относятся к типу CPLD. Всего производится 7 типов микросхем с плотностью интеграции от 40 до 2210 логических элементов.

Микросхемы MAX-V имеют двумерную архитектуру столбцов и строк содержащих логические блоки. Связь между логическими блоками обеспечивается матрицей межсоединений. Каждый блок логического массива состоит из 10 логических элементов. Логический элемент является минимальной единицей логики и обеспечивает выполнение реализуемых логических функций.

4.4. Разработка программ для микроконтроллеров на языках высокого уровня

Запасы производительности и ресурсов современных периферийных микроконтроллеров позволяют разрабатывать программы на языках высокого уровня. На сегодняшний день для разработки программ микроконтроллеров семейства PIC существует ряд языков программирования, для которых разработаны компиляторы. Существуют компиляторы языков программиро-

98

вания PASCAL, BASIC и другие, но наиболее популярным языком для программирования микроконтроллеров является язык C. Этот язык требует большего, чем язык ассемблера количества ресурсов, но позволяет создавать более удобные для понимания программы. Разработка программ на Си выполняется быстрее, а разобраться в их исходном коде проще.

Для программирования на С используется ряд конструкций и операторов, которые преобразуются специальной программой, называемой компилятором, в машинные команды. На сегодняшний день существуют несколько С-компиляторов для микроконтроллеров PIC, наиболее популярные из них Hi-tech PICC, MPLAB XC Compiler, microC, IAR C Compiler. Компиляторы устанавливаются отдельно, после чего работа с ними доступна из среды MPLAB.

Любая конструкция языка С состоит из одного или нескольких мнемокодов, поэтому программа на C всегда занимает в памяти микроконтроллера больше места, по сравнению с программой на языке ассемблера. Файлы с исходным текстом на языке Си обычно имеют расширение *.c.

Программа на языке C представляет собой набор подпрограммфункций. Выполнение любой программы начинается с выполнения функции main(), поэтому она является обязательной.

Данные в языке Си делятся на типы, причем тип данных конкретной переменной должен объявляться заранее. Преобразование данных выполняется операторами и специальными управляющими конструкциями.

99

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1.Аналоговая и цифровая электроника (полный курс): учеб. для вузов / Под ред. О. П. Глудкина. – М.: Горячая линияТелеком, 2005. – 768 с.

2.Дубров И. А. Основы микропроцессорной техники : учеб.- метод. пособие / И. А. Дубров, М. Ю. Белошицкий, А. Н. Попов. – Екатеринбург : Изд-во УрГУПС. – 2012. – 99,[1] с.

3.Катцен С. PIC-микроконтроллеры. Полное руководство. / С. Катцен; пер. с англ. Евстифеева А. В. – М.: Додэка-XXI, 2010. – 656 c.

4.Кораблев Е. А. Основы микропроцессорной техники : учеб. пособие. – Екатеринбург : Изд-во УМЦ УПМ. – 2003. – 104 с.

5.Лебедев О. Н. Применение микросхем памяти в электронных устройствах: справочное пособие. – М.: Радио и связь, 1994. – 216 с.

6.Магда Ю. С. Микроконтроллеры PIC: архитектура и программирование. – М.: ДМК Пресс, 2009. – 240 с.

7.Нарышкин А. К. Цифровые устройства и микропроцессоры: учеб. пособие для студ. высш. учеб. заведений / А. К. Нарышкин. – М.: Издательский центр «Академия», 2006. – 320 с.

8.Новиков А. А. Имитационное моделирование дискретных устройств : учеб.-метод. пособие / А. А. Новиков, М. Ю. Белошицкий. – Екатеринбург : Изд-во УрГУПС, 2013. – 100 с.

9.Новиков Ю. В. Основы микропроцессорной техники: учеб. пособие / Ю. В. Новиков, П. К. Скоробогатов. – 3-е изд., испр. – М.: Интернет-Университет информационных технологий; БИНОМ, 2006. – 359 с.

10.Предко М. PIC-микроконтроллеры: архитектура и программирование пер. с англ. – М.: ДМК Пресс, 2010. – 512 с.

11.Угрюмов Е. П. Цифровая схемотехника: учеб. пособие для вузов. – 3-е. изд., перераб. и доп. – СПб.: БХВ-Петербург, 2010. – 816 с.

12.Чижма С. Н. Электроника и микросхемотехника: учеб. пособие. – М.: ФГБОУ «УМЦ ЖДТ», 2012. – 359 с.

13.Яценков В. С. Микроконтроллеры Microchip. Практическое руководство – Москва: Горячая линия-Телеком, 2002. – 296 с.

100