umm_7154

.pdf

а |

б |

|

|

Операнд А |

Результат |

|

Операнд В |

|

|

Выбор |

|

|

режима |

Переполнение |

|

|

|

|

Вход |

Выход |

|

переноса |

переноса |

|

Рис. 2.7. Микросхема АЛУ 74LS382: |

|

|

а – таблица функций; б – условное обозначение |

|

Кроме сложения и вычитания микросхема выполняет операции И, ИЛИ, Исключающее ИЛИ, формирует признак переполнения.

2.4. Дешифраторы. Мультиплексоры

Дешифратор – комбинационное устройство для распознавания различных кодовых комбинаций. На входы дешифратора подается кодовая комбинация, в зависимости от которой на одном из выходов устанавливается 1. Состояние остальных выходов равно 0. В микропроцессорных системах дешифраторы используются для выборки ячеек адресных запоминающих устройств и декодирования кодов команд.

Мультиплексор – комбинационное устройство, осуществляющее подключение одного из нескольких входов к единственному выходу под управлением входов выбора данных.

2.5. Триггеры

Триггер – устройство, имеющее два устойчивых состояния и предназначенное для хранения одного двоичного разряда. Триггер состоит из бистабильной ячейки и схемы управления. Бистабильная ячейка состоит из двух замкнутых в кольцо инверторов так, что выход одного соединен с входом другого.

21

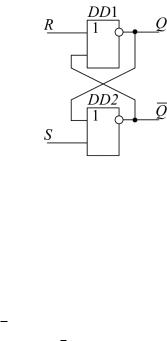

Простейший триггер представляет собой бистабильную ячейку с управляющими входами установки (R) и сброса (S). Устройство носит название асинхронного RS-триггера (рис. 2.8).

Рис. 2.8. Асинхронный RS-триггер

При включении питания логических элементов ИЛИ-НЕ и отсутствии сигналов на управляющих входах триггер принимает одно из двух устойчивых состояний, в зависимости от того, какой из логических элементов начнет переключаться раньше. Если на оба входа подан низкий уровень сигнала, триггер сохраняет свое состояние.

При установке S = 1 и R = 0 на выходах триггера появится комбинация Q = 1, Q = 0. Когда S = 0 и R = 1, выходы триггера устано-

вятся в состояние Q = 0, Q = 1, т. е. активным входным сигналом является 1. Подача единиц на оба входа одновременно приведет к появлению нулей на обоих выходах, это запрещенная входная комбинация. Если с входов одновременно снять единицы, триггер примет одно из устойчивых состояний, определяемое элементом, который начнет переключение раньше.

RS-триггер на элементах И-НЕ отличается тем, что активным входным сигналом является 0, а хранение значения триггером реализуется при двух единицах на входах.

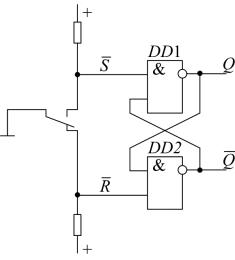

В микропроцессорных системах RS-триггеры используются как запоминающие элементы статической оперативной памяти. Также RS-триггеры могут использоваться для ввода логических сигналов от кнопок и контактов реле в микропроцессорную систему. Триггер на рис. 2.9 служит для подавления дребезга кон-

22

тактов, при замыкании которых происходит их многократное за- мыкание-размыкание.

Рис. 2.9. Подавление дребезга механических контактов

Установка триггера происходит при замыкании общего и фронтового контактов, а при размыкании состояние триггера не изменяется, благодаря чему пульсации на выходе схемы отсутствуют. При замыкании общего и тылового контактов схема работает аналогично, но происходит сброс триггера.

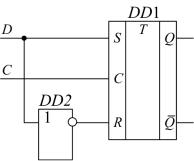

Дальнейшим развитием RS-триггера является триггер типа D (delay – задержка), который имеет один информационный вход и по тактовому сигналу переписывает состояние этого входа на выход (рис. 2.10).

В иностранной литературе D-триггер с управлением по уровню тактового сигнала носит название защелка (latch), триггером (flip-flop) называют устройство, управляемое фронтом тактового сигнала.

Триггеры D-типа являются основой для построения регистров сдвига, которые служат для хранения данных и преобразования последовательных данных в параллельные и обратно.

23

Рис. 2.10. D-триггер

Используемые в схемах счетчиков триггеры типа T (Toggle – переключатель) имеют только один вход. В момент поступления управляющего сигнала состояние T-триггера изменяется на противоположное.

Все рассмотренные типы триггеров можно реализовать на основе универсального триггера типа JK. Для установки триггера требуется на вход J подать 1, для сброса – подать 1 на вход K. Одновременная подача единиц на оба входа изменяет состояние JK- триггера на противоположное.

2.6. Регистры. Счетчики. Делители частоты

Регистр – устройство, предназначенное для хранения многоразрядного двоичного числа. Регистр представляет собой упорядоченную последовательность D-триггеров. Загрузка данных в регистр может осуществляться одновременно для всех разрядов или поразрядно. В первом случае устройство носит название регистра с параллельной загрузкой, во втором – регистра с последовательной загрузкой. Выгрузка данных также выполняется параллельно или последовательно. Регистры с параллельной загрузкой и последовательной выгрузкой данных используются в передатчиках последовательных интерфейсов, а регистры с последовательной загрузкой и параллельной выгрузкой – в приемниках. На основе регистров строятся порты ввода-вывода.

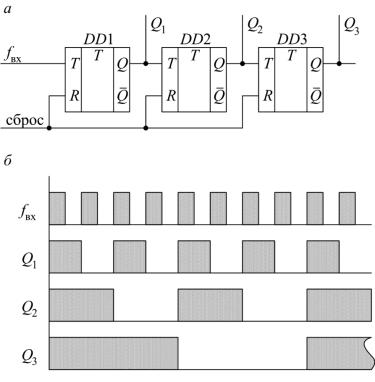

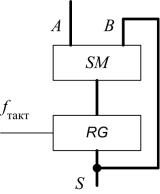

Счетчик – устройство, реализующие счет количества входных импульсов и фиксирующее полученный результат в двоичном коде. Счетчик (рис. 2.11, а) состоит из нескольких последо-

24

вательно включенных T-триггеров. Временные диаграммы (рис. 2.11, б) поясняют работу счетчика.

Рис. 2.11. Трехразрядный счетчик:

а – принципиальная схема; б – временная диаграмма работы

Комбинация на выходах Q1 – Q3 счетчика соответствует количеству поступивших на вход первого триггера импульсов. На выходе Q1 фиксируется младший разряд, на Q3 – старший. Счетчик обнуляется при переполнении или при подаче 1 на входы R всех триггеров. Переполнение наступает после подачи импульса на вход T первого триггера, когда на всех выходах установлена единица.

Как видно по диаграмме (рис. 2.11), частота импульсов на выходе T-триггера в два раза меньше частоты на его входе. Это свойство используется для деления частоты.

25

2.7. Аккумулятор

Аккумулятором называется регистр, вход которого соединен с выходом сумматора, а выход регистра используется как один из входных операндов сумматора (рис. 2.12).

Рис. 2.12. Аккумулятор

При поступлении импульса тактовой частоты результат сложения помещается в регистр и автоматически устанавливается в качестве одного из операндов. Такое устройство позволяет накапливать результат сложения.

Если вместо сумматора подключить АЛУ, как сделано в большинстве микропроцессоров и микроконтроллеров, то это позволит аккумулятору накапливать результат нескольких различных последовательных операций.

В микропроцессорах и микроконтроллерах аккумулятор совместно с АЛУ вместо сумматора является основным устройством для обработки данных. В некоторых реализациях микропроцессоров аккумулятор называют рабочим регистром (Work register,

WREG).

2.8. Тактирование и синхронизация

Функционирование микропроцессорных систем определяется порядком выполнения операций. Нарушение такого порядка приводит к сбоям и «зависаниям» процессора, неправильному

26

выполнению операций. Для обеспечения порядка срабатывания логических схем процессора выполняется тактирование внутренних элементов и синхронизация процессов обработки информации. Для формирования сигналов тактирования и синхронизации применяются тактовые генераторы на основе кварцевых резонаторов или в некоторых случаях RC-цепей. Кварцевые резонаторы обладают высокой добротностью, что позволяет обеспечить стабильность частоты. Генераторы с RC-цепочками применяются в основном на низких частотах, когда требуется обеспечить малое энергопотребление и низкую стоимость устройства.

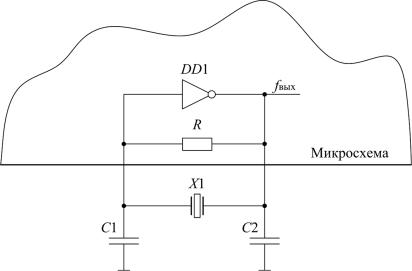

Наиболее распространенный тактовый генератор представляет собой генератор Пирса (рис. 2.13).

Рис. 2.13. Генератор Пирса

Основу генератора Пирса составляет инвертор DD1. За счет обратной связи, созданной резистором R, инвертор работает в линейном режиме и представляет собой инвертирующий усилитель, сдвигающий входной сигнал на 180о. Подключенный параллельно резистору, кварцевый резонатор X1, сопротивление которого является реактивным, сдвигает сигнал еще на 180о. За счет чего обеспечивается баланс фаз (фаза напряжения обратной связи совпа-

27

дает с фазой входного напряжения). Инвертирующий усилитель компенсирует потери в цепи обратной связи, что обеспечивает баланс амплитуд и возбуждение генератора. Высокая добротность кварцевого резонатора обеспечивает стабильность частоты генерируемого синусоидального сигнала. Конденсаторы C1 и C2 вместе с емкостью схемы, подключенной к выходу генератора, являются нагрузкой инвертора. Емкости C1 и C2 примерно равны, их изменение позволяет регулировать частоту выходного сигнала в некотором достаточно узком диапазоне.

Для работы логических схем требуются тактовые импульсы прямоугольной формы, получить которые можно с помощью компаратора, установленного на выходе генератора.

2.9. Входы и выходы микросхем

Микропроцессорная система должна обеспечивать ввод и вывод информации. Непосредственно с внешними цепями взаимодействуют входы и выходы микросхемы, которые имеют различное устройство и особенности подключения.

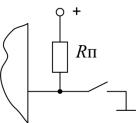

Подключать кнопки и контакты реле следует по схеме с подтягивающим резистором (рис. 2.14).

Рис. 2.14. Подтягивающий резистор

Такой резистор используется для того, чтобы гарантировать высокий логический уровень на входе порта при разомкнутом контакте и низкий логический уровень при замкнутом контакте, исключив состояние, когда вход «висит в воздухе».

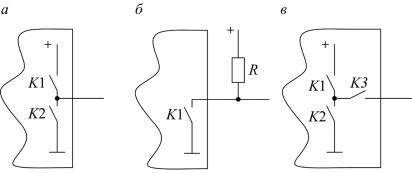

Выходные каскады микросхем имеют три разновидности (рис. 2.15):

– логические или выходы с двумя состояниями;

28

–открытые выходы (с открытым стоком, открытым коллектором);

–выходы с третьим состоянием.

Рис. 2.15. Выходы микросхем:

а – логический; б – открытый; в – с тремя состояниями

Логический выход (рис. 2.15, а) формирует два уровня напряжения. При замыкании ключа K1 на выходе формируется 1, при замыкании ключа K2 – 0. Ключи логического выхода должны иметь малое сопротивление для перезаряда емкостей при переключениях, что позволяет получить высокое быстродействие. При одновременном замыкании ключей к выходу подключаются высокий и низкий уровни сигнала, т. е. появляется состояние логической неопределенности. Кроме того, одновременное замыкание обоих ключей может вызвать повреждение выхода ввиду малого сопротивления цепи. Поэтому такая ситуация в пределах одного выхода исключается схемой управления ключами. По той же причине логические выходы нельзя соединять параллельно.

Открытый выход (рис. 2.15, б) обеспечивает напряжение низкого уровня, а при размыкании ключа состояние выхода не определено. Для формирования высокого уровня напряжения при размыкании ключа к выходу требуется подключать внешние резисторы, соединенные с источником питания. Несколько открытых выходов можно соединять, подключая их к общей для всех выходной цепи. Выходы с открытым стоком защищены от повреждений при параллельном включении, но имеют большую задержку

29

при переключении из 0 в 1, так как резистор ограничивает ток заряда емкости выхода.

У выходов с третьим состоянием (рис. 2.15, в), ключи могут замыкаться по очереди, как у логического выхода, а могут отключаться от внутренних схем третьим ключом, как у открытых входов. Состояние, когда внутренние цепи микросхемы отключены от выходов, называется высокоимпедансным, третьим, или Z-состоянием.

2.10. Классификация запоминающих устройств

Запоминающие устройства служат для хранения программ и данных в микропроцессорных системах. По способу доступа различают последовательную, адресную и ассоциативную память. Ниже рассматриваются только последовательная и адресная память, так как ассоциативная память в микроконтроллерах практически не нашла применения.

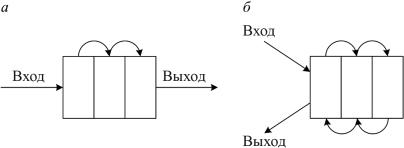

В последовательную память (рис. 2.16) данные записываются друг за другом и образуют очередь.

Рис. 2.16. Последовательная память: а – буферная; б – стековая

Последовательная память классифицируется в соответствии с принципом считывания данных. Память, использующая принцип FIFO (First In First Out – первым вошел – первым вышел) или принцип очереди, когда считывание данных выполняется в порядке записи, называется буферной. Если память использует принцип LIFO (Last In First Out – последним вошел – первым вышел)

30