- •Курс лекций

- •Наноэлектронные приборы

- •Кремниевые мдп транзисторы

- •High-k технология metal gate.

- •Кни мдп транзисторы.

- •Транзисторы с двойным затвором.

- •Полевые транзисторы с затвором Шоттки.

- •Гетеротранзисторы

- •Немт-транзисторы.

- •Modfet-транзисторы.

- •Резонансно-туннельные транзисторы.

- •Гетероструктурный транзистор на квантовых точках.

- •Транзисторы на основе одноэлектронного туннелирования.

- •Кремниевый одноэлектронный транзистор с двумя затворами.

- •Квантово-точечный кни транзистор.

- •Одноэлектронные транзисторы на основе гетероструктур.

- •Транзисторы на основе туннельных переходов мдм

- •Приборы на основе цепочек коллоидных частиц золота.

- •Молекулярный одноэлектронный транзистор.

- •Одноэлектронный механический транзистор.

- •Баллистические транзисторы

- •Интерференционные транзисторы

- •Полевые транзисторы на отраженных электронах.

- •Нанотранзисторы на основе углеродных нанотрубок

- •Транзисторы на горячих электронах.

- •Спин чувствительные приборы.

- •Энергонезависимая память на гигантском магнитосопротивлении.

- •Спин вентильный транзистор.

- •Оптоэлектронные приборы

- •Лазеры с квантовыми ямами и точками.

- •Оптические модуляторы.

Курс лекций

“Основы наноэлектроники”

Ч.3. Наноэлектронные приборы;

Кафедра электронной техники

Севастопольского национального технического университета

к.т.н., доцент кафедры ЭЛТ Богач Николай Владимирович

сентябрь 2013г.

4 курс бакалавров специальности

РАЗДЕЛЫ

1) Физика квантовых явлений наноэлектроники;

2) Элементарные объекты наноэлектроники и их свойства;

3) Наноэлектронные приборы;

4) Технологии наноэлектроники;

5) Методы исследования наноструктур.

3. Наноэлектронные приборы 3

3.1. Кремниевые МДП транзисторы 3

3.1.1. High-K технология metal gate. 13

3.1.2. КНИ МДП транзисторы. 17

3.1.3. Транзисторы с двойным затвором. 21

3.2. Полевые транзисторы с затвором Шоттки. 33

3.3. Гетеротранзисторы 40

3.3.1. НЕМТ-транзисторы. 43

3.3.2. MODFET-транзисторы. 56

3.3.3. Резонансно-туннельные транзисторы. 57

3.3.4. Гетероструктурный транзистор на квантовых точках. 60

3.4. Транзисторы на основе одноэлектронного туннелирования. 63

3.4.1. Кремниевый одноэлектронный транзистор с двумя затворами. 68

3.4.2. Квантово-точечный КНИ транзистор. 73

3.4.3. Одноэлектронные транзисторы на основе гетероструктур. 75

3.4.4. Транзисторы на основе туннельных переходов МДМ 77

3.4.5. Приборы на основе цепочек коллоидных частиц золота. 79

3.4.6. Молекулярный одноэлектронный транзистор. 79

3.4.7. Одноэлектронный механический транзистор. 83

3.5. Баллистические транзисторы 86

3.5.1. Интерференционные транзисторы 86

3.5.2. Полевые транзисторы на отраженных электронах. 92

3.6. Нанотранзисторы на основе углеродных нанотрубок 95

3.7. Транзисторы на горячих электронах. 98

3.8. Спин чувствительные приборы. 99

3.8.1. Энергонезависимая память на гигантском магнитосопротивлении. 99

3.8.2. Спин вентильный транзистор. 101

3.9. Оптоэлектронные приборы 106

3.9.1. Лазеры с квантовыми ямами и точками. 106

3.9.2. Оптические модуляторы. 109

3.9.3. Фотоприемники с квантовыми ямами и точками. 109

3.10. Примеры ИС 111

3.10.1. Аналоговые устройства. 111

3.10.2. Цифровые устройства. 111

3.10.3. Ячейка памяти на основе прибора на многотуннельных переходах. 111

3.10.4. Выводы по ИС для ПК. 111

Наноэлектронные приборы

Кремниевые мдп транзисторы

Наноэлектронные транзисторные структуры возникли на базе элементной базой микроэлектроники. Следуя основной тенденции микроэлектроники, а именно, постоянному росту степени интеграции, размеры транзисторных структур постоянно уменьшались. Основной кремниевой транзисторной структурой, вошедшей в арсенал средств наноэлектроники, является кремниевая МДП-структура.

С уменьшением геометрических размеров транзисторов снижается площадь кристалла, уменьшаются паразитные ёмкости, улучшается быстродействие и снижается энергопотребление СБИС. За последние 30 лет длина затвора МОП-транзистора уменьшилась в 200 раз (с 10 мкм в начале 70-х годов до 50 нм в наши дни). В настоящее время коммерчески доступной является технология с минимальными горизонтальными размерами элементов 0,06 мкм, позволившая реализовать массовое производство микропроцессоров с тактовой частотой более 10 ГГц на МОП-транзисторах с длиной канала 30 нм и толщиной подзатворного окисла 1,5 нм.

Однако, каждый технологический шаг в направлении уменьшения размеров сопряжён с ростом проблем конструирования и производства, которые приходится решать для обеспечения теоретически прогнозируемых характеристик транзистора. Любое улучшение одних параметров, приводит к ухудшению других, причём с уменьшением размеров, взаимное влияние параметров становится всё более сильным.

С ростом степени интеграции СБИС и систем на кристалле увеличивается доля чипов, содержащих аналоговые блоки, которые обеспечивают взаимодействие с окружающим миром, необходимое для крупных и функционально законченных систем. К транзисторам для аналоговых и цифровых применений предъявляются противоречивые требования. Для цифровых СБИС пороговое напряжение нельзя снижать неограниченно, поскольку при этом увеличивается подпороговый ток, который определяет потребление энергии СБИС в неактивном состоянии. Верхний предел порогового напряжения ограничивается четвертью от напряжения питания, которое стараются снизить для уменьшения потребляемой мощности. Однако для аналоговых схем идеальным является нулевое пороговое напряжение Vt = 0, что увеличивает динамический диапазон аналоговой схемы, определяемый разностью между напряжением на затворе и Vt, то есть (Vgs – Vt).

Особыми требованиями к "аналоговым" транзисторам являются также повышенная нагрузочная способность (ток стока в режиме насыщения), линейность и малые нелинейные искажения на малом сигнале. Для дифференциальных каскадов и токового зеркала важна согласованность характеристик транзисторов.

Транзистор, как элемент СБИС, должен иметь:

- слабую зависимость порогового напряжения от напряжения на стоке;

- слабую зависимость порогового напряжения от длины и ширины канала;

- большую передаточную проводимость;

- большое выходное сопротивление в выключенном состоянии;

- большую нагрузочную способность, и как следствие малое сопротивления областей истока и стока;

- минимальные емкости затвора и p-n-переходов;

- запаса между пороговым напряжением и напряжением питания;

- разброс параметров техпроцесса, который растёт с уменьшением размеров транзистора, не должен снижать процент выхода годных кристаллов.

Основными явлениями, ограничивающими наноминиатюризацию МОП-транзисторов, являются:

1. Туннелирование через затвор;

2. Инжекция горячих носителей в окисел;

3. Прокол между истоком и стоком;

4. Утечки в подпороговой области;

5. Уменьшение подвижности носителей в канале;

6. Увеличение последовательного сопротивления между истоком и стоком;

Теперь конкретнее.

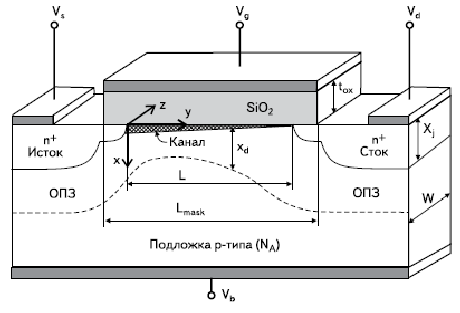

LDD МОП транзисторы. Наиболее распространённой конструкцией МОП-транзистора в СБИС, используемой более 10 лет в полупроводниковой промышленности, является LDD (Lightly Doped Drain) структура (рис. 1, 2). Ее называют структурой со слабо легированными областями стока и истока. Её особенностью является наличие мелких слаболегированных областей, которые удлиняют области истока и стока в сторону канала. Концентрацию легирующей примеси в этих областях (фосфор и бор) и режим их разгонки выбирают таким образом, чтобы получить плавный p-n-переход. Обычно концентрация примеси составляет от 4·1018 до 8·1018 см-3, в то время как в n+ областях она достигает 5·1019 – 1·1020 см-3. Полученное таким способом снижение напряжённости электрического поля в канале на границе со стоком уменьшает энергию горячих электронов, которые вызывают долговременную деградацию параметров транзистора. Слаболегированные LDD-области также повышают напряжение прокола, инжекционного и лавинного пробоя транзистора, уменьшают DIBL-эффект и эффект модуляции длины канала.

Рисунок 1. Типовая структура МОП-транзистора. Пунктиром показан ореол (halo, ОПЗ), охватывающий LDD-области истока и стока.

Комментарий. DIBL-эффект. Вследствие того, что область пространственного заряда стокового p-n перехода с ростом напряжения на стоке приближается к истоку, увеличение напряжения на стоке приводит к увеличению среднего значения вертикальной составляющей напряженности поля под затвором. Это эквивалентно уменьшению порогового напряжения и приводит к уменьшению дифференциального сопротивления стока в области насыщения (DIBL –Drain Induced Barier Lowering). DIBL-эффект также снижает потенциальный барьер p-n перехода истока, увеличивая тем самым ток инжекции электронов из истока в подпороговой области.

Например, для транзисторов с длиной канала 0,25 мкм, глубина LDD-областей истока и стока составляет 50–100 нм. Уменьшение глубины p-n-переходов до 10 нм приводит к увеличению сопротивления слоёв истока и стока до 10 кОм/квадрат, что ограничивает нагрузочную способность транзистора. Перекрытие LDD-областей затвором должно быть не менее 15–20 нм, чтобы предотвратить снижение нагрузочной способности транзистора. Толщина поликремниевого затвора составляет порядка 300 нм.

Рисунок 3. Уменьшение глубины залегания p-n-переходов LDD-областей истока и стока с развитием технологии. Границы зоны допустимых значений.

Рисунок 3. Уменьшение напряжения питания МОП ИС с развитием технологии и уменьшением толщины подзатворного диэлектрика. Границы зоны допустимых значений.

Таблица 1. Масштабирование МОП-транзисторов

|

Проектные нормы, нм |

250 |

180 |

130 |

100 |

70 |

|

Толщина окисла, нм |

4–5 |

3–4 |

2–3 |

1,5–2 |

<1,5 |

Для снижения емкостей транзистора выбирают слаболегированную подложку, а для обеспечения необходимого порогового напряжения и снижения напряжения прокола применяют легирование канала примесью того же типа, что и в подложке. Легирование выполняют примерно на глубину области пространственного заряда под затвором.

Контакты к областям истока, стока и к поликремниевому затвору выполняют с промежуточным формированием слоя TiSi2 или CoSi2 толщиной порядка 40 нм, что обеспечивает удельное сопротивление около 5 Ом на квадрат. Изоляция между поликремниевым затвором и контактами к истоку и стоку выполняется в виде спейсера (разграничителя) (рис. 1) из Si3N4.

Концентрация примеси в канале составляет 5·1017 – 1·1018 см-3. Увеличение концентрации примеси свыше этого значения, необходимое для транзисторов с длиной канала менее 100 нм, ведёт к появлению туннелирования электронов через р-n-переходы истока и стока.

Толщина окисла для транзисторов с длиной канала 0,1 мкм составляет 3–4 нм. Между толщиной окисла tox и длиной канала L МОП-транзисторов, изготавливаемых фирмой Intel в течение последних 20 лет, существует эмпирическая зависимость L = 45·tox.

Для формирования карманов МОП-транзисторов разного типа проводимости (рис. 4) используют фосфор и бор. Изоляцию между карманами выполняют обычно мелкими канавками, стенки которых окисляют, а внутренность заполняют поликремнием. Эта технология изоляции стала доминирующей в транзисторах, выполненных по 0,25-микронной технологии и пришла на смену изоляции локальным окислением кремния (LOCOS).

Показанная на рис. 1 структура транзистора обеспечила снижение длины затвора от 10 мкм в 70-х годах до 0,06 мкм в настоящее время путём простого масштабирования (табл. 1), то есть уменьшением длины затвора, толщины диэлектрика и глубины залегания p-n-переходов. Однако переход проектных норм через границу 130 нм в рамках традиционной структуры транзистора наталкивается на физические ограничения (табл. 2). Уменьшение толщины окисла приводит к росту туннельного тока утечки затвора, уменьшение глубины залегания p-n-переходов - к росту последовательного сопротивления областей транзистора, при уменьшении длины канала и порогового напряжения растёт подпороговый ток. Таким образом, транзисторы для технологий XXI века должны иметь иную структуру и использовать новые материалы для подзатворного диэлектрика.

Таблица 2. Ограничения дальнейшей миниатюризации

|

Характеристики |

Предел |

Причина ограничения |

|

Толщина окисла |

2,3 нм |

Туннелирование через окисел |

|

Глубина p-n-переходов |

30 нм |

Сопротивление областей истока и стока |

|

Легирование канала |

Vt = 0,25 В* |

Подпороговый ток |

|

Мелкие области истока и стока |

15 нм |

Сопротивление |

|

Длина канала |

60 нм |

Подпороговый ток |

|

Длина затвора |

100 нм |

Подпороговый ток |

*) Vt - пороговое напряжение.

Клубок противоречий. В процессе уменьшения длин канала и затвора достигнуто значение порядка 30 нм и меньше; толщина подзатворного окисла в схемах микропроцессоров сейчас составляет 0.8 нм, или три атомных слоя. Это позволило увеличить быстродействие микропроцессоров, снизить потребление энергии, вместе с тем возросли токи утечки (в том числе за счет туннельного тока через слой оксида), причем они весьма значительны даже для отключенного транзистора, то есть транзистор постоянно работает в цепи. С уменьшением толщины областей истока-стока возрастает их сопротивление, а значит, нужно большее напряжение для переключения транзистора, при этом увеличивается плотность потребляемой мощности. С увеличением напряжения возрастает опасность пробоя слоя диэлектрика из трех атомных слоев. Круг замкнулся. Дальнейшее уменьшение длины канала требует увеличения степени легирования в канале до 1018 см-3. Это приведет к снижению подвижности носителей и росту порога включения транзистора.

Работы по дальнейшей миниатюризации СБИС и повышению их степени интеграции ведутся широким фронтом. В потоке рекламной информации всегда необходимо понимать, к какой стадии относится достигнутый показатель.

11 нм→16 нм→

22 нм→28 нм→ 28 нм→32 нм→45 нм → 65 нм→90 нм

- исследования

- разработки и первые выпуски СБИС с низкой надежностью и малым процентом выхода годных

- устойчивое производство СБИС с приемлемой надежностью и высоким выходом годных

Рис. 3.1 Технологические разрешения на стадиях разработки СБИС.

|

годы |

минимальный технологический размер, нм |

длина затвора, нм |

размер транзистора, нм |

|

|

|

|

|

|

1970 |

|

|

|

|

1975 |

5000 |

|

|

|

1980 |

2300 |

|

10000 |

|

1985 |

1300 |

|

5000 |

|

1990 |

700 |

700 |

3000 |

|

1995 |

300 |

250 |

2000 |

|

2000 |

150 |

70 |

1300 |

|

2005 |

90 |

45 |

900 |

|

2010 |

60 |

35 |

650 |

|

2013 |

50 |

32 |

550 |

|

2015 |

45 |

30 |

500 |

|

2020 |

|

|

|

Разработки транзисторных структур для субмикронной технологии следующих за 90 нм, 65 нм поколений ведутся по разным направлениям.

Технология нанометрового диапазона будет промышленной технологией предположительно на ближайшие полвека. Исследователями пока предложено несколько путей выхода из кризиса при масштабировании параметров: