Применение электронных устройств в системах автоматизации4

.8.pdfПосле N подобных выравнивающих шагов в регистре последовательного приближения записывается двоичное число, из которого и получается напряжение ЦАП, отличающееся от входного напряжения на 1МЗР. В такте,

следующем после сравнения младшего разряда, УУ формирует сигнал

«готовность данных». Для выполнения преобразования потребовалось N+1

шагов. Синхронизация работы устройств осуществляется тактовым генератором (ТГ), который может быть внешним или внутренним.

АЦП построенные по такой схеме реализуют разрешение до 18 двоичных разрядов при частоте выборок до 200-300 КГц. Параметры АЦП поразрядного уравновешивания некоторых производителей приведены в таблице 7.2. Нужно отметить, что в связи с большим временем преобразования и во избежание ошибок входное напряжение должно оставаться неизменным на протяжении всего времени преобразования. Это достигается путем включения на входе АЦП устройства выборки-хранения

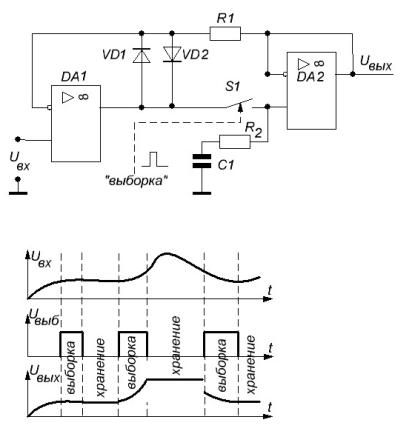

(УВХ). УВХ требуется для многих «медленных» преобразователей. Принцип работы УВХ и реализующая его схема показаны на рисунке 7.5.

81

Рисунок 7.5 - Схема УВХ и иллюстрация принципа его работы.

Во время действия сигнала «выборка» ОУ DA1 через замкнутый ключ

S1непрерывно перезаряжает конденсатор С1 до напряжения входа,

обеспечивая высокое входное сопротивление УВХ и быстрое изменение напряжения на С1. При этом, благодаря цепи отрицательной обратной связи через резистор R1, на выходе ОУ DA2 напряжение с большой точностью равно входному. После окончания сигнала «выборка» ключ S1 размыкается и на неинвертирующем входе ОУ DA2 конденсатор С1 в течение времени преобразования сохраняет уровень напряжения равного входному в момент размыкания ключа. Это возможно вследствие малого времени хранения и применения в качестве ОУ DA2 усилителя с полевыми транзисторами на входе, имеющего очень высокое входное сопротивление. Резистор R2

ограничивает выходной ток ОУ DA1 во время зарядки конденсатора на допустимом уровне, а диоды VD1и VD2 предотвращают его насыщение при разрыве цепи ООС ключом S1. УВХ выпускаются в виде отдельных

82

микросхем (например, 1100СК2, 1103СК1 и т.д.) или встраиваются в микросхемы АЦП.

7.4.АЦП двойного интегрирования.

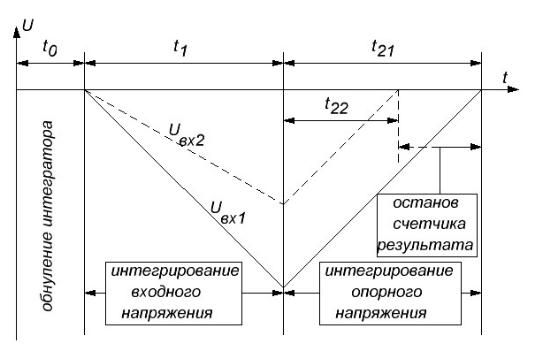

Принцип работы данного типа АЦП основан на сравнении входного

напряжения с образцовым (опорным) путем их поочередного |

|

интегрирования. Цикл преобразования |

состоит из трех временных |

интервалов (рисунок 7.6). В интервале выполняется подготовка устройства |

|

к интегрированию входного напряжения |

(обнуляется интегратор) затем в |

интервале |

оно интегрируется (длительность интервала постоянна) и, |

|

наконец, в интервале |

конденсатор интегратора разряжается до нуля при |

|

интегрировании опорного напряжения.

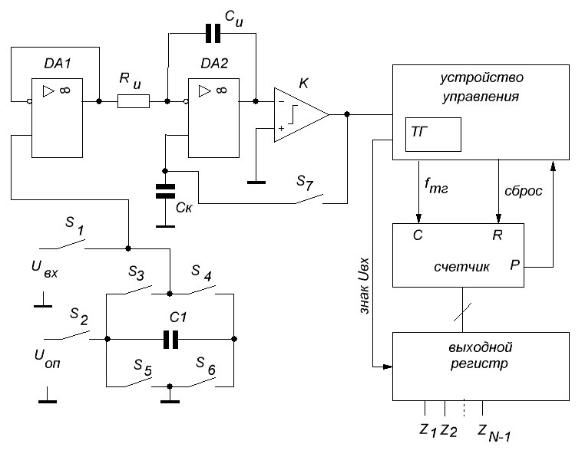

В состав схемы АЦП двойного интегрирования (рисунок 7.7) входят:

-ОУ DA1его задача обеспечить высокое входное сопротивление;

-ОУ DA1на его основе реализован инвертирующий интегратор;

-компаратор К - служит для коррекции нуля интегратора и выработки сигнала останова счетчика а также для определения знака входного напряжения;

-счетчик - предназначен для отсчета времени интегрирования входного сигнала и подсчета количества импульсов соответствующего уровню входного напряжения;

-выходной регистр - хранит результат измерения до следующей выборки.

83

Рисунок 7.6 - Принцип работы АЦП двойного интегрирования.

Работа схемы заключается в следующем. В интервале времени подготовки к измерению ключи S1, S2, S3, S5 разомкнуты, а ключи S2, S4, S6, S7 замкнуты. Интегратор, компаратор и буферный усилитель образуют повторитель напряжения, выходное напряжение которого подается на

конденсатор автоматической коррекции нуля . Входное напряжение

буферного усилителя ОУ DA1 равно нулю, а выходное его напряжению

смещения смБ. После окончания переходных процессов на конденсаторе .

установится напряжение равное смБ+ смИ, где смИ - смещение нуля интегратора.

84

Рисунок 7.7 - Структурная схема АЦП двойного интегрирования.

Одновременно конденсатор С1 заряжается от источника опорного напряжения. На интервале интегрирования входного напряжения ключи S4 и S7 размыкаются, а S1 замыкается. Так как на это время напряжение на конденсаторе . запоминается, смещение нуля в течение интервала интегрирования и на стадии счета компенсируется. По окончанию интервала интегрирования устройство управления анализирует выходное напряжение компаратора. Если среднее значение входного напряжения положительно, то на выходе компаратора устанавливается 1. В этом случае одновременно с размыканием ключа S1 замыкаются ключи S4 и S5, подключая к входу буферного усилителя конденсатор С1, на котором сохранено опорное напряжение, причем так, что это напряжение имеет полярность противоположную полярности источника опорного напряжения. Если среднее значение входного напряжения отрицательно, то на выходе

компаратора устанавливается 0, и замыкаются ключи S3,S6, подключая к

85

входу буферного усилителя опорный конденсатор другими полюсами. По сигналу компаратора УУ определяет знак входного напряжения и передает его в старший разряд выходного регистра.

Интервал интегрирования входного напряжения постоянен, а в качестве

таймера используется счетчик. При переполнении счетчика схема переходит к интегрированию опорного напряжения, при этом счетчик начинает считать с нуля. Интервал интегрирования опорного напряжения заканчивается когда выходное напряжение интегратора переходит через ноль, при этом компаратор переключается и счетчик останавливается. Информация из

счетчика переносится в регистр, она является выходным кодом и хранится в

регистре до окончания следующего цикла преобразования. Отличительная особенность метода двойного интегрирования заключается в том, что ни частота тактового генератора ни постоянная интегрирования не влияет на результат, так как интегрирование и того и другого напряжения выполняется

посредством |

одного |

и |

того же канала. Кроме того АЦП |

двойного |

|||

интегрирования |

при |

|

правильной настройке |

тактового |

генератора |

||

эффективно подавляет |

помехи промышленной |

сети (при |

|

АЦПсети |

|||

интеграл суммы целых |

периодов помехи равен |

0). |

МикросхемыТГ |

||||

|

= |

|

|||||

двойного интегрирования, как правило, содержат дешифратор двоичного кода в двоично-десятичный или в семисегментный. Параметры микросхем АЦП двойного интегрирования приведены в таблице 7.2.

7.5. Сигма-дельта АЦП.

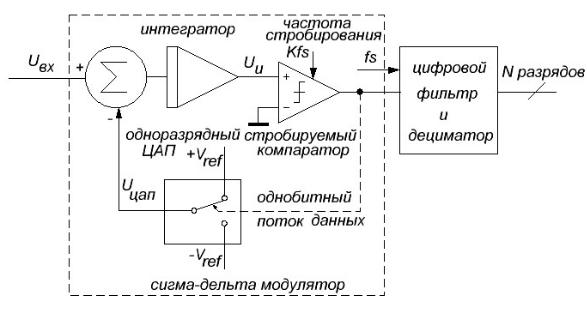

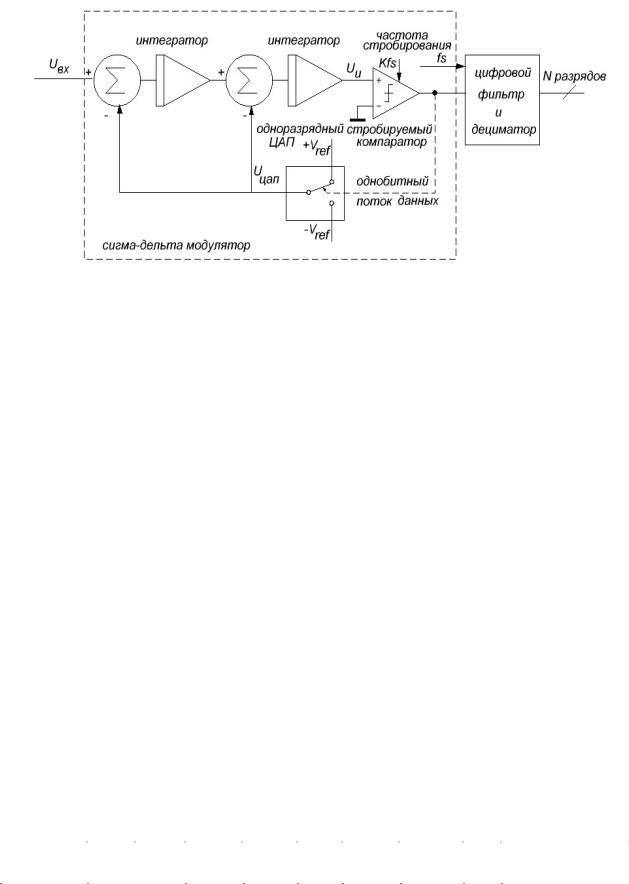

Сигма-дельта АЦП работает следующим образом (рисунок 7.8).

Предположим |

что на входе АЦП присутствует сигнал постоянного |

|

уровня |

. Интегратор постоянно вырабатывает пилообразное напряжение |

|

попеременновх |

положительной и отрицательной полярности с частотой |

|

передискретизации Кfs, где К- коэффициент передискретизации, а fsчастота выборок. Выход компаратора возвращается через однобитный ЦАП на вход

86

суммирования. Петля отрицательной обратной связи с выхода компаратора через однобитный ЦАП в точку суммирования установит среднюю величину

на выходе ЦАП цап равную входному напряжению вх. Это предполагает,

что среднее выходное напряжение должно быть равно входному напряжению. Среднее выходное напряжение ЦАП определяется частотой следования логических единиц в потоке однобитных данных с выхода стробируемого компаратора. По мере того, как входной сигнал

увеличивается в сторону |

|

|

число логических |

единиц в потоке |

||||

последовательных бит |

данных увеличивается. |

Подобным образом по мере |

||||||

|

+ |

, |

|

|

|

|

|

|

того, как сигнал уменьшается в сторону |

|

, число логических единиц в |

||||||

потоке последовательных бит данных |

уменьшается, а |

число логических |

||||||

|

− |

|

|

|||||

нулей растет. Цифровой фильтр и дециматор обрабатывают последовательный поток битов и дают конечные выходные данные с частотой выборок fs. [1]

Рисунок 7.8- Структура сигма-дельта преобразователя первого порядка.

Если взять частоту дискретизации много выше Kfs, то шум квантования распределится в более широкой полосе частот. Если затем подать сигнал на низкочастотный цифровой фильтр большая часть шума квантования будет исключена, а полезный сигнал будет передан без ослабления. Так

87

выполняется амплитудноцифровое преобразование высокого разрешения с помощью АЦП низкого разрешения. Коэффициент К обычно называется коэффициентом передискретизации.

Поскольку цифровой фильтр на выходе сужает полосу частот, выходной поток данных может быть уменьшен по сравнению с частотой стробирования

Kfs, сохраняя при этом сигнал все еще удовлетворяющим критерию Найквиста. Это достигается путем пропускания каждого М-го результата выборки на выход и отбрасывания оставшихся. Данный процесс известен как

«децимация». М может принимать любую целочисленную величину при условии, что выходной поток данных более чем в два раза превышает полосу сигналов. Децимация не означает потерю информации.

Используя более одного каскада интегрирования и суммирования в ΣΔ-

модуляторе можно получить формирование шума квантования более высокого порядка с еще лучшим значением эффективного количества разрядов для заданного коэффициента передискретизации. Например, если коэффициент передискретизации равен 64, то идеальная система второго порядка может обеспечить соотношение сигнал шум около 80 децибел, а это означает, что эффективное число бит равно 13. Блок-схема ΣΔ-модулятора второго порядка показана на рисунке 7.8.

Сигма-дельта АЦП отличает низкая стоимость, высокое разрешение,

высокая линейность и наличие самокалибровки. Эти АЦП не требуют внешних элементов, конденсатор интегратора имеет емкость порядка 10-15

пФ и его получают внутри микросхемы. Благодаря этим качествам ΣΔ АЦП применяется в микроконтроллерах, интеллектуальных датчиках, устройствах обработки звука и т.д. Многие производители отказываются от выпуска многотактных интегрирующих АЦП (например, АЦП двойного интегрирования) в пользу сигма-дельта АЦП. Параметры некоторых микросхем сигма-дельта АЦП приведены в таблице 7.2.

88

Рисунок 7.8 - Блок-схема ΣΔ-АЦП на модуляторе второго порядка

Таблица 7.2 – Характеристики некоторых микросхем АЦП [19]

|

|

|

|

Время |

|

|

|

Мо |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

щ- |

|

|

|

Разря |

|

|

преобр |

|

|

Напряж |

|

|

Наименова |

д- |

Число |

Внутре |

., мкс |

Инте |

Внутре |

. |

ност |

Примечание |

ние |

ность |

канал |

н- ний |

(част. |

р- |

н- ний |

питания |

ь |

|

ов |

УВХ |

фейс |

ИОН |

потр |

|

||||

|

бит |

пребр., |

,В |

|

|||||

|

|

|

|

МПс) |

|

|

|

. |

|

|

|

|

|

|

|

|

мВт |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АЦП широкого применения |

|

|

||||

|

|

|

|

|

|

|

|

|

|

572ПВ1 |

12 |

1 |

Нет |

110 |

Пара |

Нет |

+/-5:15 |

120 |

Требуются |

л. |

внешние ОУ |

||||||||

|

|

|

|

|

Пара |

|

|

|

Последовательно |

1108ПВ2 |

12 |

1 |

Нет |

2 |

Есть |

5 ,-6 |

1300 |

го приближения |

|

|

|

|

|

|

л. |

|

|

|

(ПП) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Пара |

|

|

|

Двухступенчаты |

МАХ114 |

8 |

4 |

Есть |

0,66 |

Нет |

+/-5 |

40 |

й. Дежур. режим |

|

|

|

|

|

|

л. |

|

|

|

- 5 мкВт |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7893 |

12 |

1 |

Есть |

6 |

Посл. |

Нет |

+/-5 |

30 |

8-выводной |

|

|

|

|

|

|

|

|

|

корпус. ПП |

|

|

|

|

|

Пара |

|

|

|

Автокалибровка, |

AD7882 |

16 |

1 |

Есть |

2,5 |

Есть |

+/- 5 |

200 |

дежур. режим - 1 |

|

|

|

|

|

|

л. |

|

|

|

мВт |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

МАХ186 |

12 |

8 |

Есть |

7,5 |

Посл. |

Есть |

5, +/- 5 |

7,5 |

ПП. Дежур. |

режим - 10 мкВт |

|||||||||

|

|

|

|

|

89 |

|

|

|

|

Таблица 7.2 продолжение

Микромощные АЦП

572ПВ3 |

8 |

1 |

Нет |

|

7,5 |

Пара |

Нет |

5 |

20 |

|

|

|

|

|

|

|

л. |

|

|

|

|

МАХ1110 |

8 |

8 |

Есть |

|

16 |

Посл. |

Есть |

2,7:5 |

0,7 |

ПП. Дежур. |

|

|

|

|

|

|

|

|

|

|

режим - 5 мкВт |

AD7888 |

12 |

8 |

Есть |

|

5 |

Посл. |

Есть |

2,7:5 |

2 |

ПП. Дежур. |

|

режим - 3 мкВт |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Автокалибровка, |

МАХ195 |

16 |

1 |

Есть |

|

9,4 |

Посл. |

Нет |

+/- 5 |

80 |

дежур. режим - |

|

|

|

|

|

|

|

|

|

|

0,1 мВт |

|

|

|

Быстродействующие АЦП |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

1107ПВ4 |

8 |

1 |

Нет |

|

0,03 |

Пара |

Нет |

+/-5, - |

3500 |

Параллельный |

|

|

|

|

|

(100) |

л. |

|

5,2 |

|

|

|

|

|

|

|

|

Пара |

|

|

|

Параллельный, |

AD9054 |

8 |

1 |

Есть |

|

(200) |

Есть |

5 |

500 |

ТТЛ уровни |

|

|

л. |

|||||||||

|

|

|

|

|

|

|

|

|

|

выхода |

|

|

|

|

|

|

Пара |

|

|

|

Параллельный, |

МАХ104 |

8 |

1 |

Есть |

|

(1000) |

Нет |

+/- 5 |

3500 |

ЭСЛ уровни |

|

|

|

|

|

|

|

л. |

|

|

|

выхода |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Пара |

|

|

|

Двухступенчаты |

AD9070 |

10 |

1 |

Есть |

|

(100) |

Есть |

-5 |

700 |

й, ЭСЛ уровни |

|

|

л. |

|||||||||

|

|

|

|

|

|

|

|

|

|

выхода |

АD9224 |

12 |

1 |

Есть |

|

(40) |

Пара |

Есть |

5 |

390 |

Четырехступенча |

|

л. |

тый |

||||||||

|

|

|

|

|

|

Пара |

|

|

|

Четырехступенча |

AD9240 |

14 |

1 |

Есть |

|

(10) |

Есть |

5 |

280 |

тый. ТТЛ, КМОП |

|

|

л. |

|||||||||

|

|

|

|

|

|

|

|

|

|

уровни выхода |

|

|

|

|

Интегрирующие АЦП |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Пара |

|

|

|

Управление |

572ПВ5 |

3,510 |

1 |

- |

|

12 пр/с |

Есть |

9 |

15 |

семисегментным |

|

|

л. |

|||||||||

|

|

|

|

|

|

|

|

|

|

и ЖКИ |

МАХ132 |

18 |

1 |

- |

|

100 |

Посл. |

Нет |

5 |

0,6 |

Многотактного |

|

пр/с |

интегрирования |

||||||||

|

|

|

|

|

|

|

|

|

|

Сигма-дельта, |

|

|

|

|

|

|

|

|

|

|

автокалибровка. |

|

|

|

|

|

20...50 |

|

|

|

|

Усилитель с |

AD7715 |

16 |

1 |

- |

|

Посл. |

Нет |

3 или 5 |

3 |

программируемы |

|

|

|

|

|

|

0 пр/с |

|

|

|

|

м усилением. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Нелин. не более |

|

|

|

|

|

|

|

|

|

|

0,0015% |

|

|

|

|

|

|

90 |

|

|

|

|