руководство

.pdf

выдаваемую на выход кодовую комбинацию и используется в том случае, когда исследуемое устройство обладает свойством квитирования (подтверждения). В этом случае после получения очередной кодовой комбинации и сопровождающего его сигнала DATA READY исследуемое устройство должно выдать сигнал подтверждения получения данных, который подается на вход синхронизации генератора (клемма в блоке TRIGGER) и производит очередной запуск генератора.

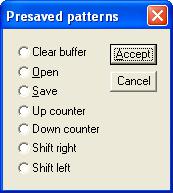

По кнопке BREAKPOINT — выполняется прерывание работы генератора в указанной ячейке. При этом требуемая ячейка выбирается на дисплее генератора курсором, а затем нажимается кнопка BREAKPOINT. Кнопкой PATTERN вызывается меню

в котором можно:

в котором можно:

Clear buffer — стереть содержимое всех ячеек (содержимое буфера экрана);

Open — загрузить кодовые комбинации (из файла с расширением *.dp);

Save — записать все набранные на экране комбинации в файл;

Up counter — заполнить буфер экрана кодовыми комбинациями, начиная с 0 в нулевой ячейке и далее с прибавлением 1 в каждой последующей ячейке;

Down counter — заполнить буфер экрана кодовыми комбинациями, начиная с FFFF в нулевой ячейке и далее с уменьшением на 1 в каждой последующей ячейке;

Shift right — заполнить каждые четыре ячейки комбинациями 1-2-4-8 со смещением их в следующих ячейках вправо;

Shift left - то же самое, но со смещением влево.

На клемму DATA READY выдается выходной синхронизирующий импульс.

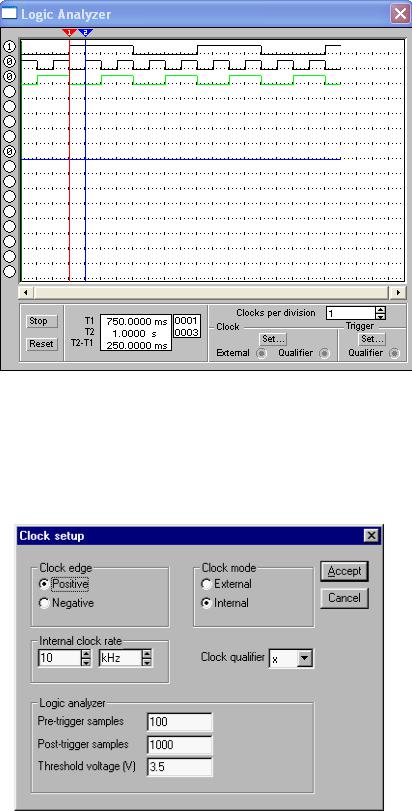

6. Logic Analyzer

31

Логический анализатор предназначен для отображения на экране монитора 16-разрядных кодовых последовательностей одновременно в 16 точках схемы, а также в виде двоичных чисел на входных клеммах.

Анализатор снабжен двумя визирными линейками, что позволяет получать точные отсчеты временных интервалов Т1, Т2 и T2-T1, а также линейкой прокрутки по горизонтали, что позволяет анализировать процессы на большом временном интервале.

В блоке Clock имеются клеммы для подключения как обычного (External), так и избирательного (Qualifier) источника запускающих сигналов, параметры которых могут быть установлены с помощью меню:

вызываемого кнопкой Set. Запуск генератора можно производить по переднему (Positive) или заднему (Negative) фронту запускающего сигнала с использованием внешнего (External) или внутреннего (Internal) источника. В окне Clock qualifier можно

32

установить значение логического сигнала (0, 1 или X), при котором производится запуск анализатора.

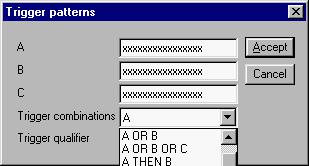

Дополнительные условия запуска анализатора могут быть выбраны с помощью

диалогового окна,  которое вызывается кнопкой Set в блоке Trigger. С помощью этого окна в каналах А, В и С можно задать нужные двоичные 16-разрядные комбинации сигналов и затем в строке Trigger combinations установить дополнительные условия отбора. Перечислим некоторые из них:

которое вызывается кнопкой Set в блоке Trigger. С помощью этого окна в каналах А, В и С можно задать нужные двоичные 16-разрядные комбинации сигналов и затем в строке Trigger combinations установить дополнительные условия отбора. Перечислим некоторые из них:

A OR В — запуск анализатора от канала А или В;

A THEN В — запуск анализатора от канала А, если сигнал в канале В равен 1;

(A OR В) THEN С — запуск анализатора от канала А или В, если сигнал в канале С равен

1.

В окне Trigger qualifier можно задать логические сигналы 1, 0 или X, при наличии которых производится запуск анализатора.

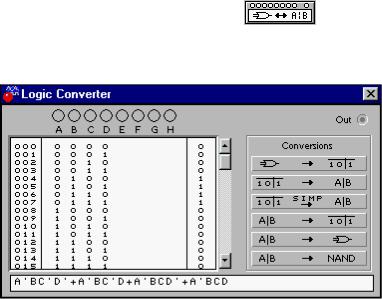

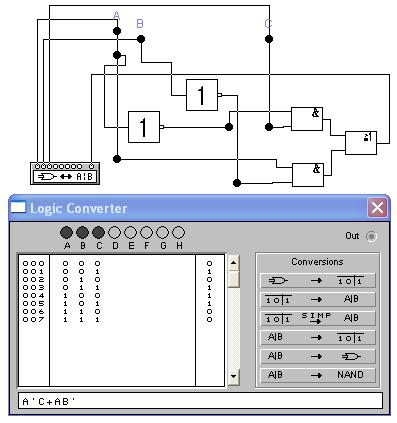

7. Logic Converter

Логический преобразователь.

На лицевой панели преобразователя показаны клеммы-индикаторы входов А, В,..., Н и одного выхода OUT, экран для отображения таблицы истинности исследуемой схемы, экран-строка для отображения ее логического выражения (в нижней части). В правой части панели расположены кнопки управления процессом преобразования (CONVERSIONS). Возможные варианты использования преобразователя:

33

1. Логический анализ n-входового устройства с одним выходом (входы исследуемого устройства подключаются к клеммам А... Н, а выход — к клемме OUT). В этом случае, используя кнопки управления, получим:

- таблицу истинности исследуемого устройства;

- таблицу истинности исследуемого устройства;

- булево выражение, реализуемое устройством;

- булево выражение, реализуемое устройством;

- минимизированное булево выражение;

- минимизированное булево выражение;

- таблицу истинности по булеву выражению;

- схему устройства на логических элементах без ограничения их типа;

- схему устройства на логических элементах без ограничения их типа;

- схему устройства только на логических элементах И-НЕ.

- схему устройства только на логических элементах И-НЕ.

2. Синтез логического устройства по таблице истинности.

2.1.Щелчком мыши по входным клеммам А, В,..., Н, начиная с клеммы А, активизируем мышью требуемое число входов анализатора, в результате чего на экране анализатора получим начальную таблицу истинности, в которой будут представлены все возможные комбинации входных сигналов и 0 в столбце OUT.

2.2.Редактируем полученную таблицу с клавиатуры (переход к следующей строке выполняется после введения значения в текущей строке) в соответствии с заданием путем записи 1, 0 или X в столбце OUT в строках, которые по комбинациям входных сигналов соответствуют заданным. При этом данные в столбцах А, В,..., Н редактирования не требуют, поскольку в этих столбцах уже имеются все возможные комбинации.

Далее последовательно задаем команды кнопками управления  ,

,  ,

, .

.

3. Синтез устройства по логическому выражению.

3.1. Булево выражение заносим в экран-строку, предварительно активизируя там мышью курсор. Используем символы А...Н, при инверсии — А'...Н'.

Далее даем команду  или

или  или

или  .

.

Ниже приведен пример синтеза схемы из выражения или таблицы истинности:

34

ЛИТЕРАТУРА:

1. В.И. Карлащук,Электронная лаборатория на IBM PC. Лабораторный практикум на базе

Electronics Workbench и MATLAB. Издание 5-е. – М.: СОЛОН-Пресс. 2004.-800с.:ил.-

(Серия «Системы проектирования»).

ПРИЛОЖЕНИЯ |

|

1. соответствие микросхем ТТЛ отечественным. |

|

7400 |

155ЛАЗ |

4 элемента 2И-НЕ (цифра 2 означает двухвходовой); |

|

7402 |

155ЛЕ1 4 элемента |

2ИЛИ-НЕ; |

|

7403 |

155ЛА9 |

4 элемента 2И-НЕ с открытым коллектором (позволяют подключать нагрузку с питанием от более высоковольтного источника питания);

35

7404 |

155ЛН1 |

|

6 |

элементов НЕ; |

|

7405 |

555ЛН2 |

|

6 |

элементов НЕ с открытым коллектором; |

|

7406 |

155ЛНЗ |

|

6 |

элементов НЕ с открытым коллектором; |

|

7407 |

155ЛП9 |

|

6 |

буферных элементов с открытым коллектором; |

|

7408 |

155ЛИ1 |

|

4 |

элемента 2И; |

|

7409 |

155ЛИ2 |

|

4 |

элемента 2И с открытым коллектором; |

|

7410 |

155ЛА4 |

|

3 |

элемента ЗИ-НЕ; |

|

7411 |

555ЛИЗ |

|

3 |

элемента 3И; |

|

7412 |

155ЛА10 |

|

3 |

элемента ЗИ-НЕ с открытым коллектором; |

|

7414 |

155ТЛ2 |

|

6 |

триггеров Шмитта с инверсией (обладают повышенной помехозащищенностью); |

|

7416 |

155ЛН5 |

|

6 |

буферных элементов НЕ; |

|

7417 |

155ЛП4 |

|

6 |

буферных элементов с открытым коллектором; |

|

7420 |

155ЛА1 |

|

2 |

элемента 4И-НЕ; |

|

7421 |

155ЛИ6 |

|

2 |

элемента 4И; |

|

7422 |

155ЛА7 |

|

2 |

элемента 4И-НЕ с открытым коллектором; |

|

7425 |

155ЛЕЗ |

|

2 |

элемента 4И-НЕ с входом стробирования; |

|

7426 |

155ЛА11 |

|

4 |

элемента 2И-НЕ с открытым коллектором; |

|

36

7428 |

155ЛЕ5 |

|

4 |

элемента 2ИЛИ-НЕ; |

|

7430 |

155ЛА2 |

|

элемент 8И-НЕ; |

|

|

7432 |

155ЛЛ1 |

|

4 |

элемента 2ИЛИ; |

|

7437 |

155ЛА12 |

|

4 |

элемента 2И-НЕ с открытым коллектором; |

|

7438 |

155ЛА13 |

|

4 |

элемента 2И-НЕ с открытым коллектором; |

|

7440 |

155ЛА6 |

|

2 |

элемента 4И-НЕ с повышенной нагрузочной способностью; |

|

7442 |

1555ИД6 |

|

дешифратор 4x10 (декодирование 4-разрядного двоичного числа в десятичное); |

||

7451 |

155ЛР11 |

|

элементы 2-2И-2ИЛИ-НЕ (2 элемента 2И, выходы которых подключены на кристалле ИМС к элементу 2ИЛИ-НЕ) и 2-ЗИ- 2ИЛИ-НЕ (аналогично для 2-ЗИ);

7454 155ЛР13

элемент 2-3-3-2И-4ИЛИ-НЕ (2 элемента 2И и 2 элемента 3И объединены через 4ИЛИ-НЕ);

7455 155ЛР4

элемент 4-4И-2ИЛИ-НЕ (2 элемента 4И объединены через 2ИЛИ-НЕ) с возможностью объединения по ИЛИ (выходной каскад элемента

2ИЛИ-НЕ имеет дополнительные входы транзистора С — Collector и Е — Emitter, что и позволяет осуществить объединение по ИЛИ);

7472 |

155ТВ1 |

JK-триггер и элементом 3И на входах; |

|

7474 |

155ТМ2 |

2 D-триггера; |

|

7475 |

155ТМ7 |

4 D-триггера с прямыми и инверсными выходами; |

|

7476 |

155ТВ7 |

2 JK-триггера; |

|

7477 |

155ТМ5 |

4 D-триггера с прямыми выходами; |

|

7478 |

134ТВ14 |

два JK-триггера; |

|

37

7486 |

155ЛП5 |

|

4 |

элемента Исключающее ИЛИ; |

|

7490 |

155ИЕ2 |

|

4-разрядный асинхронный двоично-десятичный счетчик; |

|

|

7491 |

134ИР2 |

|

8-разрядный сдвиговый регистр; |

|

|

7492 |

155ИЕ4 |

|

4-разрядный асинхронный счетчик-делитель на 12; |

|

|

7493 |

155ИЕ5 |

|

4-разрядный асинхронный двоичный счетчик; |

|

|

74107 |

155ТВ6 |

|

2 |

JK-триггера с раздельной установкой нуля; |

|

74109 |

155ТВ15 |

|

2 |

JK-триггера; |

|

74112 |

155ТВ9 |

|

2 |

JK-триггера; |

|

74113 |

155ТВ10 |

|

2 |

JK-триггера с предустандвкой нуля или единицы; |

|

74114 |

155ТВ11 |

|

2 |

JK-триггера с предустановкой нуля или единицы и общим обнулением; |

|

74125 |

155ЛП8 |

|

4 |

буфера с тремя состояниями; |

|

74126 |

155ЛП14 |

|

4 |

формирователя с тремя состояниями; |

|

74132 |

155ТЛЗ |

|

4 |

триггера Шмитта; |

|

74134 |

155ЛА19 |

|

элемент 12И-НЕ с тремя состояниями; |

|

|

74138 |

155ИД7 |

|

дешифратор-демультиплексор 3x8; |

|

|

74139 |

155ИД14 |

|

2 |

дешифратора-демультиплексора 2x4; |

|

74145 |

155ИД10 |

|

двоично-десятичный дешифратор с открытым коллектором; |

|

|

38

74147 |

555ИВЗ |

приоритетный шифратор 10-4; |

|

74148 |

155ИВ1 |

шифратор приоритетов 8x3; |

|

74150 |

155КП1 |

селектор-мультиплексор 16x1; |

|

74151 |

155КП7 |

селектор-мультиплексор 8x1; |

|

74152 |

155КП5 |

селектор-мультиплексор 8x1; |

|

74153 |

155КП2 |

2 селектора-мультиплексора 4х2; |

|

74154 |

155ИДЗ |

дешифратор-демультиплексор 4x16; |

|

74155 |

155ИД4 |

2 дешифратора-мультиплексора 2x4; |

|

74156 |

555ИД5 |

2 дешифратора-демультиплексора 2x4 с открытым коллектором; |

|

74157 |

533КП16 |

4-разрядный селектор-мультиплексор 2x1; |

|

74158 |

1533КП18 |

4-разрядный селектор-мультиплексор 2x1 с инверсией; |

|

74160 |

155ИЕ9 |

4-разрядный синхронный двоично-десятичный счетчик; |

|

74162 |

1533ИЕ11 |

4-разрядный синхронный десятичный счетчик; |

|

74163 |

155ИЕ18 |

4-разрядный синхронный реверсивный двоично-десятичный счетчик; |

|

74164 |

155ИР8 |

8-разрядный регистр сдвига с параллельными выходами; |

|

74165 |

555ИР9 |

8-разрядный регистр сдвига с параллельным вводом информации; |

|

74166 |

555ИР10 |

8-разрядный регистр сдвига с синхронным параллельным вводом;

39

74169 |

155ИЕ17 |

4-разрядный двоичный синхронный реверсивный счетчик; |

|

74173 |

155ИР15 |

4-разрядный регистр с тремя состояниями; |

|

74174 |

155ТМ9 |

6 D-триггеров; |

|

74175 |

155ТМ8 |

4D-триггера; |

|

74181 |

155ИПЗ |

4-разрядное АЛУ; |

|

74191 |

155ИЕ13 |

синхронный реверсивный двоичный счетчик; |

|

74192 |

155ИЕ6 |

двоично-десятичный реверсивный счетчик; |

|

74194 |

155ИР11 |

4-разрядный универсальный регистр сдвига; |

|

74195 |

155ИР12 |

4-разрядный регистр сдвига с параллельным вводом; |

|

74198 |

155ИР13 |

8-разрядный универсальный регистр сдвига; |

|

74240 |

155АПЗ |

8 буферов с инверсией и тремя состояниями; |

|

74241 |

155АП4 |

8 буферов с тремя состояниями; |

|

74244 |

155АЛ5 |

2x4 буферов с тремя состояниями; |

|

74251 |

155КП15 |

селектор-мультиплексор 8x1 с тремя состояниями; |

|

74253 |

155КП12 |

2 селектора-мультиплексора 4x1 с тремя состояниями; |

|

74257 |

155КП11 |

4 селектора-мультиплексора 2x1 с тремя состояниями; |

|

74258 |

155КП14 |

4 селектора-мультиплексора 2x1 с тремя состояниями и инверсией;

40