Розрахунково-графічна робота з КС. Методичка

.pdf

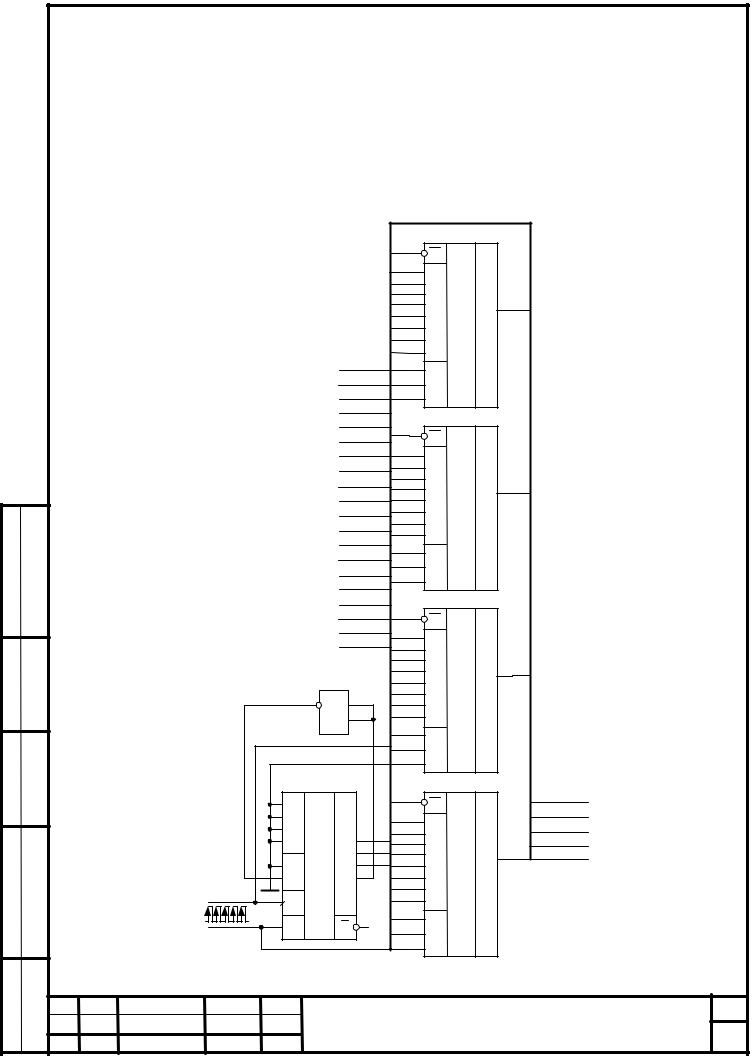

Принципова схема блока комутації наведена на рис.5.6, і працює так. Всі розряди першої декади лічильного блока подаються на перші входи мультилексорів, розряди другої декади – на другі входи мультиплексорів і т.д. При подачі паралельно (на всі адресні входи одночасно) адреси потрібної декади, мультиплексори синхронно комутують дану декаду (кожний свій розряд) на виходи схеми комутації Q0к-Q3к.

Підпис і дата |

|

|

|

|

|

|

|

Інв. № дубл. |

|

|

|

|

|

|

|

Взам. інв. № |

|

|

|

|

|

|

|

Підпис і дата |

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

№оригін |

|

|

|

Рис.5.6. Принципова схема блока комутації |

|

||

|

|

|

|

362.6050102 1 511 ПЗ |

Арк. |

||

. |

|

|

|

|

|

||

Інв |

|

|

|

|

17 |

||

Зм. |

Арк. |

№ докум. |

Підпис |

Дaта |

|||

|

|||||||

|

|

|

|

|

40 |

|

|

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

5.3. Проектування перетворювача коду 3321 у десятковий унітарний код

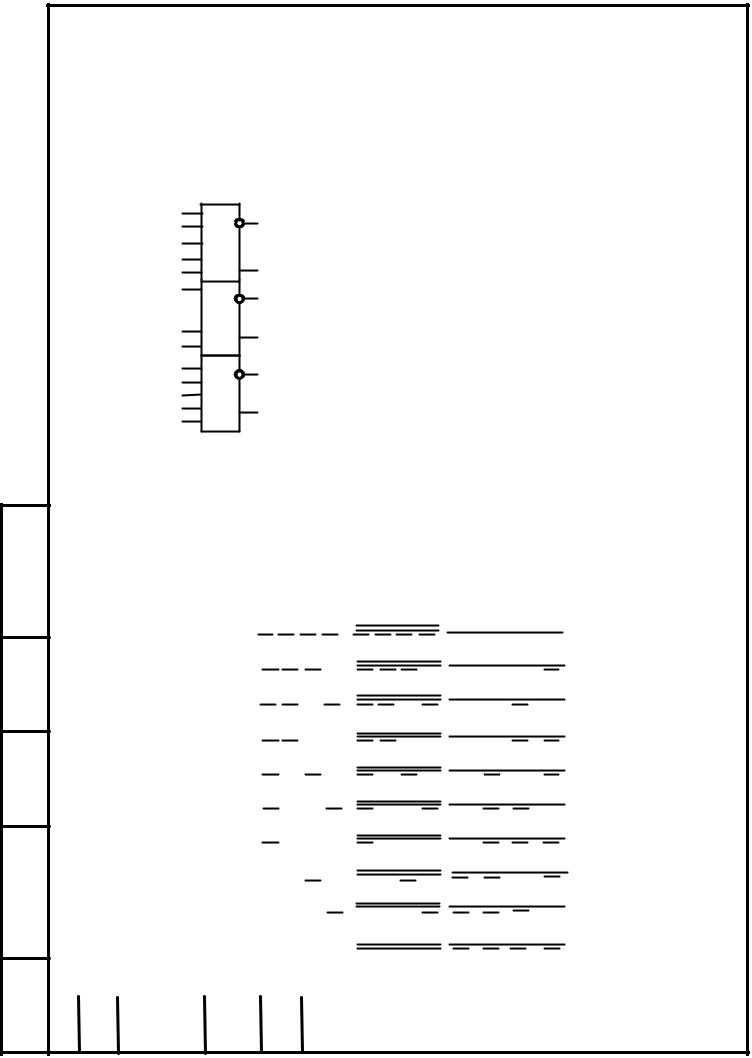

Для побудови перетворювача коду 3321 у десятковий унітарний код, окрім використаних раніше мікросхем, була задіяна також інтегральна схема К1500ЛМ101 (рис.5.7).

12 |

|

|

|

Мікросхема |

К1500ЛМ101 може |

|||||

1 |

10 |

виконувати |

логічні |

функції |

|

АБО-НЕ |

||||

13 |

|

|||||||||

|

|

|

||||||||

14 |

|

|

(при |

використанні |

інверсного |

виходу) |

||||

15 |

|

11 |

||||||||

10 |

|

|

|

|

|

|

|

|

|

|

17 |

1 |

9 |

та АБО |

(при використанні |

прямого |

|||||

19 |

||||||||||

20 |

|

|

виходу). |

В |

одному |

корпусі |

розміщені |

|||

21 |

|

8 |

||||||||

22 |

|

|

три |

п’ятивходові |

логічні |

елементи. |

||||

23 |

1 |

5 |

||||||||

24 |

|

|

Мікросхема |

виготовлена |

на |

основі |

||||

1 |

|

4 |

||||||||

2 |

|

|||||||||

3 |

|

|

технологій емітерно-звязної логіки [4]. |

|||||||

Рис.5.7. Мікросхема К1500ЛМ101 |

||||||||||

|

Для |

проектування принципової |

||||||||

|

|

|

|

|||||||

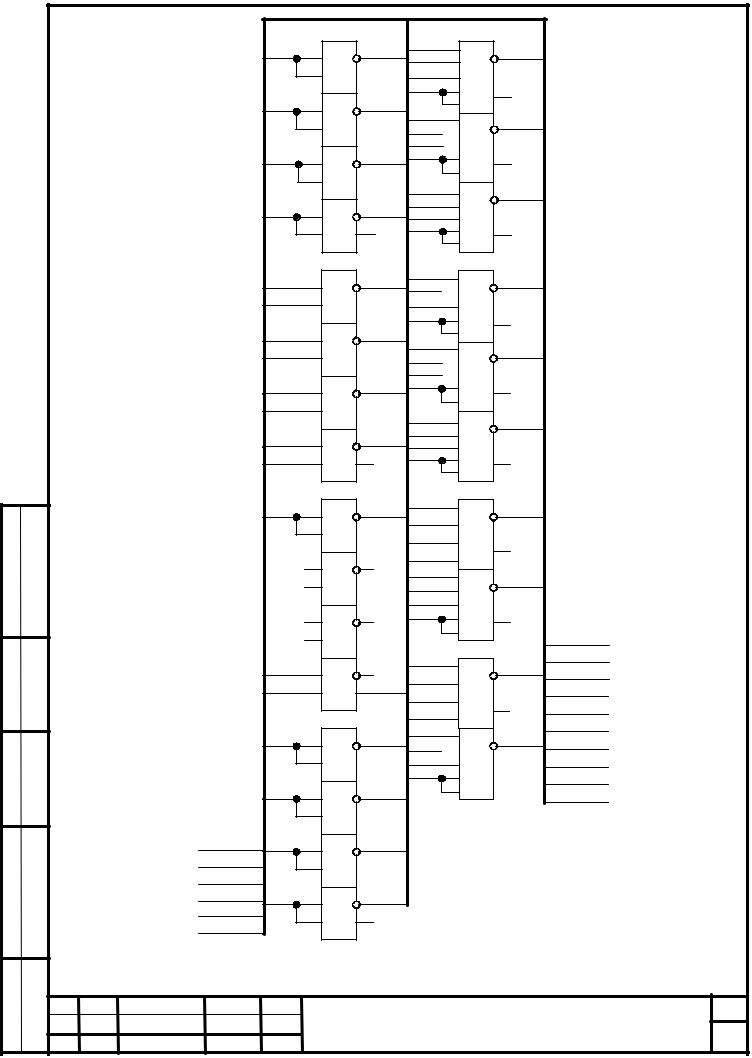

схеми перетворювача коду (рис.5.8), з табл.2.1 були записані його вихідні логічні функції, які, в даному випадку – для унітарного коду, не потребують мінімізації. Загальний вигляд отриманих функцій Q0-Q9, за якими була побудована схема дешифратора, наведений у (5.3).

Q0=D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

Q1= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

Q2= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

Q3= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

Q4= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0 (5.3)

Q5= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

Q6= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

Q7= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

Q8= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

Q9= D3D2D1D0=D3D2D1D0=D3+D2+D1+D0

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

18 |

|

Зм. Арк. № докум. Підпис Дaта |

|

41

|

|

|

|

|

|

|

|

DD36 |

|

|

37 |

12 |

DD40 |

|

|

|

|

|

|

|

|

|

|

26 |

4 |

1 |

2 |

31 |

38 |

13 |

1 |

10 |

45 |

|

|

|

|

|

|

|

|

|

5 |

|

|

|

39 |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

15 |

|

11 |

|

|

|

|

|

|

|

|

|

27 |

6 |

1 |

3 |

32 |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

41 |

|

|

|

|

|

||||||

|

|

|

|

|

|

|

17 |

1 |

9 |

46 |

|

|

|||||

|

|

|

|

|

|

|

7 |

|

|

|

38 |

19 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

39 |

20 |

|

|

|

|

|

|

|

|

|

|

|

28 |

10 |

1 |

14 |

33 |

40 |

21 |

|

8 |

|

|

|

|

|

|

|

|

|

|

11 |

|

|

|

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

5 |

47 |

|

|

||

|

|

|

|

|

|

29 |

12 |

1 |

15 |

34 |

42 |

24 |

|

|

|

|

|

|

|

|

|

|

|

39 |

1 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

13 |

|

9 |

|

40 |

2 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

DD37 |

|

|

41 |

12 |

DD41 |

|

|

|

|

|

|

|

|

|

|

36 |

4 |

1 |

2 |

37 |

42 |

13 |

1 |

10 |

48 |

|

|

|

|

|

|

|

|

31 |

5 |

|

|

|

39 |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

15 |

|

11 |

|

|

|

|

|

|

|

|

|

36 |

6 |

1 |

3 |

38 |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

41 |

17 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

1 |

9 |

49 |

|

|

||||||

|

|

|

|

|

|

32 |

7 |

|

|

|

38 |

19 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

43 |

20 |

|

|

|

|

|

|

|

|

|

|

|

36 |

10 |

1 |

14 |

39 |

40 |

21 |

|

8 |

|

|

|

|

|

|

|

|

|

33 |

11 |

|

|

|

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

23 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

1 |

5 |

50 |

|

|

||

|

|

|

|

|

|

36 |

12 |

1 |

15 |

40 |

42 |

24 |

|

|

|

|

|

|

|

|

|

|

|

43 |

1 |

|

|

|

|

|

|||||

|

|

|

|

|

|

34 |

13 |

|

9 |

|

40 |

2 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

DD38 |

|

|

41 |

4 |

DD42 |

|

|

|

|

|

|

|

|

|

|

30 |

4 |

1 |

2 |

35 |

42 |

5 |

1 |

3 |

51 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

і дата |

|

|

|

|

|

|

5 |

|

|

|

43 |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

40 |

7 |

|

|

|

|

||

|

|

|

|

|

|

6 |

1 |

3 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

41 |

9 |

|

|

|

|

|

||||

Підпис |

|

|

|

|

|

|

7 |

|

|

|

1 |

14 |

52 |

|

|

||

|

|

|

|

|

|

|

|

|

38 |

10 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

43 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

10 |

1 |

14 |

|

44 |

12 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

11 |

|

|

|

|

13 |

|

|

|

45 |

Q0 |

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

дубл |

|

|

|

|

|

|

|

|

|

|

37 |

4 |

DD43 |

|

|

46 |

Q1 |

|

|

|

|

|

24 |

12 |

1 |

15 |

|

1 |

3 |

53 |

47 |

Q2 |

|||

|

|

|

|

|

|

42 |

5 |

||||||||||

. № |

|

|

|

|

|

35 |

13 |

|

9 |

36 |

|

|

|

48 |

Q3 |

||

|

|

|

|

|

|

43 |

6 |

|

2 |

|

|||||||

Інв |

|

|

|

|

|

|

|

|

|

|

44 |

7 |

|

|

49 |

Q4 |

|

|

|

|

|

|

|

|

DD39 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

41 |

9 |

|

|

|

50 |

Q5 |

|

. № |

|

|

|

|

|

37 |

4 |

1 |

2 |

41 |

1 |

14 |

54 |

51 |

Q6 |

||

|

|

|

|

|

42 |

10 |

|||||||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

5 |

|

|

|

43 |

11 |

|

|

|

52 |

Q7 |

|

інв |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

44 |

12 |

|

15 |

|

53 |

Q8 |

|

. |

|

|

|

|

|

|

|

1 |

|

|

|

13 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Взам |

|

|

|

|

|

38 |

6 |

3 |

42 |

|

|

|

|

54 |

Q9 |

||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

дата |

|

|

|

D0 |

26 |

39 |

10 |

1 |

14 |

43 |

|

|

|

|

|

|

|

|

|

|

D1 |

27 |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

і |

|

|

|

D3 |

29 |

40 |

12 |

1 |

15 |

44 |

|

|

|

|

|

|

|

Підпис |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

V |

24 |

|

13 |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

C |

30 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

. |

|

|

Рис.5.8. Принципова схема дешифратора коду 3321 у |

||||||||||||||

№оригін |

|

|

|

|

двійково-десятковий |

унітарний код |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Арк. |

|

. |

|

|

|

|

|

|

|

|

|

|

362.6050102 1 511 ПЗ |

||||||

Інв |

|

|

|

|

|

|

|

|

|

|

|||||||

Зм. |

Арк. |

№ докум. |

Підпис |

Дaта |

|

|

|

|

|

|

|

|

|

|

19 |

||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

42 |

|

|

|

|

|

|

|

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

Аналогічно, як і для дешифратора лічильного блока, функції (5.3) мають бути з допомогою законів де Моргана перетворені у базис АБО-НЕ, у зв’язку з відсутністю у логічному наборі мікросхем серії К500 та К1500 базових логічних елементів кон’юнкції.

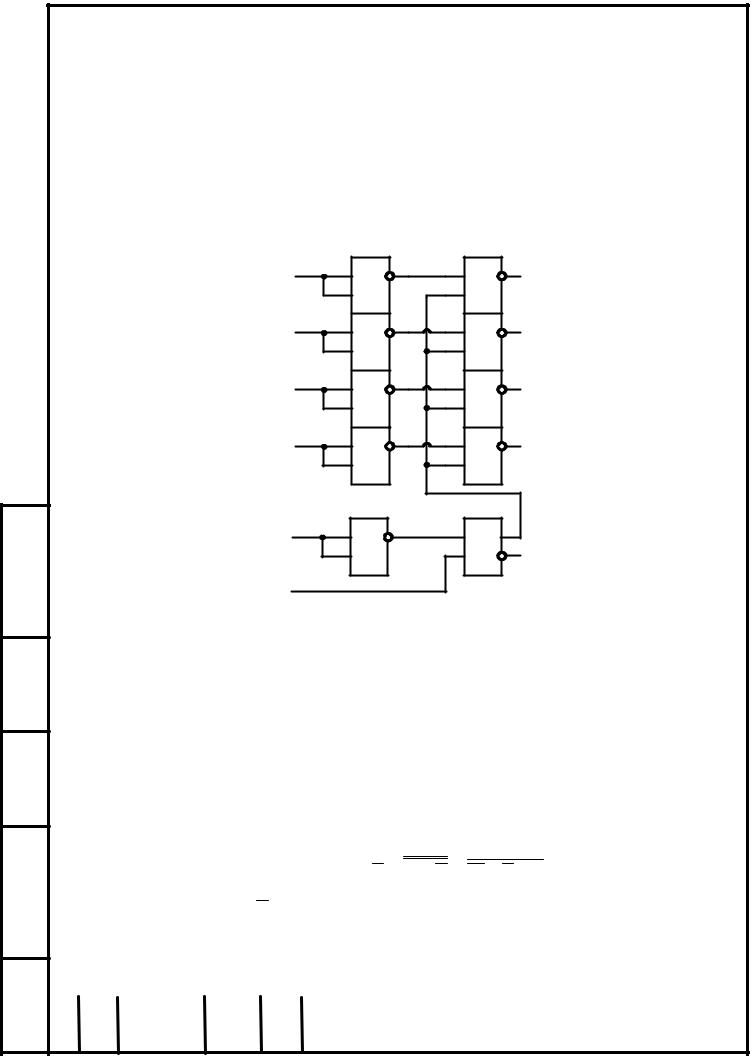

Це ж стосується і схеми керування процесом дозволу та синхронізації дешифрування результату підрахунку кількості вхідних імпульсів, яка

зображена на рис.5.9. |

|

DD36 |

DD37 |

|

|

|

|

||

|

D0 |

1 |

1 |

D0' |

|

|

|

||

|

D1 |

1 |

1 |

D1' |

|

|

|

||

|

D2 |

1 |

1 |

D2' |

|

|

|

||

|

D3 |

1 |

1 |

D3' |

|

|

|

||

|

|

DD38.1 |

DD38.4 |

|

|

V |

1 |

1 |

|

|

|

|

|

C

Рис.5.9. Схема керування перетворювачем коду 3321 у десятковий унітарний код

На даній схемі, як і в рівняннях (1.3), D0-D3 – сигнали, що надходять з виходу схеми комутації (ті ж самі сигнали, що й Q0к-Q3к), а D0’-D3’ – сигнали, що безпосередньо надходять на входи перетворювача коду після подачі дозволяючого V та синхронізуючого С сигналів.

Рівняння, за якими була реалізована дана схема:

D′i = DiV C = DiV C = Di +V +C .

Синхросигнал C вибраний інверсним для того, щоб тактування (синхронізацію) схеми комутації та схеми перетворювача коду можна було б здійснити одними й тими ж п’ятьма тактовими імпульсами, але різними

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

20 |

|

Зм. Арк. № докум. Підпис Дaта |

|

|

|

43 |

|

фронтами. Переднім фронтом здійснюється (запускається) процес комутації відповідної декади, заданої адресою, а заднім фронтом (перепадом з 1 в 0) – процес перетворення коду 3321 у десятковий унітарний код.

Загальна принципова схема розробленого двійково-десяткового лічильника у коді 3321 зображена в графічній частині технічної документації курсового проекту.

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

|

|

|

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

21 |

|

Зм. Арк. № докум. Підпис Дaта |

|

|

|

|

|

44

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

6.Аналіз роботи пристрою

6.1.Побудова часових діаграм

Побудова часових діаграм функціонування принципової схеми чи окремих її частин дозволяє детальніше пояснити і, водночас, ще глибше проаналізувати й перевірити правильність функціонування розробленого пристрою.

Для схеми розробленої в даному курсовому проекті, оптимальною за складністю та інформативністю є побудова часових діаграм окремо для: 1) однієї декади лічильного блока; 2) схеми комутації і перетворювача коду 3321 у десятковий унітарний код, які наведено в графічній частині технічної документації до курсового проекту.

На часових діаграмах враховано, що рівень логічної одиниці емітернозв’язної логіки становить не менше -0,98В, а рівень логічного нуля – -1,63В (тому всі діаграми знаходяться нижче осі часу – в області від’ємних напруг).

Сигнали на часовій діаграмі роботи однієї декади лічильного блока: V,

R та +1 – дозволяючий, сигнал обнулення та вхідний сигнал підраховуваних імпульсів, відповідно; Q0-Q3 та P – вихідні сигнали розрядів і переповнення лічильника К500ИЕ137 у коді 8421; Q’0-Q’3 та Р’ – вихідні сигнали розрядів і переповнення, що знімаються з виходів дешифратора коду 8421 у код 3321.

На діаграмі роботи принципової схеми комутації та перетворювача коду: V, С та S 2 – дозволяючий, тактовий сигнали схем комутації та перетворювача коду, а також сигнал обнулення генератора адрес декад відповідно; А0-А2 – сигнали адресного коду декад лічильного блока; Q0к-Q3к (або D0-D3) – сигнали на виходах схеми комутації (або на входах схеми перетворювача коду 3321 у десятковий унітарний код); Q0-Q9 – виходи схеми перетворювача коду для десяткового унітарного коду кожної декади

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

22 |

|

Зм. Арк. № докум. Підпис Дaта |

|

45

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

двійково-десяткового лічильника.

Провівши вертикальну лінію на часових діаграмах і рухаючи її вздовж осі часу легко переконатись у правильності функціонування спроектованих блоків і пристрою в цілому (тобто у функціонуванні спроектованого пристрою відповідно до поставленого в курсовому проекті завдання).

6.2. Розрахунок складності, швидкодії та максимальної частоти вхідного сигналу

На практиці, при проектуванні цифрових пристроїв, для вибору однієї схеми з кількох можливих варіантів здійснюють їх порівняння за заданими параметрами, основними з яких є складність і швидкодія схеми.

Для оцінювання складності існує декілька способів, найбільш розповсюдженими з яких є наступні:

1.В теоретичних розробках орієнтуються на довільну елементну базу і використовують оцінювання складності схем за Квайном. Складність (ціна) за Квайном визначається сумарною кількістю входів логічних елементів, з яких складається схема. При такому оцінюванні одиницею складності є один вхід логічного елемента (ціна інверсного входу приймається рівною двом).

2.При розробці схем на основі конкретної елементної бази складність цифрового пристрою вимірюють кількістю використаних в схемі корпусів інтегральних мікросхем. Інколи даний параметр виражають у вигляді кількості умовних корпусів мікросхем, який визначають за формулою

k |

m n |

||

N = ∑ |

i i |

, де k – кількість типів мікросхем; mi – кількість мікросхем |

|

14 |

|||

i=1 |

|

||

i-го типу; ni – кількість виводів мікросхем i-го типу. Як умовний використовують корпус мікросхеми на 14 виводів.

Перший спосіб використовують, в основному, при проектуванні

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

23 |

|

Зм. Арк. № докум. Підпис Дaта |

|

46

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

інтегральних схем, оскільки їх вартість залежить від площі кристалу, яка пропорційна кількості логічних елементів та кількості їх входів.

Другий спосіб є зручним при порівнянні пристроїв, побудованих на готових мікросхемах. Саме таким способом і проводилось оцінювання складності розробленого в даному курсовому проекті пристрою, для чого був використаний перелік елементів до його принципової схеми, який приведено у графічній частині технічної документації курсового проекту.

Для реалізації розробленої принципової схеми було використано 43 корпуси мікросхем емітерно-зв’язної логіки, серед яких: 6 корпусів – К500ИЕ137, 24 корпуси – К500ЛМ102, 7 корпусів – К500ЛМ109, 2 корпуси

– К1500ЛМ101 та 4 корпуси – К500ИД164. Використовуючи дані попередніх розділів пояснювальної записки про конструктивно-технологічні параметри вказаних мікросхем, за вищенаведеною формулою знаходимо кількість умовних корпусів мікросхем:

k |

m n |

5 |

6 16 |

|

24 16 |

|

7 16 |

|

2 24 |

|

4 16 |

|

|

N = ∑ |

i |

i |

= ∑ |

|

+ |

|

+ |

|

+ |

|

+ |

|

=50,3 . |

14 |

|

14 |

14 |

14 |

14 |

14 |

|||||||

i=1 |

|

i=1 |

|

|

|

|

|

||||||

Швидкодія схеми оцінюється максимальною затримкою сигналу при проходженні його від входу схеми до виходу, тобто визначається проміжком часу від моменту надходження вхідних сигналів до моменту встановлення відповідних значень вихідних.

Затримка сигналу комбінаційної схеми є кратною до кількості елементів, через котрі проходить сигнал від входу до виходу схеми. Тому швидкодія такої схеми характеризується значенням rmaxt, де t – затримка сигналу на одному елементі. Значення rmax визначається кількістю рівнів схеми, що розраховується наступним чином. Входам комбінаційної схеми приписують нульовий рівень. Логічні елементи, входи яких є входами всієї схеми відносяться до першого рівня. Кожний наступний елемент відноситься до рівня r, якщо його входи є виходами r-1 (попереднього) рівня елементів. Максимальний рівень елементів rmax називається рангом

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

24 |

|

Зм. Арк. № докум. Підпис Дaта |

|

47

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

комбінаційної схеми.

Оскільки в розробленій схемі лічильника процес підрахунку імпульсів лічильним блоком і процес перетворення результату підрахунку перетворювачем коду 3321 у десятковий унітарний код є розділеними в часі (див. п.3), то швидкодія схеми визначається як максимальний час від моменту надходження одного підраховуваного імпульсу на вхід лічильного блока (лічильника першої декади) до моменту перетворення в унітарний код останньої (п’ятої) декади результату підрахунку (рис.3.1). Тобто, максимальний час затримки схеми розробленого лічильника визначається як сумарний максимальний час затримки окремих його блоків: tmax=tЛБ+5(tБК+tД), де tЛБ, tБК, tД – часи затримки, відповідно: першої декади лічильного блока; блока комутації (який складається з генератора адреси декад та схеми комутації); та дешифратора коду 3321 у десятковий унітарний код.

Максимальний час затримки лічильного блока tЛБ дорівнює сумі часу затримки tК500ИЕ137 вхідного лічильника К500ИЕ137 першої декади, який рівний 8нс [4], і часу затримки комбінаційної схеми дешифратора результату підрахунку імпульсів першою декадою з коду 8421 у код 3321 – t(8421-3321), ранг якої дорівнює 3 (5.2, рис.5.4). Оскільки час затримки сигналу логічним елементом емітерно-зв’язної логіки серії К500 складає tЛЕ К500=2,9нс [4], то: tЛБ=tК500ИЕ137+3tЛЕ К500=8нс+3 2,9нс=16,7нс.

Схема дешифратора коду 3321 у десятковий унітарний код є повністю комбінаційною (складається тільки з мікросхем базових логічних елементів), ранг якої, враховуючи схему керування (рис.5.9), рівний 4 (5.3,

рис.5.8). Тому: tД=4tЛЕ К500=4 2,9нс=11,6нс.

Максимальний час затримки tБК блока комутації (рис.5.6) визначається часом затримки генератора адреси декад, роль якого відіграє двійководесятковий лічильник К500ИЕ137 (tК500ИЕ137=8нс); часом затримки схеми

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

25 |

|

Зм. Арк. № докум. Підпис Дaта |

|

|

|

48 |

|

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

комутації, швидкодія якої повністю визначається швидкодією мультиплексорів К500ИД164 (tК500ИД164=8нс [4]); а також тривалістю паузи tП синхроімпульсів С (tП=tЛЕ К500), якими тактується робота як схеми комутації так і перетворювача коду 3321 у десятковий унітарний код:

tБК=tК500ИЕ137+tК500ИД164+tЛЕ К500.

Зауважимо, що величина tБК, фактично, дорівнює періоду повторення ТСІ синхроімпульсів С. Це твердження, а також рівність tП=tЛЕ К500 можна пояснити наступним чином.

Тривалість вершини тактового синхроімпульсу має бути не меншою за суму часів затримок генератора адрес декад та схеми комутації: tК500ИЕ137+tК500ИД164 (рис.3.1), в противному випадку перетворювач коду не встигне перетворити код попередньої декади, а на його вхід вже надійде наступна декада. Враховуючи те, що (tК500ИЕ137+tК500ИД164)>tД, тривалість паузи синхроімпульсу tП можна звести до мінімуму: перетворення коду попередньо декади завершиться швидше, ніж на вхід перетворювача надійде код наступної. Якщо генератор синхроімпульсів також буде побудований на елементах емітерно-зв’язної логіки, то мінімальна тривалість паузи синхроімпульсу може досягти значення tП=tЛЕ К500. Тому період повторення синхроімпульсів: ТСІ=tК500ИЕ137+tК500ИД164+tЛЕ К500=tБК=8нс+8нс+2,9нс=18,9нс, а максимальна їх частота дорівнюватиме, відповідно: fСІ=1/ТСІ=1/18,9нс= =52910053Гц≈53МГц.

Отже, максимальний час затримки схеми лічильника, розробленої в курсовому проекті, дорівнює: tmax=tЛБ+5(tБК+tД)=16,7нс+5(18,9нс+11,6нс)= =169,2нс.

Максимальна частота вхідного сигналу (максимальна частота вхідних підраховуваних імпульсів) співпадає із частотою роботи першої декади лічильного блоку, і визначається із співвідношення: fмах=1/tЛБ=1/16,7нс= =59880234,5Гц≈60МГц.

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

26 |

|

Зм. Арк. № докум. Підпис Дaта |

|

49