Розрахунково-графічна робота з КС. Методичка

.pdf

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

2. Аналіз завдання на курсовий проект

Аналізуючи задане в курсовому проекті завдання і зважаючи на обмежений (у плані різноманітності) набір базових логічних елементів та вузлів емітерно-зв’язної логіки, можна зробити висновок, що саме схема з груповою структурою лічильника з послідовним переносом між групами є найбільш оптимальним варіантом для побудови заданого функціонального вузла.

Отже, у курсовому проекті необхідно розробити функціональний вузол комп’ютерної схемотехніки, що являє собою двійково-десятковий лічильник у коді 3321 на п’ять декад з введенням даних у число-імпульсному коді та виведенням результату підрахунку вхідних імпульсів у десятковому унітарному коді, подекадно. Розробку принципової схеми необхідно виконати в логічному базисі набору інтегральних мікросхем серії К500 та К1500.

Для реалізації заданого функціонального вузла треба виконати нижченаведені завдання.

Розробити п’ятидекадний лічильний блок у коді 3321, що здійснюватиме підрахунок вхідних числових імпульсів. Спроектувати схему комутації (фактично – спеціалізований мультиплексор), що дозволятиме синхронізовано почергово комутувати всі декади лічильного блока, починаючи з першої, з блоком подекадного перетворення коду 3321 у десятковий унітарний код. І, власне, розробити сам вказаний блок перетворювача коду. Необхідно також передбачити обнулення лічильника в будь-який момент часу (на будь-якому етапі роботи пристрою), а також можливість керувати дозволом роботи розробленого функціонального вузла.

Виходячи із завдання на курсовий проект та сказаного вище, стає зрозумілим, що виведення результату підрахунку кількості вхідних імпульсів має здійснюватись після припинення процесу підрахунку й бути

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

7 |

|

Зм. Арк. № докум. Підпис Дaта |

|

30

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

синхронізованим з процесом комутації виходу кожної декади лічильного блока зі входом перетворювача коду. В противному випадку (тобто при одночасному протіканні процесу підрахунку імпульсів та процесу комутації і перетворення результату підрахунку), через те, що виведення результату підрахунку кількості імпульсів потрібно здійснювати за п’ять тактів комутації декад лічильного блока з блоком перетворювача коду і, власне, самого перетворення коду 3321 у десятковий унітарний код, швидкодія розробленого функціонального вузла буде дуже низькою (адже в цьому випадку розроблений вузол мав би працювати так: після підрахунку кожного вхідного числового імпульсу потрібно виконувати п’ять тактів виведення результату підрахунку) або ж функціональний вузол взагалі не буде працювати правильно (відповідно до поставленого в курсовому проекті завдання).

Крім того, слід звернути увагу на те, що невеликий логічний набір інтегральних схем серії К500 та К1500 змушує здійснювати заміну потрібних для проектування логічних елементів, яких немає в даних серіях, іншими (часто виникає необхідність проектувати функціональний вузол на базових логічних елементах), що, в свою чергу, приводить до збільшення кількості використовуваних елементів та ускладнення принципової схеми пристрою, і тому особливо вимагає пошуку оптимальних варіантів реалізації складових блоків розроблюваного функціонального вузла.

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

8 |

|

Зм. Арк. № докум. Підпис Дaта |

|

31

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

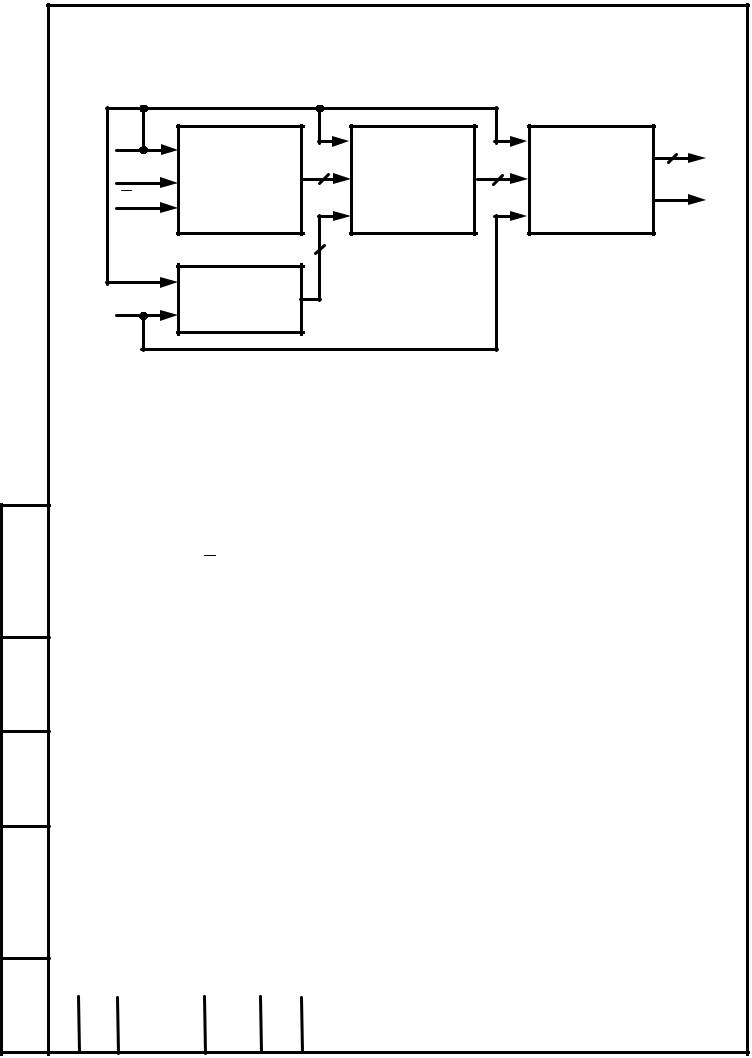

3. Структурна схема двійково-десяткового лічильника у коді 3321

Структурна схема спроектованого лічильника зображена на рис.3.1.

V |

|

|

|

|

|

Q0-Q9 |

Лічильний |

|

|

|

Перетворювач |

10 |

|

|

20 |

|

4 |

|||

+1 |

блок |

Схема |

коду 3321 |

Р |

||

R |

з розрядністю |

|

комутації |

|

у десятковий |

|

5 декад |

|

|

|

унітарний код |

|

|

|

|

|

|

|

||

|

|

3 |

|

|

|

|

С |

Генератор |

|

|

|

|

|

адрес декад |

|

|

|

|

|

Рис.3.1. Структурна схема двійково-десяткового лічильника у коді 3321

Схема складається з таких основних елементів: лічильного блоку (це, фактично, двійково-десятковий лічильник у коді 3321 з розрядністю 5 декад, що працює в режимі підрахунку вхідних імпульсів, які подаються на вхід +1, і має можливість обнулення при подачі сигналу високого рівня на інверсний вхід R ), схеми комутації, перетворювача коду 3321 у десятковий унітарний код та генератора адрес декад лічильного блока.

Схема комутації, роль якої, фактично, виконує спеціалізований мультиплексор, здійснює почергове з’єднання кожної з п’яти декад лічильного блока, починаючи з молодшої, зі входом перетворювача коду 3321 у десятковий унітарний код.

Для реалізації подекадної вибірки результатів підрахунку вхідних імпульсів використовуються генератор адрес декад, запуск якого здійснюється тактовим сигналом С.

Усхемі також передбачено вхід V для керуючого (дозволяючого) сигналу, високий рівень якого дозволяє роботу окремих елементів схеми і, відповідно, схеми в цілому.

Узагальному, спроектований пристрій функціонує так. Двійково-

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

9 |

|

Зм. Арк. № докум. Підпис Дaта |

|

32

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

десятковий лічильник у коді 3321 підраховує кількість імпульсів, що подаються на його вхід +1. Після закінчення підрахунку на генератор адрес декад подаються 5 тактів, при надходженні кожного з яких генерується чергова адреса декади, внаслідок чого схема комутації з’єднує декаду із входом перетворювача коду. Після перетворення останньої декади схема лічильника готова до підрахунку нової серії числових імпульсів. Зважаючи на те, що двійково-десятковий лічильник має розрядність 5 декад, максимальна кількість імпульсів, що може бути підрахована (без втрат), становить 99999. Під час перетворення коду 3321 у десятковий код імпульси на вхід +1 подавати не варто, оскільки вони можуть змінити вміст лічильника і тим самим спотворити результат попереднього підрахунку.

У зв’язку з тим, що, відповідно до завдання курсового проекту, підрахунок кількості імпульсів лічильника повинен здійснюватися у коді 3321, а виведення результату має відбуватися у десятковому унітарному коді, то спроектована схема кілька разів виконує перекодування результату підрахунку імпульсів. Враховуючи те, що лічильника імпульсів у коді 3321 не існує і його слід спроектувати на основі інших елементів (наприклад, на основі лічильника у коді 8421), код кількості імпульсів, підрахованих однією декадою, зазнає трьох перетворень, що ілюструє табл.3.1.

Таблиця 3.1

|

Десяткове |

|

|

|

|

|

|

|

число, |

Двійково- |

Двійково- |

Десятковий |

|

|

|

|

к-сть |

десятковий |

десятковий |

|

|||

|

унітарний код |

|

|

||||

|

вхідних |

код 8421 |

код 3321 |

|

|||

|

|

|

|

||||

|

імпульсів |

|

|

|

|

|

|

|

0 |

0000 |

|

0000 |

0000000001 |

|

|

|

1 |

0001 |

|

0001 |

0000000010 |

|

|

|

2 |

0010 |

|

0010 |

0000000100 |

|

|

|

3 |

0011 |

|

0011 |

0000001000 |

|

|

|

4 |

0100 |

|

0101 |

0000010000 |

|

|

|

5 |

0101 |

|

0110 |

0000100000 |

|

|

|

6 |

0110 |

|

0111 |

0001000000 |

|

|

|

7 |

0111 |

|

1101 |

0010000000 |

|

|

|

8 |

0100 |

|

1110 |

0100000000 |

|

|

|

9 |

1001 |

|

1111 |

1000000000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

362.6050102 1 511 ПЗ |

Арк. |

||

|

|

|

|

|

|||

|

|

|

|

10 |

|||

Зм. Арк. № докум. |

Підпис Дaта |

|

|

|

|

||

33

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

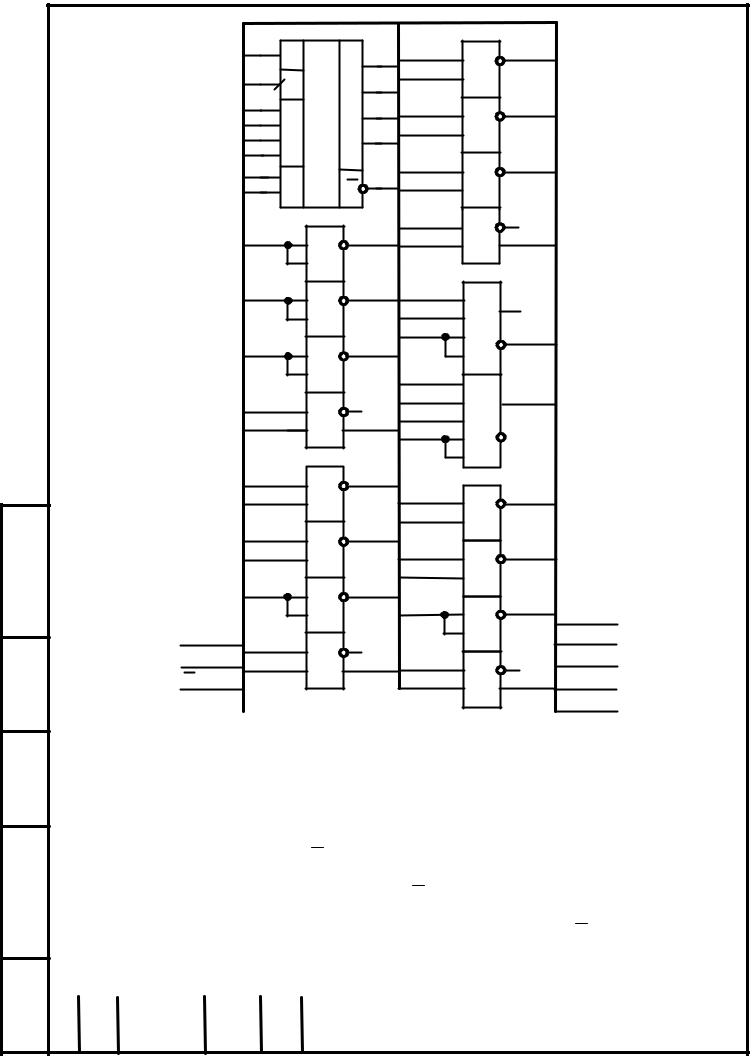

4.Функціональна схема лічильника

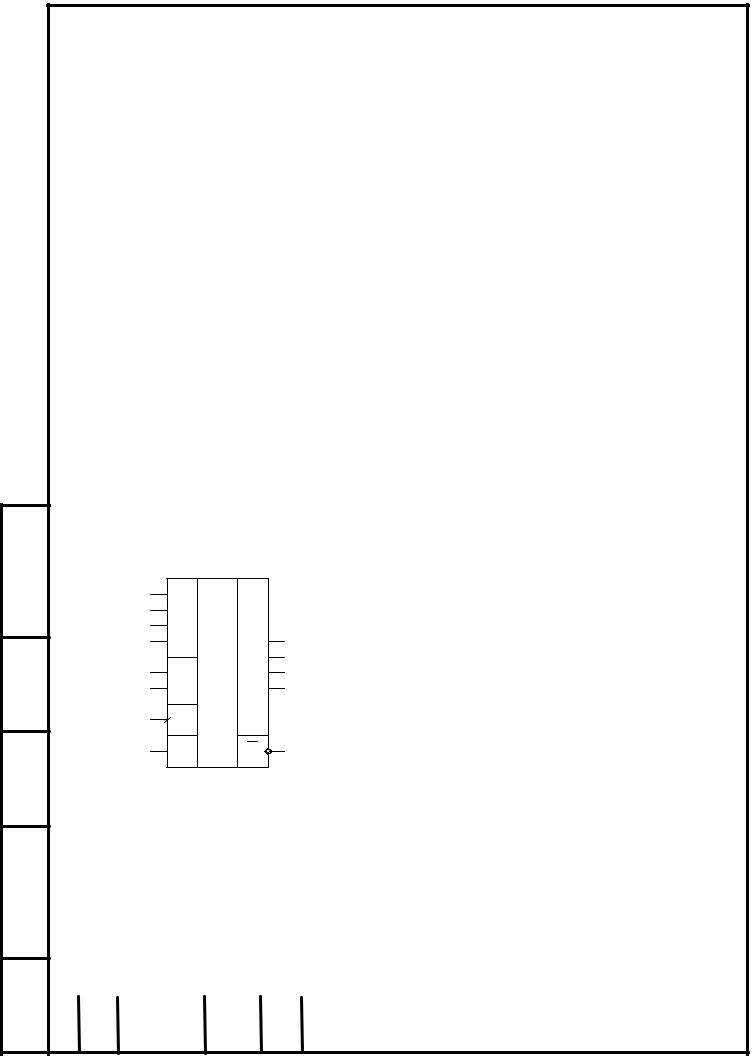

Унаборі ІС К500 є промисловий двійково-десятковий лічильник для коду 8421 К500ИЕ137 (рис.4.1), на базі якого можна синтезувати лічильник

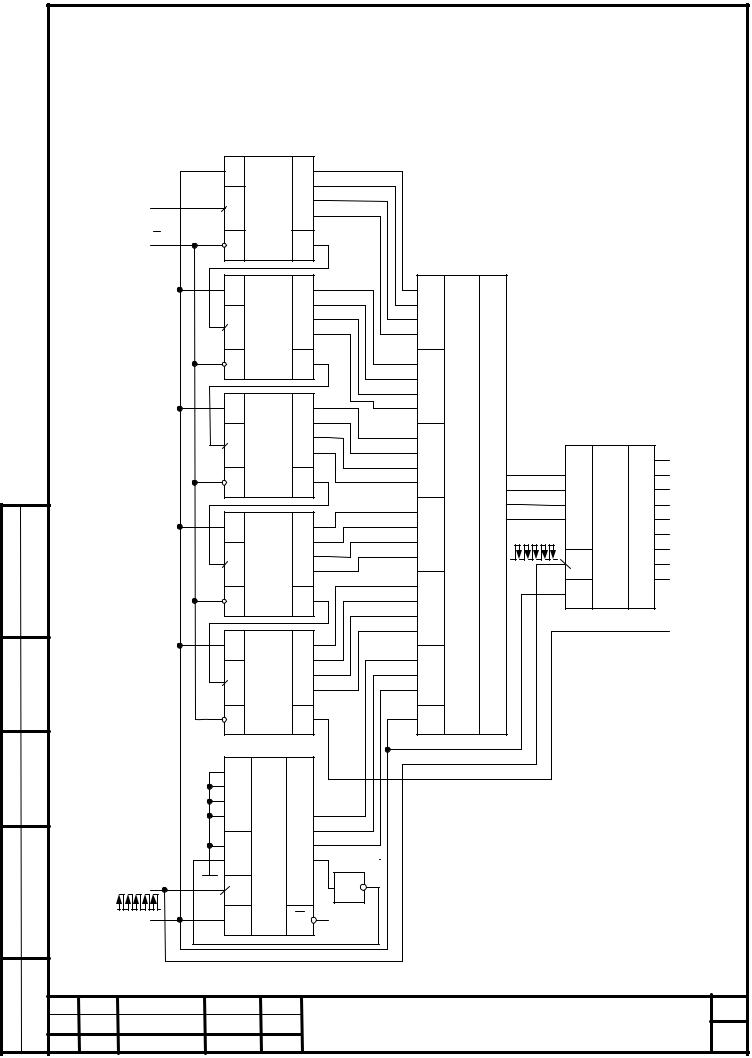

укоді 3321. На функціональній схемі (рис.4.2) кожна декада лічильного блока розробленого пристрою зображена елементом СТ2/10, виходи якого з’єднані з відповідними входами схеми комутації, зображеної блоком MUX, котрий фактично виконує роль мультиплексора, що комутує п’ять 4- розрядних шин в одну 4-розрядну. Адреса кожної шини задається генератором адрес декад, роль якого виконує мікросхема лічильника К500ИЕ137 при подачі на її вхід +1 п’ять тактових імпульсів.

Мікросхема К500ИЕ137 є універсальним реверсивним двійководесятковим лічильником, що може працювати при тактовій частоті більше 100МГц. Чотири режими роботи лічильника програмуються за двома входами S1 і S2, як показано в таблиці 4.1 [4; 5; 6; 7]. Режим попередньої установки дозволяє завантажити в лічильник початкові дані підрахунку,

наявні на входах D0-D3.

12 |

D0 |

CT |

|

11 |

D1 |

2/10 |

|

6 |

D2 |

|

|

5 |

D3 |

1 |

14 |

9 |

|

2 |

15 |

S1 |

4 |

2 |

|

7 |

S2 |

8 |

3 |

13 |

+1 |

|

|

10 |

V |

P |

4 |

Рис.4.1. Лічильник К500ИЕ137

Таблиця 4.1 Вибір режиму роботи лічильника

|

ВХІД |

РЕЖИМ |

|

|

|

|

|

S1 |

|

S2 |

|

|

|

||

0 |

|

0 |

Попередня установка (загрузка) |

|

|

|

|

0 |

|

1 |

Рахунок на збільшення |

|

|

|

|

1 |

|

0 |

Рахунок на зменшення |

1 |

|

1 |

Зберігання; зупинка рахунку |

Лічильник К500ИЕ137 працює в режимі додавання імпульсів і генерує адреси декад починаючи з 001 до 101. Комутація відповідної декади до входу блока перетворювача коду (позначеного на схемі – X/Y) здійснюється додатним перепадом тактових імпульсів (з 0 в 1). Від’ємним перепадом вказаних тактових імпульсів (з 1 в 0) здійснюється перетворення декади результа-

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

11 |

|

Зм. Арк. № докум. Підпис Дaта |

|

34

ту підрахунку імпульсів з коду 3321 в десятковий унітарний код. Керуючий сигнал V одночасно дозволяє роботу всіх складових вузлів структурної схеми лічильника. Сигнал переповнення Р останньої декади лічильного блока є сигналом переповнення всієї схеми розробленого лічильника.

Підпис і дата |

|

|

|

|

|

|

|

Інв. № дубл. |

|

|

|

|

|

|

|

Взам. інв. № |

|

|

|

|

|

|

|

Підпис і дата |

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

№оригін |

|

|

Рис.4.2. Функціональна схема лічильника у коді 3321 |

|

|||

|

|

|

|

362.6050102 1 511 ПЗ |

Арк. |

||

. |

|

|

|

|

|

||

Інв |

|

|

|

|

12 |

||

Зм. |

Арк. |

№ докум. |

Підпис |

Дaта |

|||

|

|||||||

|

|

|

|

|

35 |

|

|

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

5.Принципова схема пристрою

5.1.Проектування лічильного блока

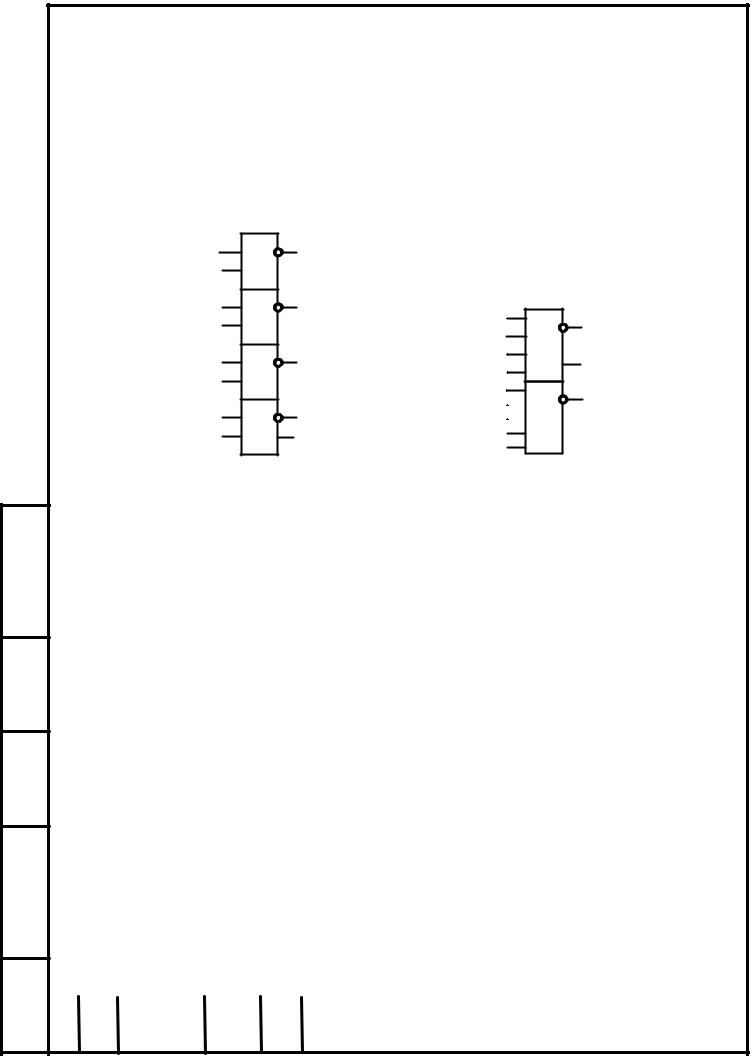

Для проектування лічильного блока в коді 3321 використовуються мікросхеми логічних елементів АБО-НЕ типу К500ЛМ102 (рис.5.1) та К500ЛМ109 (рис.5.2), а також мікросхема двійково-десяткового лічильника у коді 8421 – К500ИЕ137, яка описана в розділі 4.

4 |

1 |

2 |

|

|

|

5 |

|

|

|

|

|

6 |

1 |

3 |

4 |

|

|

7 |

|

|

1 |

3 |

|

|

|

5 |

|||

|

|

|

|

|

|

10 |

1 |

14 |

6 |

|

2 |

7 |

|

||||

11 |

|

|

|

|

|

|

|

9 |

1 |

14 |

|

|

|

|

|||

|

1 |

15 |

10 |

||

12 |

|

|

|||

11 |

|

|

|||

13 |

|

9 |

12 |

|

15 |

|

|

|

13 |

|

|

Рис.5.1. Логічний елемент |

Рис.5.2. Логічний елемент |

||||

АБО-НЕ К500ЛМ102 |

АБО-НЕ К500ЛМ109 |

||||

Мікросхема К500ЛМ102 виконує логічну функцію АБО-НЕ. В одному корпусі розміщено чотири логічні елементи. Четвертий елемент має доповнюючий неінвертований вихід, при використанні якого елемент працює як АБО. Мікросхема К500ЛМ109 виконує функції АБО-НЕ (при використанні інверсного виходу) та АБО (при використанні прямого виходу). В одному корпусі розміщені два логічні елементи на чотири та п’ять входів.

Обидві мікросхеми виготовлені на основі технології емітерно-зв’язної логіки, параметри та експлуатаційні дані якої наведено в таблиці 5.1, і випускаються в пластмасовому корпусі [4].

|

|

|

Таблиця 5.1 |

||

|

Параметри та експлуатаційні дані логічних елементів серії К500 |

|

|||

|

|

|

|

|

|

|

І спожив – не більше 26 мА |

|

U1вих – не менше 0,98 В |

|

|

|

І0 вх – не менше 0,5 мкА |

|

t1,0затр р і t0,1затр р – не більше 2,9 нс |

|

|

|

І1вх – не більше 265 мкА |

|

Uживл = -5,2 В+-5% |

|

|

|

U0вих – не більше (-1,63) В |

|

Tсередов – від -10 до +75 °С |

|

|

|

|

|

|

|

|

|

|

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

|

||

|

|

13 |

|||

Зм. Арк. № докум. Підпис Дaта |

|

|

|

||

|

|

36 |

|

|

|

|

|

|

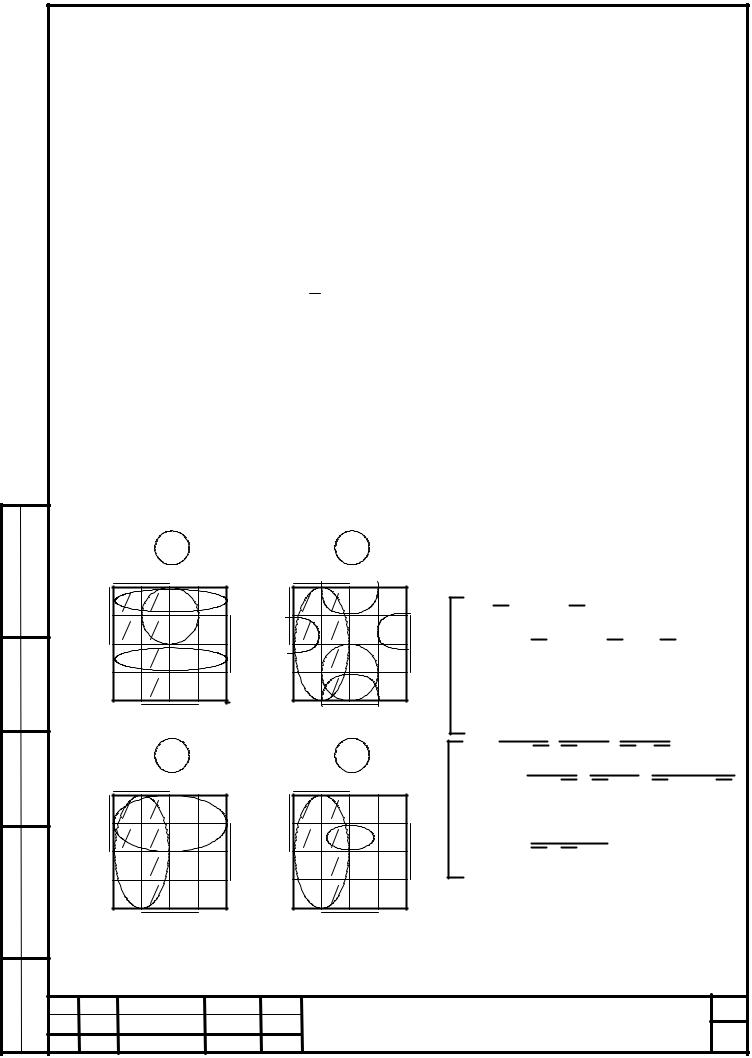

Принципова |

схема |

однієї декади лічильного блока в коді 3321 |

|||||||||

|

зображена на рис.5.4, і працює так. Кількість вхідних імпульсів, що |

|||||||||||||

|

надходять на вхід +1 схеми, підрахованих лічильником DD1 –К500ИЕ137, у |

|||||||||||||

|

вигляді двійково-десяткового коду 8421 (виходи лічильника –Q0-Q3), |

|||||||||||||

|

схемою дешифратора, зібраного на мікросхемах К500ЛМ102 та К500ЛМ109 |

|||||||||||||

|

– DD2-DD6, перетворюється у код 3321 і подається на виходи Q’0-Q’3 схеми |

|||||||||||||

|

(на функціональній схемі позначені як виходи 1233 відповідно). Схема |

|||||||||||||

|

лічильника дозволяє обнулити його вміст у будь-який момент часу, подаючи |

|||||||||||||

|

інверсний сигнал на вхід |

R . Вхід V є дозволяючим для функціонування |

||||||||||||

|

лічильника DD1 та схеми в цілому. Рівняння вихідних функцій |

|||||||||||||

|

дешифратора, побудовані відповідно до табл.3.1 і мінімізовані з допомогою |

|||||||||||||

|

діаграм Вейча (рис.5.3), мають вигляд (5.1). Враховуючи те, що в наборі |

|||||||||||||

|

емітерно-зв’язної логіки не існує логічних елементів &, використовуючи |

|||||||||||||

|

закони де Моргана, рівняння (5.1) були перетворені в (5.2) для реалізації їх у |

|||||||||||||

|

базисі мікросхем К500ЛМ102 та К500ЛМ109. |

|||||||||||||

і дата |

|

|

|

Q’0 |

|

|

|

Q’1 |

|

|

|

|||

|

|

Q3 |

|

|

|

Q3 |

|

|

|

|

||||

Підпис |

|

|

|

|

|

|

|

|

|

|||||

|

Q2 |

012 |

014 |

1 6 |

1 4 |

Q2 |

012 |

014 |

1 6 |

0 4 |

|

Q’0=Q2Q0+Q2Q0+Q2Q1 |

||

|

|

013 |

015 |

1 7 |

0 5 |

013 |

015 |

0 7 |

1 5 |

|

||||

. |

|

|

Q0 |

Q0 |

Q’1= Q3+Q2Q1+Q1Q0+Q2Q1Q0 |

|||||||||

дубл |

|

|

1 9 |

011 |

1 3 |

1 1 |

1 9 |

011 |

1 3 |

0 1 |

||||

|

|

|

|

|||||||||||

|

|

|

|

(5.1) |

||||||||||

№ |

|

|

0 8 |

010 |

0 2 |

0 0 |

|

1 8 |

010 |

1 2 |

0 0 |

|

Q’2= Q3+Q2 |

|

Інв. |

|

|

|

Q1 |

|

|

|

Q1 |

|

|

Q’3= Q3+Q2Q1Q0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

. № |

|

|

|

Q’2 |

|

|

|

Q’3 |

|

|

Q’0= Q2+Q0+Q2+Q0+Q2+Q1 |

|||

. інв |

|

|

Q3 |

|

|

|

Q3 |

|

|

|

Q’1= Q3+Q2+Q1+Q1+Q0+Q2+Q1+Q0 |

|||

Взам |

|

|

|

|

|

|

|

|

||||||

|

Q2 |

012 |

014 |

16 |

14 |

Q2 |

012 |

014 |

0 6 |

0 4 |

|

(5.2) |

||

|

|

013 |

015 |

1 7 |

15 |

013 |

015 |

1 7 |

0 5 |

|

Q’2= Q3+Q2 |

|||

і дата |

|

|

Q0 |

Q0 |

Q’3= Q3+Q2+Q1+Q0 |

|||||||||

|

|

1 9 |

011 |

0 3 |

0 1 |

|

1 9 |

011 |

0 3 |

0 1 |

|

|||

|

|

|

|

|

||||||||||

|

|

1 8 |

010 |

0 2 |

0 0 |

|

1 8 |

010 |

0 2 |

0 0 |

|

|

||

Підпис |

|

|

|

|

|

|||||||||

|

|

|

Q1 |

|

|

|

Q1 |

|

|

|

||||

Рис.5.3. Діаграми Вейча для мінімізації рівнянь |

|

|||||||||||||

. |

|

|||||||||||||

вихідних функцій дешифратора лічильного блока |

||||||||||||||

№оригін |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Арк. |

||

. |

|

|

|

|

|

|

|

|

|

|

|

362.6050102 1 511 ПЗ |

||

Інв |

|

|

|

|

|

|

|

|

|

|

|

|||

Зм. |

Арк. |

№ докум. |

Підпис Дaта |

|

|

|

|

|

14 |

|||||

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

|

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

|

|

2 |

10 |

|

DD1 |

|

|

|

|

|

DD4 |

|

|

|

|

|

|

V |

СТ |

Q0 14 |

5 |

7 |

4 |

1 |

2 |

18 |

|

|

|||

|

|

1 |

13 |

|

2/10 |

11 |

5 |

|

|

|

|

|

|||

|

|

+1 |

|

|

15 |

6 |

|

|

|

|

|

||||

|

|

|

Q1 |

|

|

|

|

|

|

|

|||||

|

|

4 |

12 |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

D0 |

|

Q2 |

2 |

7 |

11 |

6 |

3 |

19 |

|

|

|||

|

|

4 |

11 |

D1 |

|

|

|

5 |

7 |

|

|

|

|

|

|

|

|

4 |

6 |

|

|

3 |

8 |

|

|

|

|

|

|||

|

|

D2 |

|

Q3 |

|

|

|

|

|

||||||

|

|

4 |

5 |

D3 |

|

|

|

|

7 |

10 |

1 |

14 |

22 |

|

|

|

|

4 |

9 |

S1 |

|

|

|

|

|

|

|||||

|

|

|

|

4 |

9 |

10 |

11 |

|

|

|

|

|

|||

|

|

3 |

7 |

|

P |

|

|

|

|

|

|||||

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD2 |

|

|

|

22 |

12 |

1 |

15 |

|

|

|

|

|

5 |

|

4 |

1 |

2 |

|

10 |

23 |

13 |

|

9 |

25 |

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD5 |

|

|

|

|

|

|

6 |

|

6 |

1 |

3 |

|

11 12 |

4 |

1 |

2 |

|

|

|

|

|

|

|

|

7 |

|

|

|

|

6 |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

10 |

6 |

|

3 |

20 |

|

|

|

|

7 |

|

10 |

1 |

14 |

|

12 |

|

7 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

11 |

|

|

|

|

8 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

18 |

10 |

15 |

21 |

|

|

|

|

|

10 |

|

12 |

1 |

15 |

|

|

|

|

|

||||

|

|

|

|

|

19 |

11 |

|

|

|

|

|

||||

|

|

11 |

|

13 |

|

9 |

|

13 |

|

14 |

|

|

|

||

|

|

|

|

|

20 |

12 |

|

|

|

|

|||||

|

|

|

|

|

DD3 |

|

|

|

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

4 |

1 |

2 |

|

14 |

|

|

DD6 |

|

|

|

|

|

|

13 |

|

5 |

|

|

|

|

12 |

4 |

1 |

2 |

23 |

|

|

|

|

|

|

|

|

|

|

|

11 |

5 |

|

|

|

|

|

|

|

8 |

|

6 |

1 |

3 |

|

16 |

|

|

|

|

|

|

|

|

|

7 |

|

7 |

|

|

|

|

12 |

6 |

1 |

3 |

24 |

|

|

|

|

|

|

|

|

|

|

|

5 |

7 |

|

|

|

|

|

|

|

16 |

|

10 |

1 |

14 |

|

17 |

|

|

1 |

|

|

|

|

|

|

|

|

11 |

|

|

|

|

9 |

10 |

14 |

27 |

15 |

Q'3 (3) |

|

|

|

|

|

|

|

|

|

|

|

11 |

|

|

|

||

+1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

17 |

Q'2 (3) |

|

8 |

|

12 |

1 |

15 |

|

|

|

|

|

|

|

||||

V |

2 |

14 |

|

13 |

|

9 |

|

15 |

25 |

12 |

1 |

15 |

|

21 |

Q'1 (2) |

R |

3 |

|

|

|

|

|

|

|

24 |

13 |

|

9 |

26 26 |

Q'0 (1) |

|

GND |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

27 |

P' |

Рис.5.4. Схема однієї декади лічильного блока

Оскільки підрахунок вхідних імпульсів лічильником К500ИЕ137 здійснюється по передньому фронту імпульсу (при перепаді сигналу з 0 в 1),

а сигнал переповнення P даної мікросхеми інверсний (тобто при надходженні 10-го імпульсу на виході P відбувається перепад сигналу з 1 в 0), то сигнал переповнення кожної декади лічильника P інвертується й подається на лічильний вхід наступної декади, розширюючи в такий спосіб

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

15 |

|

Зм. Арк. № докум. Підпис Дaта |

|

|

|

38 |

|

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

розрядність лічильного блока.

Спосіб з’єднання декад лічильника, подача вхідних імпульсів на лічильний вхід першої декади, дозволяючого сигналу і сигналу обнулення всіх декад зображені на функціональній схемі спроектованого пристрою

(рис.4.2).

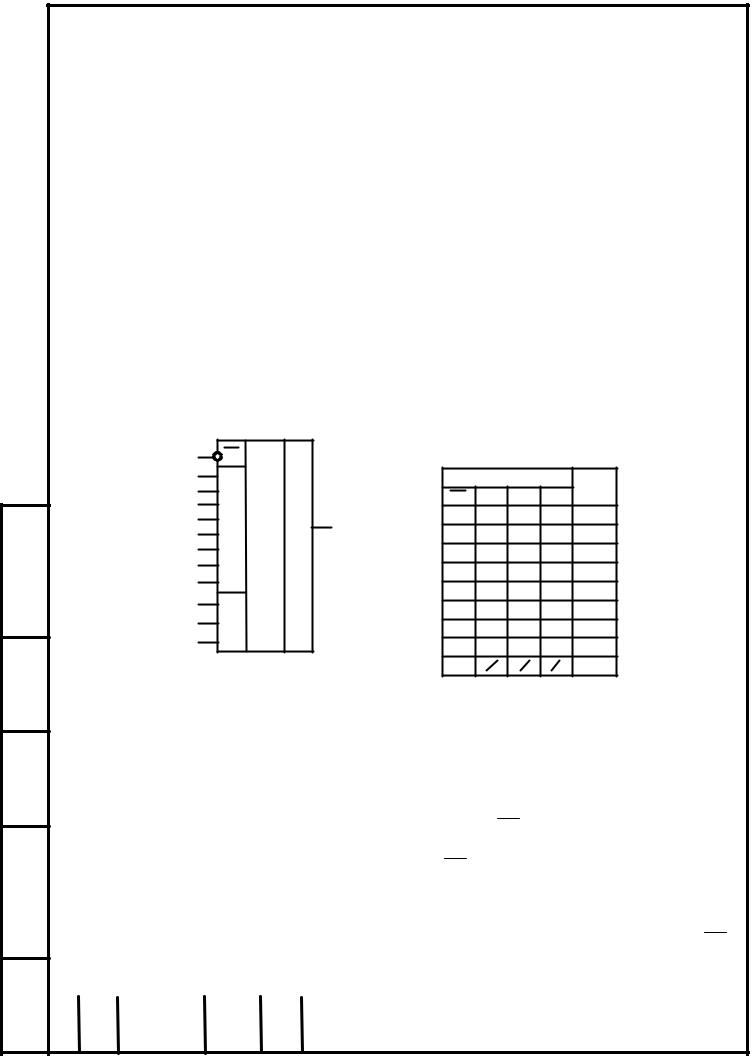

5.2. Проектування схеми комутації

Схема комутації двійково-десяткового лічильника у коді 3321 зібрана на мікросхемах К500ИД164. Вибір потрібної декади здійснюється з допомогою генератора адрес декад К500ИЕ137, як це описано в розділі 3.

Мікросхема К500ИД164 – мультиплексор, який працює як восьмиканальний селектор даних, наявних на його входах D0-D7 (рис.5.5) [4].

|

|

|

|

|

|

|

|

|

Таблиця 5.2 |

2 |

E0 |

MUX |

|

Стан мультиплексора К500ИД164 |

|||||

6 |

|

|

|

Вхід управління |

Код на |

||||

5 |

D0 |

|

|

|

|||||

4 |

D1 |

|

|

|

ЕО |

S3 |

S2 |

S1 |

вих.Q |

3 |

D2 |

|

|

15 |

0 |

0 |

0 |

0 |

D0 |

11 |

D3 |

|

Q |

||||||

|

|

|

|

|

|

||||

12 |

D4 |

|

|

|

0 |

0 |

0 |

1 |

D1 |

13 |

D5 |

|

|

|

0 |

0 |

1 |

0 |

D2 |

D6 |

|

|

|

0 |

0 |

1 |

1 |

D3 |

|

14 |

D7 |

|

|

|

1 |

||||

7 |

S1 |

|

|

|

0 |

0 |

0 |

D4 |

|

|

|

|

0 |

1 |

0 |

1 |

D5 |

||

9 |

S2 |

|

|

|

|||||

|

|

|

0 |

1 |

1 |

0 |

D6 |

||

10 |

S3 |

|

|

|

|||||

|

|

|

0 |

1 |

1 |

1 |

D7 |

||

|

|

|

|

|

|||||

Рис.5.5. Мікросхема К500ИД164 |

1 |

0 |

0 |

0 |

0 |

||||

Ці дані почергово можуть з’являтися на виході Q відповідно до коду вибору вхідної лінії, заданому на адресних входах S1, S2 та S3. Дев’ятий стан (напруга низького рівня) з’явиться на виході Q при забороні

мультиплексування, коли на дозволяючий вхід E0 буде поданий високий рівень (табл.5.2). З допомогою виводу E0 можна збільшити кількість каналів мультиплексора, з’єднуючи разом кілька мультиплексорів. Потрібну групу каналів включають в електричне коло комутації, подавши на вхід E0 відповідної мікросхеми низький рівень.

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

16 |

|

Зм. Арк. № докум. Підпис Дaта |

|

|

|

39 |

|