Розрахунково-графічна робота з КС. Методичка

.pdf

Чернівецький національний університет імені Юрія Федьковича

Факультет комп’ютерних наук Кафедра комп’ютерних систем та мереж

Спеціальність 6.050102 – комп’ютерні системи і мережі

.

.

.

|

|

|

ЗАТВЕРДЖУЮ |

||

Зав. кафедрою |

|||||

|

|

|

|

Мельничук С.В. |

|

„ |

|

” |

|

|

2011 р. |

ЗАВДАННЯ на курсовий проект студенту

Прізвище Ім’я Побатькові

|

|

|

(прізвище, ім’я, по батькові) |

|

|

|

|

|

|

||

1. |

Тема проекту |

|

Двійково-десятковий лічильник у коді 3321 . |

|

|||||||

|

|

|

|

|

|

||||||

затверджена наказом по університету від „ 24 ” 10 |

|

2011 р., протокол № 3 |

. |

||||||||

|

|

|

|

|

|

|

|

||||

2. |

Термін подачі студентом закінченого проекту |

|

|

25 грудня |

2011 р. |

|

|||||

3. |

Вихідні дані до проекту |

Розробити |

функціональний |

вузол двійково- |

|||||||

десяткового лічильника у коді 3321 з попереднім встановленням нуля. Розрядність – 5 декад. Введення даних – в число-імпульсному коді (нормованому до 10). Виведення – у вигляді десяткового унітарного коду, по-декадно. Електричну принципову схему пристрою розробити в

логічному базисі набору інтегральних схем – К500, К1500 |

4. Зміст розрахунково-пояснювальної записки (перелік питань, які потрібно розробити) |

1)Описати основні типи лічильників, їх параметри, характеристики та принцип роботи

2)Розробити структурну схему заданого пристрою

3)Розробити функціональну схему пристрою

4)Розробити принципову схему пристрою

5)Скласти перелік елементів до принципової схеми

6)Побудувати часові діаграми функціонування пристрою і розрахувати

його складність та швидкодію .

7) Змоделювати спроектовану схему лічильника у віртуальному

|

симуляторі електронних схем – Multisim |

. |

|

5. |

Перелік графічного матеріалу (з точним зазначенням обов’язкових креслень) |

|

|

1)Структурна схема розробленого пристрою (Ф.А4/Ф.А3)

2)Функціональна схема пристрою (Ф.А4)

3)Принципова схема розробленого функціонального вузла (Ф.А4/Ф.А3)

4)Перелік елементів до принципової схеми (Ф.А4)

5)Часові діаграми функціонування пристрою (Ф.А4)

6)Ілюстрації результатів моделювання роботи пристрою (Ф.А4/Ф.А3)

20

6. Консультанти з проекту, із зазначенням розділів проекту, що стосуються їх

|

|

Підпис, дата |

|

Розділ |

Консультант |

|

|

Завдання |

Завдання |

||

|

|

видав |

прийняв |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7. Дата видачі завдання

|

Керівник |

|

|

|

|

|

|

|

|

(підпис) |

|

|

Завдання прийняв до виконання |

|

|||

|

|

|

|

(підпис) |

|

|

КАЛЕНДАРНИЙ ПЛАН |

|

|||

|

|

|

|

||

№ |

Етапи проекту |

Терміни виконання |

Примітки |

||

п/п |

етапів проекту |

||||

|

|

|

|

||

1 |

Огляд літератури з теми курсового проекту |

1.11.11 – 6.11.11 |

|

||

|

|

|

|

||

2 |

Проектування структурної схеми пристрою |

7.11.11 – 9.11.11 |

|

||

3 |

Проектування функціональної схеми двійково- |

10.11.11 – 14.11.11 |

|

||

|

|

|

|

|

|

|

десяткового лічильника у коді 3321 |

|

|

|

|

4 |

Проектування принципової схеми і складання |

15.11.11 – 24.11.11 |

|

||

|

|

|

|

|

|

|

переліку елементів до неї |

|

|

|

|

|

|

|

|

||

5 |

Побудова часових діаграм функціонування |

25.11.11 – 26.11.11 |

|

||

|

схеми спроектованого вузла і розрахунок її |

|

|

|

|

|

|

|

|

|

|

|

складності та швидкодії |

|

|

|

|

6 |

Моделювання спроектованої схеми лічильника |

27.11.11 – 10.12.11 |

|

||

|

|

|

|

|

|

|

у віртуальному симуляторі електронних схем |

|

|

|

|

|

Multisim |

|

|

|

|

|

|

|

|

||

7 |

Оформлення курсового проекту |

11.12.11 – 25.12.11 |

|

||

8 |

Захист курсового проекту |

за графіком |

|

||

|

|

|

|

|

|

Студент

(підпис)

Керівник проекту

(підпис)

21

АНОТАЦІЯ

Укурсовому проекті представлена розробка функціонального вузла двійково-десяткового лічильника у коді 3321 з попереднім встановленням нуля, розрядністю – 5 декад, введенням даних у числоімпульсному коді (нормованому до 10) та виведенням – у вигляді десяткового унітарного коду, подекадно.

Відповідно до технічного завдання, електрична принципова схема пристрою спроектована в логічному базисі набору інтегральних схем – К500 та К1500. Побудовано часові діаграми функціонування принципової схеми пристрою, проведено аналіз її складності та розрахунок швидкодії і граничної робочої частоти.

Упояснювальній записці до технічної документації проекту детально розглянуто етапи проектування пристрою, аналіз його працездатності та результати моделювання принципової схеми у віртуальному симуляторі електронних схем NI Multisim11.0, зроблено висновки та наведено список використаних літературних джерел.

Креслення структурної, функціональної та принципової схем розробленого двійково-десяткового лічильника, перелік елементів та часові діаграми функціонування принципової схеми, а також ілюстрації результатів моделювання роботи пристрою оформлені відповідно до вимог ЄСКД і наведені в графічній частині технічної документації проекту.

Курсовий проект містить 21 рисунок, 4 таблиці, 6 креслень, перелік елементів до принципової схеми розробленого пристрою і має загальний обсяг 45 сторінок друкованого тексту.

22

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

|

Фор- |

|

Зо- |

Поз. |

|

Позначення |

Найменування |

|

|

|

|

Кіль- |

Прим. |

|||

|

мат |

|

на |

|

|

|

|

|

|

|

|

|

|

кість |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

Документація загальна |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Новорозроблена |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

А4 |

|

|

|

|

362.6050102 1 511 ПЗ |

Двійково-десятковий |

|

|

|

|

1 |

|

|||

|

|

|

|

|

|

|

|

|

|

лічильник у коді 3321 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Пояснювальна записка |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

А4 |

|

|

|

|

|

362.6050102 1 511 Е1 |

Двійково-десятковий |

|

|

|

|

1 |

|

||

|

|

|

|

|

|

|

|

|

|

лічильник у коді 3321 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Схема електрична |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

структурна |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

А4 |

|

|

|

|

|

362.6050102 1 511 Е2 |

Двійково-десятковий |

|

|

|

|

1 |

|

||

|

|

|

|

|

|

|

|

|

|

лічильник у коді 3321 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Схема електрична |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

функціональна |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

А3,А4 |

|

|

|

|

|

362.6050102 1 511 Е3 |

Двійково-десятковий |

|

|

|

|

2 |

|

||

|

|

|

|

|

|

|

|

|

|

лічильник у коді 3321 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Схема електрична |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

принципова |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

А4 |

|

|

|

|

362.6050102 1 511 ПЕ3 |

Двійково-десятковий |

|

|

|

|

1 |

|

|||

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

лічильник у коді 3321 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Перелік елементів |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

А4 |

|

|

|

|

|

362.6050102 1 511 Д1 |

Двійково-десятковий |

|

|

|

|

1 |

|

||

|

|

|

|

|

|

|

|

|

|

лічильник у коді 3321 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Часові діаграми роботи |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

принципової схеми однієї |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

декади лічильника |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

А4 |

|

|

|

|

|

362.6050102 1 511 Д2 |

Двійково-десятковий |

|

|

|

|

1 |

|

||

|

|

|

|

|

|

|

|

|

|

лічильник у коді 3321 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Часові діаграми роботи |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

принципової схеми комутації |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

та перетворювача коду |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

А3 |

|

|

|

|

362.6050102 1 511 М3 |

Двійково-десятковий |

|

|

|

|

3 |

|

|||

|

|

|

|

|

|

|

|

|

|

лічильник у коді 3321 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ілюстрація результатів |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

моделювання роботи |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

пристрою |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

362.6050102 1 511 ОА |

|

|||||

|

Зм. Арк. |

№ докум. |

Підпис Дaта |

|

||||||||||||

|

|

|

|

|

|

|

|

|||||||||

|

Розроб. |

|

Прізвище І.П. |

|

|

|

|

Літ. |

|

Арк. |

Аркушів |

|||||

|

Перевір. |

Прізвище І.П. |

|

|

Двійково-десятковий |

|

|

|

1 |

1 |

||||||

|

|

|

|

|

||||||||||||

|

Реценз. |

|

|

|

|

|

|

лічильник у коді 3321. |

|

Кафедра комп’ютерних |

||||||

|

Н. контр. |

|

|

|

|

|

|

Опис альбому |

|

|

|

систем та мереж, |

||||

|

Затв. |

|

|

|

|

|

|

|

|

|

|

|

|

група 321 |

||

23

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

ЗМІСТ Вступ…………………………………………………………………………... 2

1.Класифікація, параметри і характеристики лічильників……………….. 3

2.Аналіз завдання на курсовий проект.…………………………………..... 7

3.Структурна схема двійково-десяткового лічильника у коді 3321……... 9

4.Функціональна схема лічильника……………………………………..... 11

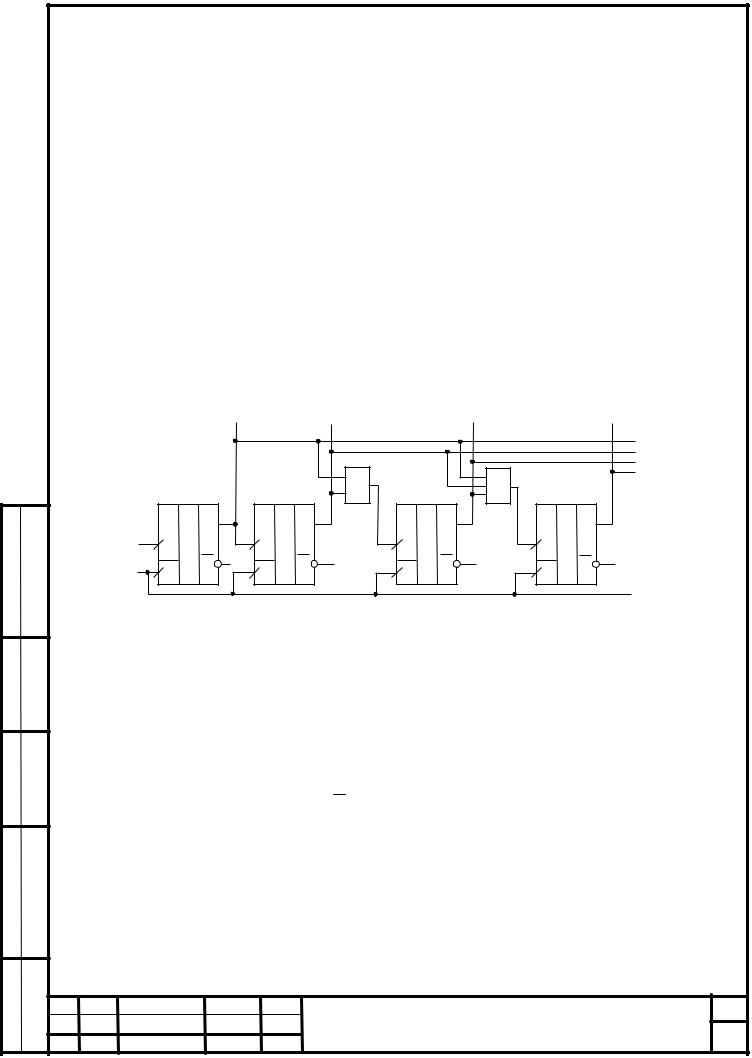

5.Принципова схема пристрою…………………..……………………...... 13

5.1.Проектування лічильного блока…………….……………………... 13

5.2.Проектування схеми комутації…………………………………….. 16

5.3.Проектування перетворювача коду 3321 у десятковий унітарний код………………………………………………………...18

6.Аналіз роботи пристрою……..…..……………………………………... 22

6.1.Побудова часових діаграм………………………………………..... 22

6.2.Розрахунок складності, швидкодії та максимальної частоти вхідного сигналу…………………………………………………… 23

7.Моделювання роботи спроектованої принципової схеми двійководесяткового лічильника у коді 3321.…………………………………… 27

Висновки…………………………………………………………………….. 28

Список використаних джерел……………………………………………… 29

|

№ докум. |

|

362.6050102 1 511 |

ПЗ |

|

|||||

Зм. Арк. |

Підпис Дaта |

|

|

|

|

|

||||

Розроб. |

Прізвище І.П. |

|

|

|

|

Літ. |

Арк. |

Аркушів |

||

Перевір. |

Прізвище І.П. |

|

|

|

Двійково-десятковий |

|

|

|

1 |

29 |

Реценз. |

|

|

|

|

лічильник у коді 3321. |

|

Кафедра комп’ютерних |

|||

Н. контр. |

|

|

|

|

Пояснювальна записка |

|

|

|

систем та мереж, |

|

Затв. |

|

|

|

|

|

|

|

|

група 321 |

|

24

Інв. № оригін. Підпис і дата Взам. інв. № Інв. № дубл. Підпис і дата

Вступ

У курсовому проекті розроблено функціональний вузол комп’ютерної схемотехніки, який являє собою двійково-десятковий лічильник у коді 3321 на п’ять декад з введенням даних у число-імпульсному коді та виведенням результату підрахунку вхідних імпульсів у десятковому унітарному коді, подекадно. Наведено структурну, функціональну і принципову схеми заданого пристрою; проведено моделювання і перевірку роботи принципової схеми, аналіз її складності, швидкодії, частоти та часу затримки; побудовано часові діаграми функціонування пристрою. Розробка принципової схеми виконана в логічному базисі набору інтегральних мікросхем серії К500 та К1500.

Особливістю завдання до курсового проекту є розробка схеми лічильника, що не виготовляється промисловістю. Тому обмежитися простим розширенням розрядності існуючих типових двійково-десяткових лічильників неможливо. Крім того, емітерно-зв’язна логіка, в базисі якої необхідно спроектувати принципову схему пристрою, містить досить обмежений набір інтегральних схем логічних елементів та функціональних вузлів (порівняно з ТТЛ чи КМОН-логікою), що суттєво ускладнює як сам процес проектування, так і принципову схему спроектованого пристрою.

При проектуванні лічильного блока пристрою, з двох розроблених варіантів – побудова однієї декади лічильного блока в коді 3321 на основі D- тригерів, що працюють у режимі Т-тригерів (Т-тригерів емітерно-зв’язної логіки немає), або використання готової мікросхеми лічильника у коді 8421 з подальшим дешифруванням результату підрахунку у код 3321, – було вибрано саме останній, оскільки в такому варіанті загальна кількість використаних інтегральних схем скорочується приблизно на половину, що не тільки суттєво спрощує загальну принципову схему розробленого пристрою, а й значною мірою збільшує його швидкодію, граничну частоту обробки вхідного коду, підвищує надійність.

|

362.6050102 1 511 ПЗ |

Арк. |

|

|

|

|

2 |

|

Зм. Арк. № докум. Підпис Дaта |

|

25

|

|

|

1. Класифікація, параметри і характеристики лічильників. |

|

||||||||||||||||

|

|

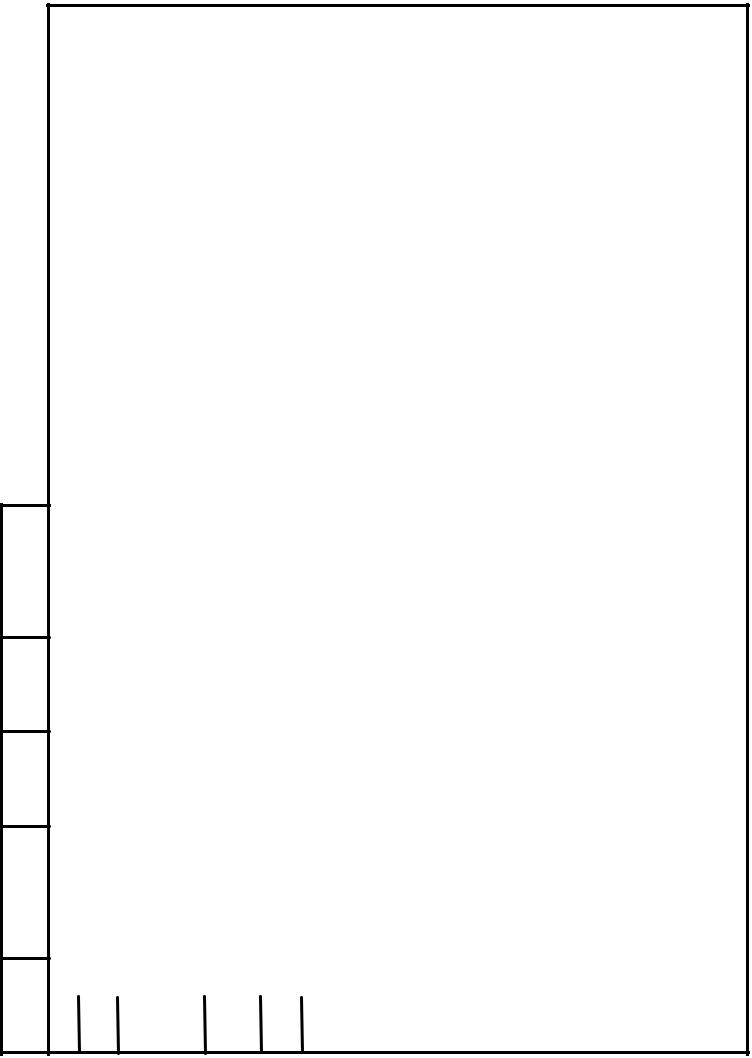

Лічильниками називаються послідовні логічні пристрої, призначені для |

||||||||||||||||||

|

перерахунку кількості імпульсів, а також для зберігання цієї інформації в |

|||||||||||||||||||

|

двійковому коді. Будують їх на основі динамічних Т-тригерів. Залежно від |

|||||||||||||||||||

|

схеми комутації тригерів та комбінаційної схеми керування лічильники |

|||||||||||||||||||

|

можуть забезпечувати як додавання одиничних імпульсів, тобто виконання |

|||||||||||||||||||

|

функцій інкременту, так і віднімання – функція декременту. |

|

|

|

||||||||||||||||

|

|

До основних параметрів лічильників відносять модуль перерахунку та |

||||||||||||||||||

|

час встановлення вихідного двійкового коду. |

|

|

|

|

|

|

|||||||||||||

|

|

За модулем перерахунку їх поділяють на двійкові (М = 2n) та двійково- |

||||||||||||||||||

|

кодовані, наприклад, двійково-десяткові, тобто з нецілочисловим модулем |

|||||||||||||||||||

|

М. За напрямком перерахунку: лічильники з додаванням, відніманням та |

|||||||||||||||||||

|

реверсивні. За способом організації міжкаскадних зв’язків виділяють |

|||||||||||||||||||

|

лічильники з послідовним, паралельним та комбінованим переносами. |

|

||||||||||||||||||

і дата |

|

Найпростіше |

реалізуються |

схеми |

з |

послідовим |

переносом |

на |

||||||||||||

динамічних Т-тригерах. В цьому випадку вихід попереднього каскаду |

||||||||||||||||||||

Підпис |

вмикається на вхід наступного (рис.1.1) [1, 2, 3]. |

|

|

|

|

|

||||||||||||||

|

|

|

|

Q0 |

|

|

Q1 |

|

|

Q2 |

|

Uвх |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

. |

|

|

|

Т |

|

|

Т Q |

|

|

Т Q |

|

Q0 |

|

|

|

|

|

|||

дубл |

|

|

Uвх Т |

Q |

|

|

Т |

|

|

|

|

t |

|

|||||||

|

|

|

|

|

Т |

|

|

|

|

|

Q1 |

|

|

|

t |

|

||||

№ |

|

|

|

|

Q |

|

|

Q |

|

|

Q |

|

|

|

|

|

|

|

||

Інв. |

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

№ |

|

|

|

Рис.1.1. Схема лічильника з послідовим переносом на |

|

|

||||||||||||||

інв. |

|

|

|

|

|

|

|

динамічних Т-тригерах |

|

|

|

|

|

|||||||

Взам. |

|

Для побудови |

|

лічильника на додавання використовується інверсія |

||||||||||||||||

дата |

стану |

в |

лічильному |

|

тригері. Якщо як прямий сигнал використовується |

|||||||||||||||

прямий |

вихід |

Т-тригера |

Q, |

то |

динамічний |

вхід |

його |

повинен бути |

з |

|||||||||||

і |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Підпис |

переходом в |

активному |

стані |

від |

1 |

до |

0, і, |

навпаки, при |

прямому |

|||||||||||

динамічному |

вході |

для |

одержання |

функції |

додавання |

необхідно |

||||||||||||||

. |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

№оригін |

використовувати |

інверсний |

вихід |

тригера, |

тільки |

у |

цьому |

випадку |

||||||||||||

|

|

|

|

|

|

|

|

|

|

362.6050102 1 511 ПЗ |

|

Арк. |

||||||||

. |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

Інв |

Зм. Арк. |

№ докум. |

Підпис |

Дaта |

|

|

|

|

3 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

26 |

|

|

|

|

|

|

|

|

|

активними станами будуть нульові стани.

Якщо використовувати однойменні вхідні-вихідні сигнали, то реалізується функція віднімання, епюри напруг якої зображені на рис.1.2.

Uвх |

|

Таким |

чином, |

досить просто |

||

|

реалізувати |

реверсивний |

лічильник, |

|||

Q0 |

|

|||||

|

використовуючи |

змінну |

комутацію |

|||

Q1 |

|

|||||

|

вихідного сигналу |

при |

постійному |

|||

Q2 |

|

|||||

|

значенні динамічного входу. Для |

|||||

|

|

|||||

Рис.1.2. Епюри напруг лічильника цього звичайну |

схему динамічного |

|||||

|

на віднімання |

лічильника |

доповнюють |

елементами |

||

|

|

|||||

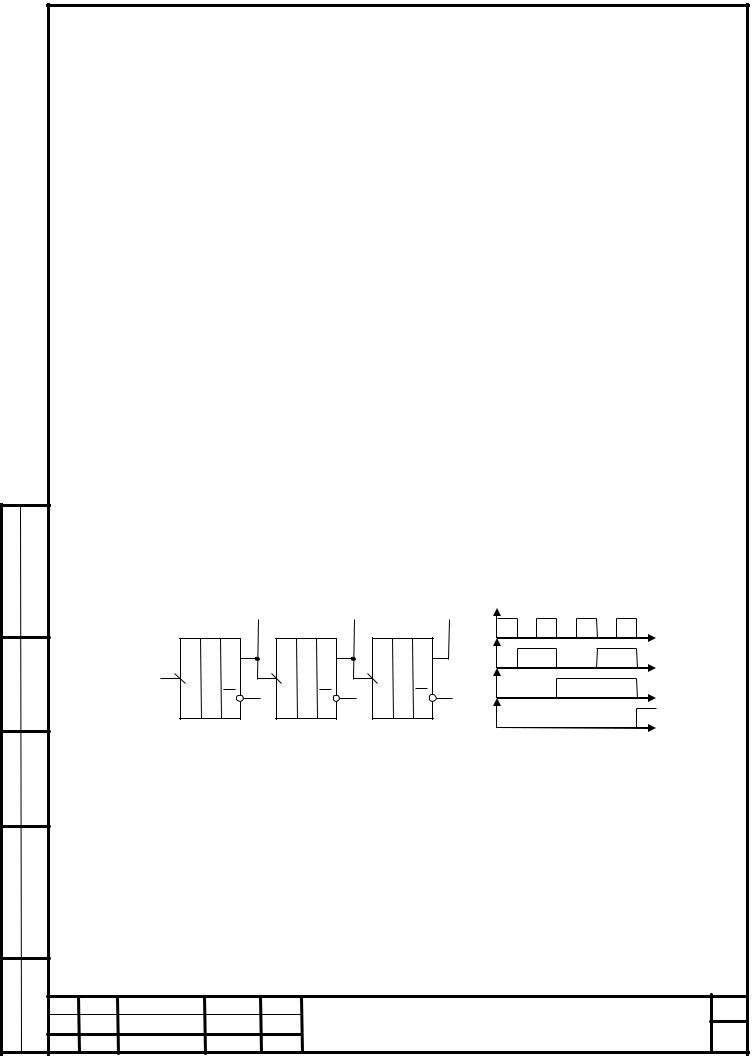

складної логіки 2-2І-АБО. Схема керування доповнюється двома інверторами, які забезпечують перекомутацію сигналів з виходів складних елементів (рис.1.3) [1, 3].

|

|

|

|

Q0 |

|

|

|

Q1 |

|

|

Q2 |

|

|

|

|

Uвх |

Т Q |

|

& |

1 |

Т Q |

& |

1 |

Т |

Q |

|

|

|

|

|

|

|

|

|

|

|

Т |

|

|||

дата |

|

Т |

|

& |

|

Т |

& |

|

|

|

|||

|

|

Q |

|

|

Q |

|

|

Q |

|

||||

і |

|

|

|

|

|

|

|

|

|

|

|||

Підпис |

|

V |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||

. |

|

|

Рис.1.3. Реверсивний лічильник на Т-тригерах |

|

|||||||||

. № дубл |

|

|

|

||||||||||

|

Сигнал V визначає напрямок перерахунку – додавання чи віднімання. |

||||||||||||

Інв |

|

||||||||||||

Вхідні тактові імпульси подаються на вхід Т першого тригера. Якщо V=1, то |

|||||||||||||

інв. № |

|||||||||||||

на перший елемент І комбінаційного пристрою 2-2І-АБО подається значення |

|||||||||||||

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Взам |

логічного нуля, |

на другий |

– |

значення логічної |

одиниці, |

тобто в |

цьому |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

дата |

випадку інформаційним сигналом є сигнал з інверсного виходу Q тригера. |

||||||||||||

При прямому динамічному вході реалізується схема додавання. Якщо V=0, |

|||||||||||||

і |

|

|

|

|

|

|

|

|

|

|

|

|

|

Підпис |

активним стає прямий вихід тригера і маємо реалізацію схеми віднімання. |

||||||||||||

|

При реалізації схеми віднімання, якщо маємо обнулені значення Q за |

||||||||||||

. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

№оригін |

першим тактовим імпульсом, в тригер записується максимальне значення |

||||||||||||

|

|

|

|

|

|

362.6050102 1 511 ПЗ |

Арк. |

||||||

. |

|

|

|

|

|

|

|

||||||

Інв |

Зм. Арк. |

№ докум. |

Підпис |

Дaта |

|

|

4 |

||||||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

27 |

|

|

|

|

|

|

коду (всі одиниці), і з кожним тактовим імпульсом здійснюється віднімання одиниці у двійковому коді. Загальним недоліком є зростання часу комутації результуючого вихідного стану лічильника при зростанні загальної його розрядності. Для усунення цього недоліку використовуються лічильники з паралельним переносом (рис.1.4), тоді схеми послідовних лічильників доповнюють комбінаційними елементами, які враховують в кожному наступному розряді стани всіх попередніх розрядів, що реалізуються функцією кон’юнкції [1].

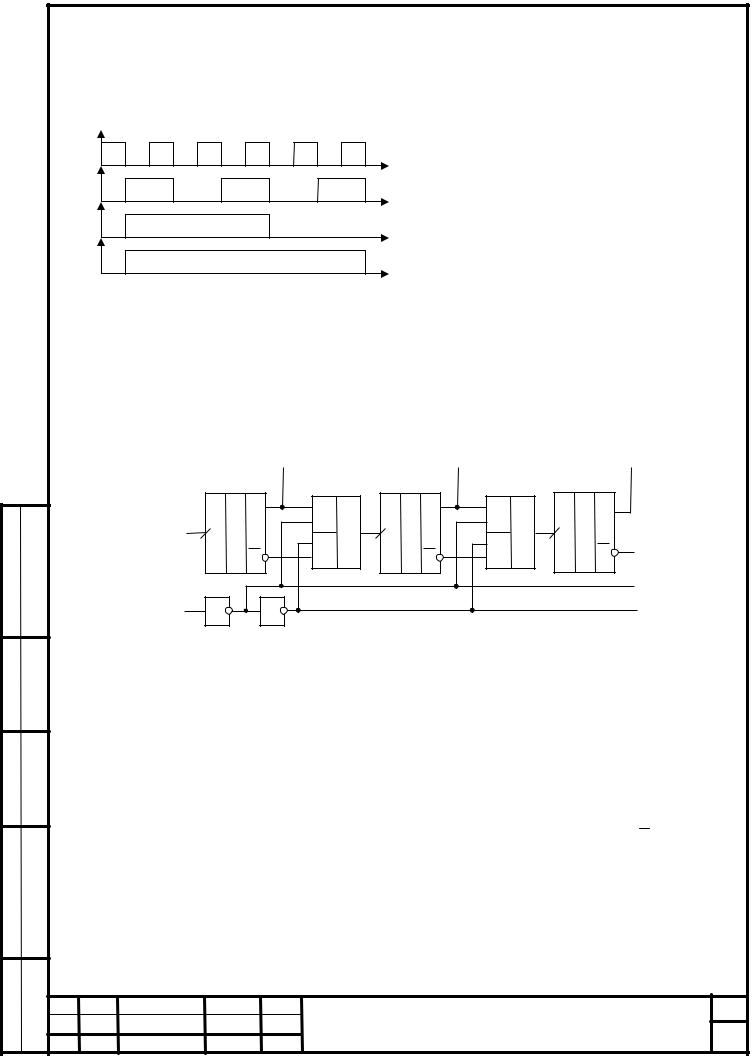

Обов’язковою умовою схем паралельного переносу є використання синхронізуючого входу С. Недоліком є зростання кількості входів у кон’юнкторах зі зростанням розрядності лічильника, оскільки вони повинні забезпечувати реалізацію функції множення за модулем 2.

|

|

|

|

|

Q0 |

|

Q1 |

|

|

|

Q2 |

|

Q3 |

|

|

|

|

|

|

|

|

|

|

& |

|

|

& |

|

|

|

|

і дата |

|

Uвх |

|

Т Q |

Т |

Q |

|

Т |

Т |

Q |

Т |

Q |

|

||

|

Т |

|

|

Т |

|

|

|

|

Т |

|

|

||||

|

C |

C |

Q |

|

C |

Q |

|

C |

Q |

C |

Q |

|

|||

Підпис |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Рис.1.4. Лічильник з паралельним переносом |

|

|

||||||||||

|

|

|

|

|

|

||||||||||

дубл. |

|

Для першого розряду формуючий сигнал залишається асинхронним, |

|||||||||||||

. № |

тому його вважають таким, що дорівнює 1. В лічильнику з паралельним |

||||||||||||||

Інв |

|||||||||||||||

переносом напрямок перерахунку не залежить від вибору типу вхідного |

|||||||||||||||

інв. № |

|||||||||||||||

стану |

(прямого |

чи |

інверсного), |

він визначається |

тільки використаними |

||||||||||

Взам. |

вихідними сигналами Q або |

Q , тому реалізувати реверсивну схему можна |

|||||||||||||

і дата |

аналогічно до схеми послідовного лічильника. |

|

|

|

|||||||||||

|

Для |

усунення |

недоліків |

паралельних схем і підвищення швидкості |

|||||||||||

Підпис |

перерахунку використовуються комбіновані схеми паралельно-послідовного |

||||||||||||||

переносу (рис.1.5), при цьому лічильник розрядності n, меншої за загальну |

|||||||||||||||

. |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

№оригін |

розрядність |

m |

лічильника, |

є |

базовою |

групою, |

в |

якій |

реалізовано |

||||||

|

|

|

|

|

|

|

|

|

362.6050102 1 511 ПЗ |

Арк. |

|||||

. |

|

|

|

|

|

|

|

|

|

|

|||||

Інв |

Зм. Арк. |

№ докум. |

Підпис Дaта |

|

|

5 |

|||||||||

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

28 |

|

|

|

|

|

|

паралельний підрахунок. Передача комутаційних сигналів між групами реалізується послідовно [2].

Q1.1Q1.2 … Q1.n |

|

Q2.1Q2.2 … Q2.n |

|

|

Максимальне значення |

часу |

|||||

|

|

|

перемикання визначається |

часом |

|||||||

|

& |

|

|

|

& |

|

|||||

|

|

|

|||||||||

|

… |

|

|

… |

|

|

комутації тригерів у окремій групі. |

||||

Uвх |

|

|

|

|

При цьому |

потрібно враховувати |

|||||

|

|

||||||||||

Група 1 |

|

|

|

Група 2 |

|

|

|

||||

|

|

|

|

|

|

|

загальний максимальний час, який |

||||

С |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

залежить |

від кількості |

груп |

|

Рис.1.5. Лічильник з груповим переносом |

|||||||||||

|

|

|

|

|

|

|

|

|

багаторозрядного лічильника. |

|

|

У загальному випадку кількість тригерів у кожній групі може бути довільною і навіть дорівнювати 1, тому паралельно-послідовну схему можна реалізувати для окремих розрядів. Така схема називається схемою з наскрізним переносом (рис.1.6) [3].

|

|

|

|

Q0 |

|

Q1 |

& |

|

|

Q2 |

|

Q3 |

||

|

|

|

|

|

|

|

|

|

|

& |

|

& |

||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

і дата |

|

Uвх |

Т |

Q |

|

Т Q |

|

Т |

Т |

Q |

Т |

Q |

|

|

|

Т |

|

Т |

|

|

|

|

Т |

|

|

||||

|

C |

C |

Q |

C |

Q |

|

C |

Q |

C |

Q |

|

|||

Підпис |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Рис.1.6. Схема лічильника з наскрізним переносом |

|

||||||||||

|

|

|

|

|

||||||||||

дубл. |

|

У такій схемі комутація тригерів відбувається практично одночасно, |

||||||||||||

. № |

необхідно враховувати тільки час затримки на комутацію одного окремого |

|||||||||||||

Інв |

||||||||||||||

розряду із врахуванням часу затримки в комбінаційній схемі. Підвищення |

||||||||||||||

інв. № |

||||||||||||||

швидкодії досягається за рахунок того, |

що час перемикання комбінаційної |

|||||||||||||

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Взам |

схеми менший за час комутації тригера. |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

дата |

|

На практиці, з врахуванням схемотехнічних можливостей мікросхем |

||||||||||||

середнього |

ступеня |

інтеграції, |

багаторозрядні |

лічильники |

будуються, |

|||||||||

і |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Підпис |

частіше за все, |

у вигляді групової структури. При цьому кожною групою є, |

||||||||||||

наприклад, |

мікросхема |

чотирирозрядного |

лічильника |

з |

паралельним |

|||||||||

|

||||||||||||||

. |

переносом, а між групами організовують послідовні або паралельні зв’язки. |

|||||||||||||

№оригін |

||||||||||||||

|

|

|

|

|

|

|

362.6050102 1 511 ПЗ |

Арк. |

||||||

. |

|

|

|

|

|

|

|

|

||||||

Інв |

Зм. Арк. |

№ докум. |

Підпис |

Дaта |

|

6 |

||||||||

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

29 |

|

|

|

|

|

|

|