- •Міністерство транспорту та зв'язку України Державний економіко-технологічний університет транспорту Кафедра “Інформаційні системи й технології”

- •Київ-2007

- •1.Завдання Розробити спеціалізовану мікропроцесорну систему у складі *

- •2. Основні функціонально-конструктивні пристрої

- •2.1. Мікропроцесор.

- •2.1.1. Загальні відомості.

- •2.1.2. Призначення виводів мікропроцесора (на прикладі мпс к1810вм86).

- •2.1.3. Структура мікропроцесора

- •2.1.4. Функціонування мікропроцесора

- •2.2Арифметичний співпроцесор.

- •2.2.1. Призначення виводів віс к1810вм87

- •2.2.2. Функціонування арифметичного співпроцесора

- •2.2.3. Спеціальнє використання арифметичного співпроцесора

- •2.3.Спвб:

- •2.3.1. Структура спвб

- •2.3.2Функціонування спвб

- •Поле р визначає пріоритет каналу. •

- •2.3.3. Система команд спвв

- •3. Розрахунок адресного простору пам’яті та портів

- •4. Організація переривань

- •5. Структура однопроцесорної системи

- •7.1. Генератор тактових імпульсів

- •7.2. Буферні регістри й шинні формувачі.

- •7.3. Контролер системної шини

- •7.4. Арбітр шин

- •8.1. Контролер прямого доступу пам'яті.

- •10 Література

- •03049, М. Київ-49, вул. Миколи Лукашевича, 19

2.3.Спвб:

2.3.1. Структура спвб

Внутрішня структура СПВБ підлегла його основному призначенню – виконувати пересилання даних без безпосереднього втручання ЦП, що зв'язується зі СПВБ тільки для ініціалізації й видачі завдання на обробку. В обох випадках ЦП попередньо готовить необхідне повідомлення в пам'яті й потім за Допомогою сигналу запиту готовності каналу активізує СПВБ ВМ89 на виконання дій, певних у повідомленні. Із цього моменту СПВБ працює незалежно від ЦП. У процесі виконання завдання або по його завершенні СПВБ може зв'язатися зі ЦП за Допомогою сигналу запиту переривання.

Процесор може звертатися до пам'яті й пристроїв уведення – виводу (ПВВ), розміщеним у системному просторі адрес ємністю 1 Мбайт або в простір уведення – виводу ємністю 64 Кбайт (мал. 4.2). Хоча СПВБ розташовує тільки одною фізичною шиною даних, зручно думати, що в системний простір він звертається по системній шині (СШ) даних, а в просторі уведення – виводу по шині уведення – виводу (ШВВ) даних. Розходження між цими двома шинами полягає в тому, що СШ управляється сигналами читання й запису на згадку, а ШВВ – сигналами читання (уведення) і запису (виводу) в ПВВ. Таким чином, пристрою уведення – виводу, розміщені в системному просторі, виявляються відображеними на пам'ять (реагують на 20-бітові адреси, закріплені за ними по командах читання й запису на згадку).

Структура процесора уведення – виводу (мал. 4.4) включає кілька функціональних вузлів, з'єднаних 20-бітовою внутрішньою шиною для одержання максимальної швидкості внутрішніх пересилань. (На відміну від 16-бітової зовнішньої шини по внутрішній шині здійснюються пересилання як 16-, так і 20-бітових значень адрес і даних.)

Загальний пристрій керування (КП) координує роботу функціональних вузлів процесора. Всі операції (виконання команд, цикли пересилання із ПДП, відповіді на запит готовності каналу й ін.), виконувані СПВБ, розпадаються на послідовності елементарних дій, які називаються внутрішніми циклами. Цикл шини, наприклад, становить один внутрішній цикл; виконання команди може зажадати декількох внутрішніх циклів. Усього налічується 23 різних типу внутрішніх циклів, кожний з яких займає від двох К восьми тактів CLK (без обліку можливих станів очікування й часу на арбітраж шин). Загальне КП вказує для кожної операції, який функціональний вузол буде виконувати черговий внутрішній цикл. Наприклад, коли обидва канали активні, загальне КП визначає, який канал має більше високий пріоритет, або, якщо їхні пріоритети рівні, здійснює керування змінно роботою каналів. Крім того, загальне КП здійснює початкову ініціалізацію процесора, для чого використовується програмно недоступний регістр РСР – покажчик блоку параметрів.

Арифметично-Логічний пристрій (АЛП) може виконувати без знакові арифметичні операції над 8- і 16-бітовими двійковими числами, що включають Додавання, інкремент і декремент. Результатом арифметичних операцій може бути 20-бітове число. Логічні операції, включаючи І, АБО, НІ, можуть виконуватися над 8- і 16-бітовими операндами.

Регістри складання – розбирання беруть участь при передачі всіх даних, що надходять у процесор. Коли розрядність джерела й приймача даних різняться, процесор використовує ці регістри для забезпечення максимальної швидкості передачі. Наприклад, при пересиланні із ПДП із 8-бітового ПВВ в 16-бітову пам'ять процесор затрачає два цикли шини на прийом двох послідовних байтів, «збирає» їх в одне 16-бітове слово й передає його на згадку за один цикл шини. При передачі 16-бітових даних 8-бітовому приймачу здійснюється його попередня «розбирання» на байти. Таким чином, наявність регістрів складання/розбирання заощаджує цикли шини.

Черга команд використовується для підвищення продуктивності процесора при вибірці їх з пам'яті. Під час виконання програми каналом команди вибираються з пам'яті словами, розміщеними по парній адресі молодшого байта. На одну таку вибірку затрачається один цикл шини. Цей процес показаний на мал. 4.5. Якщо останній байт поточної команди X доводиться на парну адресу, те наступний за ним байт із непарної адреси (він є першим байтом команди Y) витягнутого слова зберігається в черзі. Коли канал починає виконувати команду Y, цей байт із черги витягає значно швидше, ніж з пам'яті. Таким чином, черга команд розмірністю всього один байт дозволяє процесору при вибірці команд завжди читати слова, що знижує завантаження шини, збільшуючи її пропускну здатність і продуктивність СПВБ.

У двох виняткових випадках при добуванні команд процесор читає з пам'яті байти, а не слова. По-перше, коли команда передачі керування (наприклад, JMP, JNZ, CALL) указує на непарну адресу, по якому розміщена команда, що вимагає виконання. У цьому випадку перший байт команди витягає окремо. По-друге, коли зустрічається 6-байтовая команда LPDI, що витягає в наступному порядку: байт – слово – байт – байт – байт, і черга не використовується. Коли використовується 8-бітова шина для передачі команд процесору, читаються тільки байти, а черга не використовується й кожна вибірка вимагає одного циклу шини.

Блок шинного інтерфейсу (БШІ) здійснює керування й визначає цикли шини, пов'язані з вибіркою команд і передачею даних між СПВБ і пам'яттю або ПВВ. Кожне звертання до шини пов'язане з битому регістра етикеток (регістр TAG перебуває в кожному каналі), що вказує, до якого простору адрес (системному або уведення – виводу) ставиться обіг. БШІ виставляє тип циклу шини (вибірка команди із простору адрес уведення – виводу, запис даних на згадку системного простору й т.д.) у вигляді коду стану на виходах S2-S0 (табл. 4.2). Системний контролер декодує цей код, вибираючи потрібну шину (СШ/ШВВ) і формуючи відповідну команду (читання, запис і т.д.). Потім БШІ визначає співвідношення між логічною й фізичною шириною СШ і ШВВ. Фізична ширина кожної шини фіксована в системі й повідомляється процесору при його ініціалізації.

У місцевій конфігурації обидві шини (СШ і ШВВ) повинні мати однакову ширину: 8 або 16 біт, що визначається типом ЦП. У вилученій конфігурації СШ процесора уведення – виводу повинна мати ту ж фізичну ширину, що й СШ центрального процесора системи. Ширина ШВВ процесора уведення – виводу може бути обрана незалежно. Якщо в просторі уведення – виводу використовуються які-небудь 16-бітові ПВВ, повинна використовуватися 16-бітова ШВВ. Якщо в просторі уведення – виводу всі ПВВ 8-бітові, то може бути обрана 8- або 16-бітова ШВВ. Перевагу має 16-бітова ШВВ, оскільки вона дозволяє підключати до системи додаткові 16-бітові ПВВ, а також забезпечує більше ефективну вибірку команд програми, розміщеної в просторі уведення – виводу.

Таблиця 4. 2

|

Код стану S2S1SD |

Тип циклу шини |

|

000 |

Вибір команди з простору вводу – виводу |

|

001 |

Зчитування даних з простору вводу-виводу |

|

010 |

Запис даних у простір вводу-виводу |

|

011 |

Не використовується |

|

100 |

Вибір команди з системного простору |

|

101 |

Зчитування даних з системного простору |

|

110 |

Запис даних у системний простір |

|

111 |

Пасивний стан |

Для Пдп-Пересилання в програмі каналу задається логічна ширина СШ і ШВВ незалежно для кожного каналу. Логічна ширина 8-бітової фізичної шини може бути тільки 8-бітової, а для 16-бітової фізичної шини логічна ширина може бути задана 8- або 16-бітової. Це дозволяє обслуговувати 8- і 16-бітові ПВВ за Допомогою однієї 16-бітової фізичної шини. У табл. 4.3 перераховані всі можливі співвідношення між логічною й фізичною шириною СШ і ШВВ у місцевій і вилученій конфігурації.

Таблиця 4. 3

|

Конфігурація |

Ширина СШ фізична : логічна |

Ширина ШВВ фізична : логічна |

|

Місцева |

8:8 16:(8/16) |

8:8 16:(8/16) |

|

Віддалена |

8:8 16:(8/16) 8:8 16:(8/16) |

8:8 16:(8/16) 16:(8/16) 8:8 |

Логічна ширина шини враховується тільки при Пдп-Пересиланнях. добування команд, а також запис і читання операндів здійснюються словами або байтами тільки залежно від фізичної ширини шини.

Поряд з керуванням пересиланнями команд і даних блок шинного інтерфейсу здійснює арбітраж локальних шин. У місцевій конфігурації БШІ використовує лінію RQ/GT для запиту шини в ЦП і її повернення після використання, у вилученій конфігурації – для координації спільного використання локальної ШВВ із іншими процесорами або локальним ЦП, якщо вони є. У тих випадках, коли необхідно монополізувати СШ, блок шинного інтерфейсу формує нульовий активний сигнал LOCK. Це буває у двох випадках: 1) коли канал виконує команду TSL (Test and Set Lock – перевірка з монополізацією); 2) коли в програмі каналу їсти вказівку активізувати LOCK на час Пдп-Пересилання.

Структура каналів процесора уведення – виводу. Процесор ВМ87 (див. мал. 4.4) включає два ідентичних канали. Кожний канал може здійснювати Пдп-Пересилання, виконувати програму, відповідати на запити готовності або простоювати. Ці дії канали можуть виконувати незалежно друг від друга, що дозволяє розглядати СПВБ ВМ89 як два пристрої: канал 1 і канал 2. Кожний канал складається із двох основних частин: пристрою керування уведенням – виводом і групи регістрів, частина яких використовується в програмах, а частина з них є програмно-недоступними.

Пристрій керування уведенням – виводом управляє діями каналу під час Пдп-Пересилання. При виконанні синхронного пересилання воно очікує надходження сигналу синхронізації на вході DRQ, перш ніж виконати черговий цикл читання – запису. Коли Пдп-Пересилання повинна закінчуватися по зовнішньому сигналі, пристрій стежить за його появою на вході ЕХТ. Між циклами читання й запису (поки дані перебувають у СПВБ) канал може робити підрахунок числа переданих даних, перекодувати їх і зрівняти із заданим кодом. Ґрунтуючись на результатах цих дій, КП уведенням – виводом може припинити Пдп-Пересилання.

У процесі виконання програми по команді SINTR пристрій генерує запит переривання в ЦП. Часто запит використовується для того, щоб повідомити ЦП про завершення програми каналу.

Регістри каналу використовуються СПВБ як при Пдп-Пересиланнях, так і при виконанні програми. Всі регістри каналу (мал. 4.6.), за винятком TAG, безпосередньо беруть участь у зазначених процесах. Використання кожного регістра описане в табл. 4.4.

Регістр загального призначення GA служить у більшості команд у якості операнда. У якості базового він використовується для вказівки адреси операнда, що перебуває в пам'яті. Перед початком Пдп-Пересилань програма каналу завантажує в GA адреса джерела або приймача даних.

Регістр загального призначення GB функціонально взаємозамінний з регістром GA. Якщо GA завантажений адресою джерела Пдп-Пересилання, то GB повинен бути завантажений адресою приймача, і навпаки.

Регістр загального призначення GC використовується програмою каналу як операнд або базовий регістр. Використовується при виконанні Пдп-Пересилань, коли здійснюється перекодування даних. У цьому випадку, перед початком пересилання, програма каналу завантажує в GC початкова адреса таблиці перекодування. У процесі пересилання його вміст не змінюється.

Покажчик команд ТР завантажується початковою адресою програми в процесі ініціалізації каналу загальним КП на виконання завдання. Під час виконання програми (завдання від ЦП) ТР відіграє роль лічильника команд. Тому що ВМ89 не містить покажчика стека й не може виконувати стекових операцій, повернення з підпрограми здійснюється шляхом завантаження в ТР адреси повернення, що запам'ятовується в пам'яті по команді CALL. Покажчик завдання є повністю програмно-доступним (на відміну від регістра IP у ВМ86) і може використовуватися програмою як регістр загального значення або базовий. Однак робити це не рекомендується, тому що програма стає важкої для розуміння.

Таблиця 4. 4

|

Регістр |

Використання | |

|

у програмі |

при ПЛП-пересиланні | |

|

GA |

Загального призначення або базовий |

Вказівник джерела чи приймача |

|

GB |

Те ж саме |

Вказівник приймача чи джерела |

|

GC |

>> |

Вказівник таблиці перекодування |

|

ТР |

Вказівник команд |

Вказівник причини закінчення |

|

PF |

Базовий |

Не використовується |

|

IX |

Загального призначення або індексний |

Те ж сааме |

|

ВС |

Загального призначення |

Лічильник байтів |

|

МС |

Загального призначення або маскуючого порівняння |

Приймає участь у маскую чому порівнянні |

|

СС |

Обмеженого використання |

Визначає умови пересилання |

Покажчик блоку параметрів РР завантажується загальним КП початковою адресою блоку параметрів у процесі ініціалізації каналу на виконання завдання. У підготовленому повідомленні розташування блоку параметрів у пам'яті визначає центральний процесор (див. табл. 4.4). Програма каналу не може змінити вміст регістра PP. Його зручно використовувати як базовий для пересилання даних у блок параметрів. Для Пдп-Пересилань регістр РР не використовується.

Індексний регістр IX використовується програмою каналу як регістр загального призначення. Він може також використовуватися як індексний регістр для адресації операндів, що перебувають у пам'яті. Як різновид індексної адресації, за Допомогою IX можна задати індексну адресацію з автоінкрементом, що дуже зручна при обробці масивів даних. Для Пдп-Пересилань регістр IX не використовується.

Лічильник байтів ВР у програмі каналу служить регістром загального призначення. При Пдп-Пересиланню підраховує число пересланих байтів шляхом декрементування значення, завантаженого перед її початком. Якщо пересилання повинна закінчуватися по заданому числу пересланих байтів, то КП уведенням – виводом закінчить її, коли вміст ВР стане рівним нулю.

Регістр маскованого порівняння МС у програмі каналу може використовуватися як регістр загального призначення або для маскованого порівняння. При Пдп-Пересиланню використовується для маскованого порівняння. Масковане порівняння дозволяє зрівняти виділені розряди байта (операнда команди або байта, що пересилається,) із заданим заздалегідь значенням. Для цього в старший байт МС завантажується маска, що виділяє розряди, що цікавлять, а в молодший – порівнюване значення (мал. 4.7). У програмі, при виконанні команди умовного переходу по маскованому порівнянню (або при Пдп-Пересиланню), певний у ній операнд рівняється із замаскованим значенням.

Регістр керування каналом СС використовується в основному при Пдп-Перисилках. Він служить для визначення умов пересилання й указує спосіб її закінчення. Структура й позначення керуючих полів СС представлені на мал. 4.8. П'ять старших полів визначають умову Пдп-Пересилання:

F (пересилання) визначає, звідки й куди пересилаються дані;

TR (перекодування) – чи треба пересилаються данні, що, перекодувати;

SYN(синхронізація) – спосіб синхронізації пересилання; S (джерело) – у якому регістрі (GA або GB) перебуває адреса джерела; L (монополізація) – чи варто активізувати сигнал під час пересилання.

Чотири молодші поля задають спосіб закінчення пересилання:

TS указує, що пересилання складається в передачі тільки одного даного;

ТХ – що пересилання повинна закінчуватися по зовнішньому сигналі (ЕХТ);

ТВС – по нулі в лічильнику байтів (ВР);

ТМС – за результатами маскованого порівняння.

Поле З не використовується для Пдп-Пересилань, а служить зручним засобом керування пріоритетом програми каналу.

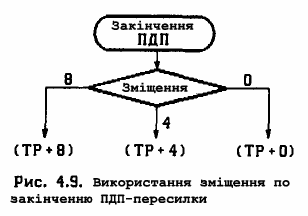

Кодування всіх керуючих полів регістра СС наведене в табл. 4.5. Кодування полів ТХ, ТВС і ТМС дозволяє вибрати зсув 0, 4 або 8 по закінченню Пдп-Пересилання. Обране значення додається до вмісту лічильника команд ТР і визначає три різних крапки програми, у які передається керування після закінчення пересилання (мал. 4.9). Закінчення по одиночному пересиланню TS = 1 завжди приводить до нульового зсуву.

У регістрі TAG кожний біт відповідає одному із чотирьох регістрів: GA, GB, GC і ТР (див. мал. 4.6). Коли вони використовуються в якості базових чи вказівнику (см. табл. 4.5), то біт TAG визначає, до якого простору адресів (системного чи уведення – виведення) відносять адрес, розміщений в відповідному регістрі. Значення біта TAG = 0 показує, що адрес відноситься

до системного простору (20-бітовий адрес); TAG=1 показує на простір уведення – виведення (16-бітовий адрес). Загальне КП встановлюється чи

Таблиця 4.5

|

Керуюче поле |

Код поля |

Умова ПДП-пересилання |

|

F (функція пересилання) |

00 |

З порту вводу у порт виводу |

|

01 |

З пам’яті у порт виводу | |

|

10 |

З порту вводу у пам’ять | |

|

11 |

З пам’яті у пам’ять | |

|

TR (перекодування) |

0 |

Немає перекодування |

|

1 |

Є перекодування | |

|

SYN (синхронізація) |

00 |

Пересилання асинхронне |

|

01 |

Синхронізація від джерела | |

|

10 |

Синхронізація від приймача | |

|

11 |

Зарезервований код | |

|

S (джерело) |

0 |

Адреса джерела у регістрі GA |

|

1 |

Адреса джерела у регістрі GB | |

|

L (монополізація) |

0 |

Сигнал LOCK не активний |

|

1 |

Сигнал LOCK активний | |

|

С (пріоритет програми) |

0 |

Звичайний пріоритет програми |

|

1 |

Підвищений пріоритет програми | |

|

TS (одиночне пересилання) |

0 |

Пересилання не одиночне |

|

1 |

Пересилання одного даного | |

|

ТХ (Закінчення за зовнішнім сигналом) |

00 |

Не зовнішнє закінчення |

|

01 |

По сигналу ЕХТ зі зміщенням 0 | |

|

10 |

По сигналу ЕХТ зі зміщенням 4 | |

|

11 |

По сигналу ЕХТ зі зміщенням 8 | |

|

ТБС (Закінчення по нулю в лічильнику) |

00 |

Закінчення не по нулю в лічильнику |

|

01 |

Закінчення по (ВС)=0 зі зміщенням 0 | |

|

10 |

Закінчення по (ВС)=0 зі зміщенням 4 | |

|

11 |

Закінчення по (ВС)=0 зі зміщенням 8 | |

|

ТМС (закінчення по результатам маскуючого порівняння) |

000 |

Не по результатам маскуючого порівняння |

|

001 |

За збігом зі зміщенням 0 | |

|

010 |

За збігом зі зміщенням 4 | |

|

011 |

За збігом зі зміщенням 8 | |

|

100 |

Не за результатам маскуючого порівняння | |

|

101 |

За неспівпадінням зі зміщенням 0 | |

|

110 |

За неспівпадінням зі зміщенням 4 | |

|

111 |

За неспівпадінням зі зміщенням 8 |

скидає біт регістру TAG, відповідний ТР, в залежності від того, в якому адресному просторі розміщена програма каналу.

Коли GA, GB і GC використовуються як регістри загального призначення, що відповідає біт регістра TAG установлюється по-різному при виконанні різних груп команд (див. табл. 4.5).

Восьмибітовий регістр PSW, наявний у кожному каналі, зберігає слово-стан програми. У регістр PSW заноситься інформація про поточний стан каналу (мал. 4.10). Логічна ширина шини приймача дорівнює 8 біт при D = 0 і 16 біт при D = 1. Логічна ширина шини джерела дорівнює 8 біт при 5 = 0 і 16 біт при 5 = 1. Коли канал виконує програму, біт ТВ установлюється в одиницю. При керуванні видачею запиту переривання 1C установлюється в нуль, коли переривання заборонене, і в одиницю, коли воно дозволено. Якщо канал видав запит переривання, то 15 = 1, якщо не видав – 15 = = 0. Біт В = 1 задає режим граничного завантаження шини. Біт XF=1, коли канал виконує Пдп-Пересилання. Біт Р задає пріоритет каналу. Ця інформація дозволяє в будь-який момент призупинити роботу каналу, записавши значення PSW і ТР на згадку, а потім відновити його роботу, зчитавши PSW і ТР.