- •Міністерство транспорту та зв'язку України Державний економіко-технологічний університет транспорту Кафедра “Інформаційні системи й технології”

- •Київ-2007

- •1.Завдання Розробити спеціалізовану мікропроцесорну систему у складі *

- •2. Основні функціонально-конструктивні пристрої

- •2.1. Мікропроцесор.

- •2.1.1. Загальні відомості.

- •2.1.2. Призначення виводів мікропроцесора (на прикладі мпс к1810вм86).

- •2.1.3. Структура мікропроцесора

- •2.1.4. Функціонування мікропроцесора

- •2.2Арифметичний співпроцесор.

- •2.2.1. Призначення виводів віс к1810вм87

- •2.2.2. Функціонування арифметичного співпроцесора

- •2.2.3. Спеціальнє використання арифметичного співпроцесора

- •2.3.Спвб:

- •2.3.1. Структура спвб

- •2.3.2Функціонування спвб

- •Поле р визначає пріоритет каналу. •

- •2.3.3. Система команд спвв

- •3. Розрахунок адресного простору пам’яті та портів

- •4. Організація переривань

- •5. Структура однопроцесорної системи

- •7.1. Генератор тактових імпульсів

- •7.2. Буферні регістри й шинні формувачі.

- •7.3. Контролер системної шини

- •7.4. Арбітр шин

- •8.1. Контролер прямого доступу пам'яті.

- •10 Література

- •03049, М. Київ-49, вул. Миколи Лукашевича, 19

7.4. Арбітр шин

Арбітр шин використовується в багатопроцесорних системах як пристрій, що здійснює синхронізацію доступу безлічі МП до системної шини.

Структурна схема арбітра шин (АШ) наведена на мал. 5.18. Дешифратор станів залежно від коду стану МП запускає схему пріоритетного арбітражу, інтерфейси Multibus і місцевої шини на виконання дій по захоплення або звільненню системної шини. Схема пріоритетного арбітражу робить арбітраж мікропроцесорів, що запитують керування системною шиною, і по тактовому сигналі МП, що займає шину, здійснює дії по її звільненню. Інтерфейс Multibus здійснює процедуру взаємодії арбітрів шини багатопроцесорної системи й синхронізує дії по захоплення системної шини. Інтерфейс місцевої шини формує сигнал дозволу доступу до системної шини для шинного інтерфейсу МП. Пристрій управління здійснює синхронізацію й керування режимами роботи арбітра шин з боку МП.

Призначення виводів (мал. 5.19).

S2 – S0 – входи сигналів стану мікропроцесора. Арбітр шин фіксує ці сигнали й починає дії по захоплення, утриманню або звільненню системної шини.

CLK – вхідні сигнали від генератора тактових імпульсів синхронізує дію арбітра шин з діями мікропроцесора.

LOCK – сигнал заборони звільнення системної шини. Мікропроцесор виробляє цей сигнал, забороняючи арбітрові звільняти системну шину для будь-якого іншого арбітра, що запитує керування шиною, незалежно від його пріоритету.

CRQLCK – сигнал заборони звільнення системної шини при її запиті по входу CBRQ.

ANYRQST – вхід дозволу звільнення системної шини при будь-якому запиті. Активний сигнал ANYRQST = 1 дозволяє арбітрові звільнити системну шину при запиті керування шиною арбітром з більше низьким пріоритетом. Запитуючий арбітр здійснює захоплення шини в цьому випадку так, ніби він був арбітром з більше високим пріоритетом. Активний сигнал на вході ANYRQST у сполученні з активним сигналом на вході CBRQ = 0 змушує арбітр звільняти системну шину після кожного циклу передачі.

RESB – вхід вибору режиму роботи зі якою-небудь шиною. Забезпечує роботу арбітра шин у багатопроцесорних системах, що мають як системну, так і якою-небудь шину. При вхідному сигналі RESB=1 системна шина запитується або звільняється як функція вхідного сигналу SYSB/RESB. При RESB = 0 вхідний сигнал SYSB/RESB не впливає на роботу арбітра.

SYSB/RESB – вхід дозволу доступу до системної шини для арбітра, установленого в режим роботи із системною й якою-небудь шиною. Сигнал SYSB/RESB звичайно формується додатковим дешифратором, підключеним до шини адреси. Зміна значення сигналу SYSB/RESB дозволена в період часу від четвертого такту поточного циклу до початку другого такта наступного циклу МП. У період від другого такту до початку четвертого такту циклу МП зміна сигналу SYSB/RESB приводить до невизначеності по захоплення й звільненню системної шини. При SYSB/RESB – I арбітр запитує системну шину, при SYSB/RESB = 0 він звільняє системну шину іншому арбітрові, що запитує керування нею.

IOB – вхід вибору режиму роботи з периферійною шиною уведення – виводу. Забезпечує роботу арбітра шини в багатопроцесорних системах, що мають як системну шину, так і периферійну шину уведення – виводу.

При IOB = 0 арбітр запитує й звільняє системну шину залежно від значення сигналу S2: при виконанні мікропроцесором команд уведення – виводу (52 = 0) арбітр звільняє системну шину, а при виконанні команд звертання до пам'яті (S2=l) він захоплює керування системною шиною.

AEN – вихід дозволу доступу до системної шини. Сигнал AEN = 0 переводить фіксатори адреси, шинні формувачі й тактовий генератор МП в активний стан і дозволяє йому управляти системною шиною. Сигнал AEN = 1 знімає сигнал готовності із входу МП і переводить виходи фіксаторів адреси й шинних формувачів у високоомний стан.

IN IT – початкова установка. Використовується для початкової установки всіх шинних арбітрів, пов'язаних із системною шиною. Після початкової установки ніякий арбітр не має доступу до керування системною шиною. Тривалість імпульсу INIT повинна бути не менш суми трьох періодів CLK. і трьох періодів BCLK.

BCLK – вхід синхронізації системної шини. На нього подаються тактові імпульси від шинного тактового генератора, що здійснює синхронізацію дій всіх арбітрів шин по захоплення системної шини. У якості шинного тактового генератора може служити генератор тактових імпульсів одного із МП багатопроцесорної системи.

BREQ – сигнал запиту шини. Використовується в схемах паралельного й циклічного дозволу пріоритету для запиту керування системною шиною.

BPRN – вхід пріоритетного дозволу доступу до шини. Сигнал BPRN = 0 указує арбітрові шини, що в системі немає іншого арбітра з більше високим пріоритетом, що запитував би керування шиною. Сигнал BPRN = 1 указує арбітрові на те, що він втратив пріоритет стосовно іншого арбітра. Надалі появу сигналу BPRN = 0 дозволяє арбітрові знову захопити системну шину при переході сигналу BCLK, від високого рівня до низького.

BPRO – вихід пріоритетного дозволу доступу до шини використовується в системах зі схемою послідовного арбітражу, у яких вихід BPRO з'єднаний із входом BPRN арбітра з більше низьким пріоритетом. Сигнал BPRO -Про видається арбітром, що одержав сигнал BPRN = 0, але не запитуюче керування шиною, і подається на вхід BPRN наступного арбітра з більше низьким пріоритетом.

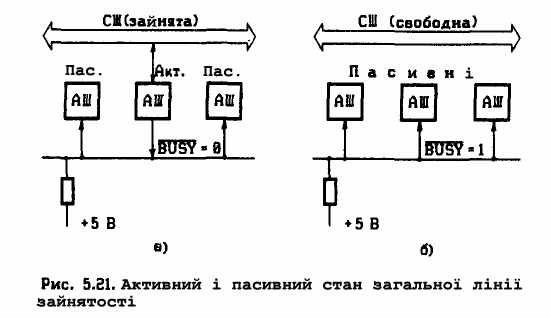

BUSY— вхід/вихід зайнятості шини. Сигнал BUSY = 0 видається арбітром, що одержав керування системною шиною, і служить для вказівки іншим арбітрам, що системна шина зайнята. Виводи всіх шинних арбітрів системи мають вихід з відкритим колектором і об'єднані по лінії BUSY. Коли який-небудь арбітр захоплює керування шиною, він видає сигнал BLJSY = 0 і забороняє доступ до керування шиною іншим арбітрам системи. По закінченні роботи із шиною арбітр видає сигнал BLJSY=1, дозволяючи тим самим іншим арбітрам захопити шину.

CBRQ – вхід/вихід загального запиту шини. У якості вхідного сигнал CBRQ = 0 повідомляє арбітра шин про те, що в системі є інші арбітри з більше низьким пріоритетом, що запитують керування системної шиною. Сигнал CBRQ= 1 повідомляє, що таких арбітрів немає й, отже, арбітр може продовжувати керування, що виключає процедуру захоплення шини. У якості вихідний сигнал CBRQ = 0 видається арбітром, що у цей момент не управляє шиною, але хоче одержати доступ до керування.

Виводи CBRQ всіх арбітрів системи, аналогічно виводам BUSY, мають вихід з відкритим колектором і об'єднані по лінії CBRQ.

Функціонування. У багатопроцесорних системах, що містять як системну, так і якою-небудь шину, кожний МП може підключитися до однієї або більше шинам. У той же час два або більше МП можуть підключатися до однієї шини. У першому випадку потрібно визначити, до якої шини повинен бути підключений МП, у другому – який МП має більший пріоритет і, отже, якому МП повинен бути забезпечений доступ до шини. Рішення подібних питань здійснюється арбітрами шин.

На мал. 5.20 зображені два МП (ведучі й ведений), підключені до локальної шини. Наявність зв'язку мікропроцесорів по лінії RQ/GT забезпечує вихід на ЛШ тільки один МП (виходи іншого переходять у високоомний стан). Схема шинного інтерфейсу (СШІ) підключає локальну шину до зовнішнього, причому одна ЛШ може підключатися до будь-якого числа зовнішніх і для кожного такого підключення потрібно своя СШІ. На мал. 5.20 показані дві СШІ: одна підключає ЛШ до якої-небудь шини, використовуваною тільки даною парою МП, інша – до системної шини, використовуваної іншими МП багатопроцесорної системи. СШІ складається з фіксаторів адреси, шинних формувачів і системного контролера. Арбітр шин використовує входи S2 – S0 для визначення того, що МП потрібна системна шина й він дозволяє доступ до неї, якщо цьому не перешкоджає схема пріоритетного арбітражу, тобто якщо в системі немає інших МП із більше високим пріоритетом, що використовують СШ. Коли АШ, видаючи сигнал AEN = 0, дозволяє доступ своєму мікропроцесору до СШ, він стає активним. Якщо СШІ системної шини відключена, то АШ пасивний, і в цей час мікропроцесор не має доступу до СШ і може використовувати тільки РШ.

З пасивного стану в активне АШ переходить щораз, коли того зажадає МП (кодом стану S0S1S2), і СШ виявляється вільна, тобто немає запиту на неї від іншого АШ, що обслуговує МП із більше високим пріоритетом. Ця ж схема пріоритетного арбітражу змушує АШ звільнити СШ при надходженні запиту з більше високим пріоритетом. У загальному випадку можна вважати, що АШ здійснює зв'язок СШ із одним провідної і його веденим (якщо він є) МП. При цьому МП «не знає» про існування АШ і виконувана їм програма «не піклується» про доступ до шин. АШ стає активним і починає керування СШ, як тільки почнеться цикл обігу МП до шини, що вимагає доступу. У цей цикл вводяться такти очікування, щоб надати арбітрові необхідний час для захоплення шини. Після цього АШ дозволяє доступ до СШ своєму МП, поки для цього існують умови. Таким чином, МП виконує один довгий цикл звертання до шини із внесенням тактів очікування TW щораз при захоплення СШ арбітром і звичайні цикли, поки АШ утримує системну шину.

Арбітр шин уважає СШ зайнятий або вільної залежно від значення сигналу BUSY. Виводи BUSY всіх АШ багатопроцесорної системи поєднуються в загальну лінію зайнятості (мал. 5.21). Сигнал BUSY = 0 виставляється на виході активного АШ і на входах всіх інших арбітрів, що перебувають у пасивному стані (мал. 5.21, а). Це означає, що системна шина зайнята. Якщо жодному МП системи не потрібен доступ до СШ, то всі арбітри стають пасивними й загальний сигнал BUSY=1 означає, що СШ вільно (мал. 5.21,6). Вільний або пасивний АШ може аналізувати вхідний сигнал BUSY для визначення зайнятості системної шини.

Захопивши керування шиною, АШ зберігає його до настання умов звільнення. Звичайна умова звільнення наступає, коли МП виконує команду HALT або NOP (S2S1 S0 дорівнює 011 або 111) або коли BPRN = 1, що вказує на наявність запиту з більше високим пріоритетом. Однак якщо АШ одержує вхідний сигнал LOCK = 0, то він зберігає керування шиною на увесь час дії цього сигналу, що блокує всі умови звільнення шини. Продовжуючи втримувати вихідний сигнал BUSY = 0, АШ змушує схему пріоритетного арбітражу не реагувати на запити від інших АШ із більше високим пріоритетом. Сигнал CRQLCR діє подібно сигналу LOCK, але його дія обмежена тільки сигналом запиту шини CBRQ. Якщо АШ спробує звільнити шину по запиті CBRQ = 0, то активний сигнал CRQLCR =0 перешкодить цьому. Сигнал ANYRQST змушує арбітр звільнити шину з появою будь-якої умови звільнення. Повні відомості про умови звільнення й утримання СШ зведені в табл. 5.2.

|

Таблиця 5.2 | |||||||

|

Вхідний сигнал |

Реакція арбітру шин | ||||||

|

LOCK |

BPRN |

CRQLCK |

CBRQ |

ANYRQST | |||

|

0 |

X |

X |

X |

X |

Утримання шини | ||

|

1 |

0 |

0 |

0 |

X |

Теж саме | ||

|

1 |

0 |

0 |

1 |

X |

>> | ||

|

1 |

0 |

1 |

0 |

0 |

Умовне звільнення шини1) | ||

|

1 |

0 |

1 |

0 |

1 |

Безумовне звільнення шини | ||

|

1 |

0 |

1 |

1 |

X |

Утримання шини | ||

|

1 |

1 |

X |

X |

X |

Безумовне звільнення шини | ||

|

1)АШ звільняє шину тільки в тому випадку, коли його МП знаходиться в стані S2S1S0=001 або 111 | |||||||

Залежно від конфігурації багатопроцесорної системи може бути задано чотири різних режими роботи АШ. Для завдання режимів роботи арбітра служать два входи: IOB і RESB. Сигнал на вході SYSB/RESB відіграє допоміжну роль і служить для визначення умов доступу до СШ.

Режим роботи із системною шиною задається установкою сигналів IOB = 1 і RESB = 0 (вхід SYSB/RESB ігнорується). Ця комбінація сигналів відповідає підключенню МП тільки до однієї системної шини, як показано на мал. 5.22. Як тільки МП буде потрібно виконати цикл звертання до СШ, він виставляє відповідний код стану на входах S2 – S0 арбітра. Якщо зовнішня схема пріоритетного арбітражу дозволяє арбітрові захоплення СШ (BPRN = 0), він, одержавши доступ, буде його втримувати до виникнення умов звільнення. Поки АШ має доступ до СШ, він формує сигнал AEN = 0, дозволяючи МП використовувати СШ. Оскільки часто в подібних конфігураціях окремі МП синхронізуються від своїх генераторів тактових імпульсів, загальна синхронізація роботи СШ здійснюється окремим тактовим генератором шини. Виходячи із цього перехід сигналу AEN в активний стан (1-*-і^0) синхронізується імпульсами BCLK, а зворотний перехід (0->1) – імпульсами CLK, (мал. 5.23).

Режим роботи із системною шиною пам'яті й якою-небудь шиною уведення – виводу задається установкою сигналів IOB = RESB = 0 і SYSB/RESB = 0.

Ця комбінація сигналів відповідає підключенню МП до системної шини, до якої підключена тільки пам'ять, і до шини, що обслуговує тільки пристрою уведення – виводу (мал. 5.24). У цьому режимі сигнал AEN = 0 виробляється арбітром тільки в тих випадках, коли мікропроцесору потрібно здійснити доступ до пам'яті (при наявності сигналу дозволу від зовнішньої схеми пріоритетного арбітражу BPRN=0). Доступ до якої-небудь шини

уведення – виводу наданий мікропроцесору завжди при виконанні команд уведення – виводу (IN і OUT) сигналом PDEN = 0. Схема шинного інтерфейсу, що забезпечує зв'язок ЛШ із РШ уведення – виводу, у цьому випадку звичайно не містить системного контролера. Його функції виконує системний контролер СШІ1, що здійснює зв'язок ЛШ і СШ і встановлений у режим IOВ=1. При цьому командні сигнали керування пам'яттю (MRDC, MWTC) надходять на СШ, а командні сигнали керування уведенням – виводом (IORC, IOWC), а також сигнал INTA – на РШ. Повна схема включення арбітра шин і схем шинного інтерфейсу в даному режимі наведена на мал. 5.25.

Підключаючи зовнішній дешифратор до адресних ліній ЛШ, можна перенести частина простору адрес пам'яті на пристрої уведення – виводу резидентної шини (мал. 5.26). При цьому можна використовувати проекцію адрес для поділу адресного простору пристрою уведення – виводу між СШ і РШ і підключити його до СШ із відображенням на пам'ять.

Режим роботи із системною шиною й якою-небудь шиною задається установка сигналів IOB = RESB = 1. Ця комбінація сигналів використовується в системах, де є як системна, так і якою-небудь шини, причому кожна з них забезпечує доступ до пам'яті й ПВВ (мал. 5.27).

Сигнал AEN = 0, доступ, що забезпечує, до СШ, виробляється, коли SYSB/RESB = 1 (якщо арбітр шин активний, тобто в системі немає арбітрів з більше високим пріоритетом, які використовують СШ). Для формування сигналу, що забезпечує вирішення доступу до СШ SYSB/RESB = 1 або до РШ SYSB/RESB=0, можна використовувати будь-який дешифратор адрес, підключений до ЛШ. Повна схема включення АШ і СШІ в цьому режимі наведена на мал. 5.28.

Режим роботи із системною шиною пам'яті, якою-небудь шиною й якою-небудь шиною уведення – виводу задається установкою сигналів IOВ = 0 і RESB = = 1. Цю комбінацію сигналів можна використовувати в системах, де поряд із системної шиною, що забезпечує доступ тільки до пам'яті, є дві якою-небудь шини. Одна РШ здійснює доступ як до пам'яті, так і до ПВВ, інша – тільки до ПВВ. Якщо врахувати, що весь простір адрес ЛШ розбито на дві частини (адресний простір пам'яті й адресний простір ПВВ), то використання РШ тільки для зв'язку з ПВВ недоцільно, тому що через неї був би забезпечений доступ до тих же зовнішнім пристроям, що й через першу РШ. Тому даний режим рідко використовується на практиці.

При функціонуванні арбітра шин у будь-якому режимі важливі тільки два процеси: захоплення шини і її звільнення. Чергування пасивних («-») і активних (« + ») станів АШ відбувається відповідно до табл. 5.3 і не представляє особливого інтересу.

Захоплення шини арбітром здійснюється при наявності умови доступу до СШ (табл. 5.3). Послідовність захоплення шини починається, коли МП, що не управляє шиною, виконує команду, що вимагає доступу до СШ. До цього моменту АШ пасивний і, як тільки він одержить код відповідного стану S2--S0, переходить в активний стан. Залежно від стану інших арбітрів системи даний АШ може почати захоплення негайно або після деякої тимчасової затримки. У кожному разі перший цикл звертання до СШ повинен забезпечити АШ час для захоплення шини. Тому сюди додаються такти очікування TW між періодами ТЗ і Т4 перші цикли. На мал. 5.29 представлені тимчасові діаграми послідовності захоплення в залежності or режиму роботи АШ. На цих трьох діаграмах дійсна зміна стану МП,

відбувається в точці А. Зчитування коду стану S2 SI S0 в АШ синхронізується шинним тактовим генератором у такий спосіб. RESB = 0 (мал. 5.29, а, б) синхронізація із шинним тактовим генератором здійснюється в точці В по першому зріз BCLK після встановлення сигналу CLK = 1 у такті Т1. Коли RESB = = 1 (мал. 5.33, в), синхронізація в точці У відбувається під час першого зрізу BCLK при CLK – 1 у такті Т2. Після закінчення одного періоду сигналу BCLK арбітр зчитує стан МП і переводить вихідні сигнали BREQ і CBRQ в активний стан (крапка З). Далі, якщо системна шина вільна (BUSY= 1) і сигнал BPRN = 0 не вносить тимчасової затримки, то через один

період BCLK установлюється вихідний сигнал BUSY = 0 і одночасно вихідний сигнал CBRQ стає рівним одиниці (крапка D). У ряді випадків виникає невизначена ситуація, пов'язана із взаємним розташуванням фронтів тактових імпульсів CLK і BCLK, що ілюструється мал. 5.29, б, де зріз сигналу BCLK формується приблизно по зрізі сигналу CLK-1 у такті Т1. У цьому випадку стан МП може бути записане в АШ негайно (суцільні лінії) або через один період сигналу BCLK штрихові лінії.

Відповідно з'являється залежна від режиму максимальна й мінімальна затримка між дійсною зміною стану МП (крапка А) і видачею сигналу запиту шини BREQ (крапка З). Ці затримки наведені в табл. 5.4 для різних режимів роботи АШ.

Звільнення шини арбітром здійснюється залежно від умов (див. табл. 5.2), певних вхідними сигналами LOCK, BPRN, CRQLCK, CBRQ, ANYRQST і станом МП. Послідовність звільнення ілюструє мал. 5.30.

Організація пріоритетного арбітражу. Було показано, що процеси захоплення, утримання й звільнення шини арбітром включають аналіз відповідних умов. Кожний АШ багатопроцесорної системи володіє стосовно інших арбітрів певним пріоритетом, що може бути встановлений шляхом реалізації різних методів пріоритетного арбітражу. Арбітр шини забезпечує реалізацію трьох методів: паралельного, послідовного й циклічного дозволу пріоритетів. Кожний метод реалізується за Допомогою певної схеми об'єднання арбітрів.

АШ подається сигнал дозволу доступу до шини. Цей сигнал дозволяє арбітрові здійснювати операції по захоплення системної шини.

Таблиця 5.4

|

Режим роботи |

| ||

|

IOB |

|

|

|

|

0 |

|

|

|

|

0 |

|

|

|

|

1 |

|

|

|

|

1 |

|

|

|

Схема паралельного дозволу пріоритетів (мал. 5.31) має найбільш широкі можливості. Для її реалізації необхідно використовувати додатковий пріоритетний контролер, що складається із шифратора пріоритетів і дешифратора. Сигнали з виходу запиту шини BREQ кожного АШ подаються на входи шифратора пріоритетів, що формує двійковий код запиту з найбільшим пріоритетом. Цей код дешифрується, і на вхід BPRN обраного Схема послідовного дозволу пріоритетів (мал. 5.32) є найбільше простій і виключає необхідність у пріоритетному контролері. В іншому випадку АШ з'єднуються між собою послідовно. Вихід пріоритетного дозволу доступу BPRQ арбітра з більше високим пріоритетом з'єднується із входом пріоритетного дозволу доступу BPRN арбітра з більше низьким пріоритетом. В арбітра шин з вищим пріоритетом (АШ1) вхід BPRN «заземлюється». Якщо мікропроцесор арбітра з більше високим пріоритетом не використовує СШ, то він передає отриманий пріоритет наступний за ним АШ. При такому з'єднанні пріоритет до останнього арбітра приходить із затримкою, пов'язаної із процесом передачі пріоритету від арбітра до арбітра. Тому що розподіл СШ повинне вироблятися за один період сигналу BCLK, те при тактовій частоті до 10 Мгц можливо послідовне з'єднання не більше трьох арбітрів.

Взаємодія АШ, включених за схемою послідовного дозволу пріоритетів, пояснюється тимчасовими діаграмами (мал. 5.33). Покладемо арбітр АШ1 утримує шину й формує сигнал BUSY = 0. Арбітр АШ2 запитує доступ до шини, формуючи сигнал запиту шини BREQ2 = 0. Оскільки в цей момент часу BPRN2-1, арбітр АШ2 видає вихідний сигнал загального запиту CBRQ, повідомляючи арбітра АШ1 по входу CBRQ, що арбітр із більше низьким пріоритетом запитує доступ до шини. Коли арбітр АШ1 звільнить шину, він формує сигнал BPRO = 0, зв'язаний із входом BPRN2 арбітра АШ2, і вихідний сигнал BUSY=1. Арбітр АШ2, одержавши сигнал вхідного пріоритету BPRN2 -ПРО, формує сигнал CBRQ=1 і займає шину по негативному фронті BCLK, формуючи вихідний сигнал BUSY = 0.

Арбітрові з більше високим пріоритетом при запиті доступу до шини пріоритет вертається швидше, ніж інший АШ встигне захопити системну шину, запитуючи її сигналом CBRQ.