- •1 Аналіз інформаційних мереж 10

- •1 Аналіз інформаційних мереж

- •1.1 Види мереж

- •1.2 Особливості та призначення корпоративних мереж, історія розвитку

- •1.3 Опис корпоративної мережі, що досліджується

- •2 Дослідження канального рівня мережі

- •2.1 Обгрунтування стандартизації функцій інформаційних мереж міжнародною спілкою електрозв’язку

- •2.2 Передача даних на канальному рівні

- •2.2.1 Протоколи канального рівня

- •2.2.2 Система опитування/вибір

- •2.2.3 Двійкове синхронне керування

- •2.2.4 Режими каналу

- •2.2.5 Високорівневе керування каналом (hdlc)

- •2.2.6 Формат у кадрі hdlc

- •2.2.7 Кодонезалежність і синхронізація hdlc

- •2.2.8 Керуюче поле hdlc

- •2.2.9 Протокол sdlc

- •2.2.10 Перетворення протоколів

- •3 Функціональна схема роботи кінцевого і центрального вузлів мережі

- •3.1 Склад та функції мережі

- •3.2 Функціональна схема кінцевого вузла (кв) мережі

- •3.2.2 Вихідний виклик до центрального вузла.

- •3.2.3 Вхідний виклик від центрального вузла

- •3.3 Функціональна схема центрального вузла (цв) мережі

- •3.3.1 Вихідний стан.

- •3.3.2 Вихідний виклик всіх кв по черзі

- •3.3.3 Виборочний вихідний виклик до кв

- •3.3.4 Вхідний виклик від кв

- •4. Розробка алгоритму канального рівня

- •4.1 Обгрунтування вибору середовища програмування Delphi

- •4.2 Структура програмного забезпечення

- •4.3 Опис алгоритму роботи канального рівня центрального вузла

- •4.4 Опис алгоритму роботи канального рівня кінцевого вузла

- •4.4.1 Процедура формування блоку для передачі FormBlock

- •4.4.2 Процедура передачі блоку рівню 1 PdBlock

- •4.4.3 Процедура прийому блоку від рівня 1

- •Висновки

- •Перелік посилань

- •Додаток а програма канального рівня

- •Додаток б перелік команд які використовуються в алгоритмах

- •Додаток в перелік прапорців

- •Додаток г перелік тайм-аутів

- •Обов’язкові креслення

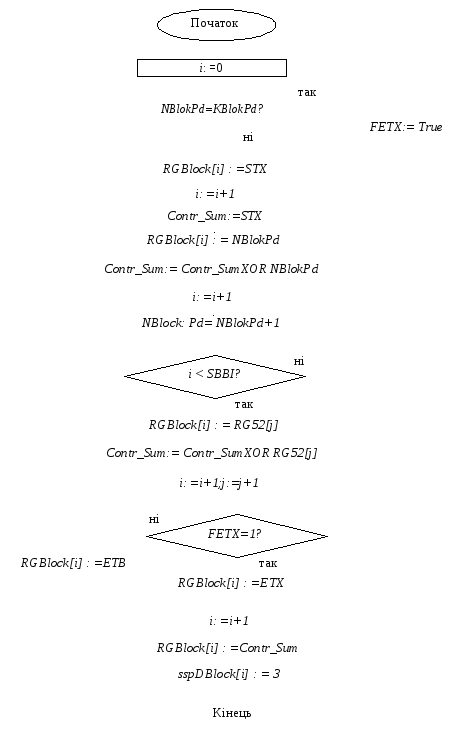

4.4.1 Процедура формування блоку для передачі FormBlock

Блок складається з наступних складових: „Початок блоку”, „Номер блоку”, „Інформація”, „Кінець блоку”, „Перевірочна інформація” (рисунок 4.32)

Для створення перевірочної інформації використовується метод формування суми по модулю 2.

|

Початок блоку |

№ блоку |

Інформація |

Кінець блоку |

Перевірочна інформація |

Рисунок 4.2 - Блок другого рівня

Алгоритм процедури формування блоку для передачі наведений на рисунку 4.3.

На початку підпрограми формування блоку для передачі треба встановити лічильник байт блоку (і) в 0. Якщо блок останній, то встановлюємо прапорець кінця кадру FETX в активний стан. Далі записуємо в регістр RGBlock ознаку початку блоку STX, збільшуємо значення покажчика (і), записуємо STX в чарунку Contr_Sum, де буде формуватись контрольна сума блоку (по модулю 2),

записуємо в RGBlock номер блоку NBlockPd, здійснюємо складання по модулю 2 Contr_Sum та NBlockPd, збільшуємо на одиницю значення покажчика (і) та NBlockPd і приступаємо до запису 16-ти байт інформації з регістра RG52 в регістр RGBlock. При цьому кожний інформаційний байт враховується в Contr_Sum. Коли всі інформаційні байти записані в регістр для передачі блоку, треба записати ознаку кінця блоку. Якщо блок останній в кадрі, то в регістр RGBlock записується ETX, а якщо ні, то записується ETB. Ці байти не враховуються при формуванні контрольної суми блоку. Останньою в RGBlock записується контрольна сума блоку Contr_Sum.

Оскільки в інформаційній мережі, що розробляється, використовується вирішуючий зворотній зв’язок, то при надходженні на прийом пошкодженого блоку ми отримаємо негативну квитанцію на нього (NAK) і цей блок треба буде повторно передати, необхідно обмежити кількість повторних передач для запобігання за циклювання програми. Для цього в лічильник повторних передач блоку SSPdBlock в кінці формування блоку записуємо 3 (допустима кількість повторних передач блоку).

Рисунок 4.3 - Формування блоку для передачі

4.4.2 Процедура передачі блоку рівню 1 PdBlock

Алгоритм процедури передачі блоку наведений на рисунку 4.4.

Оскільки після передачі блоку ми можемо отримати у відповідь квитанції – позитивну (ACK), негативну (NAK), або вимогу розпочати передачу всього кадру спочатку (DLE), то перед передачею блоку треба встановити в неактивний стан прапорці FACK, FNAK, FDLE. Крім того, для запобігання зависання програми при ненадходженні квитанції на переданий блок, починаємо відлік тайм-ауту Т23 (час очікування відповіді на блок). Покажчик регістру RGBlock (і) встановлюємо на перший байт блоку.

Після послідовної передачі всіх байтів блоку чекаємо квитанцію на переданий блок. В мережі використовується вирішуючий зворотній зв’язок з очікуванням. Якщо за час тайм-аута Т23 не надійшла очікувана відповідь (ACK, NAK або DLE) підпрограма закінчує свою роботу. Якщо ж надійшла одна з очікуваних квитанцій, встановлюється відповідний прапорець.

4.4.3 Процедура прийому блоку від рівня 1

Ця процедура призначена для прийняття інформації від фізичного рівня.

Алгоритм процедури представлений на рис. 4.5. Він полягає в наступному. Спочатку треба зробити початкові установки: покажчик на регістр прийому RGBlock (i) встановити в 0; прапорці FACK, FNAK, FDLE встановити в неактивний стан. Для запобігання зависання програми необхідно розпочати відлік тайм-ауту Т24 (час прийому повного блоку).

Тепер перевіяється, чи надійшла інформація з каналу на фізичний рівень, якщо знаку немає і тайм-аут Т24 не закінчився – повертаємося на очікування байта від рівня 1. Якщо байт надійшов, то це має бути номер блоку, який зараз приймається (NBlock). При невідповідності прийнятого і очікуваного номера блоку може бути два варіанти. У першому випадку номер блоку, що приймається, менший від очікуваного, тобто цей блок вже був прийнятий. В такому разі треба встановити прапорець FACK (ознака того, що потрібнов передати позитивну квитанцію на цей блок) в активний стан, дочекатись кінця прийому всього блоку і вийти з підпрограми. У другому випадку номер блоку, що приймається, більший від очікуваного, тобто була втрата блоку. Виправити таку помилку можна тільки розпочавши прийом всього кадру спочатку. Для цього встановлюється в активний стан прапорець FDLE, дочекатись кінця прийому всього блоку і вийти з підпрограми.

При відповідності прийнятого і очікуваного номера блоку виконуємо операцію „складання по модулю 2” чарунки Contr_Sum і NBlock, і переходимо до прийома інформаційних байт блоку. При прийомі кожного байту інформації його треба переписати в регістр RGBlock, врахувати його в контрольній сумі блоку Contr_Sum (виконати операцію „складання по модулю 2”), і збільшити покажчик регістра RGBlock (і).

Рисунок 4.4 - Алгоритм процедури передачі блоку

Коли 16 інформаційних байт блоку прийняті, чекаємо ознаку кінця блоку. Це може бути ETB (кінець блоку) або ETX (кінець тексту, тобто кінець кадру). В останньому випадку прапорець FETX необхідно встановити в активний стан.В кінці блоку повинна надійти контрольна сума блоку, яка порівнюється з тією контрольною сумою, яка підрахована в чарунці Contr_Sum. Якщо контрольна сума неправильна, це означає, що в блоці була помилка і треба встановити в активний стан прапорець FNAK. У випадку правильності контрольної суми встановлюємо в активний стан прапорець FACK, якщо до цього часу не була зафіксована помилка.

Під час роботи підпрограми весь час перевіряється тайм-аут Т24. Якщо блок не прийнятий за час Т24 підпрограма закінчує роботу.

Рисунок

4.5

- Алгоритм процедура прийому блоку

Рисунок

4.5

- Алгоритм процедура прийому блоку