14 Программируемые логические интегральные схемы

Функциональные особенности современных цифровых устройств требуют в каждом отдельном случае разработки сложных индивидуальных алгоритмов, что определяет либо рост числа корпусов интегральных схем малой и средней степени интеграции, либо выпуска специализированных больших и сверхбольших интегральных схем (БИС, СБИС). В первом случае сравнительно большое число функциональных единиц увеличивают потребляемую мощность, снижают быстродействие, лишают возможности гибкой модернизации. Во втором – применение зависит от стоимости элементов и целесообразно только при огромных объемах серийного производства разрабатываемых устройств.

Промежуточным вариантом является проектирование цифровой техники с применением элементов, обладающих функциональной универсальностью и избыточностью, позволяющих разработчику без дополнительных затрат времени и средств вносить изменения в алгоритмы и схемы. Подобные устройства получили название «ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ» (ПЛИС). При этом под программированием понимается не изменение кодов программы, заносимое в ПЗУ, а физическое изменение внутренней структуры и связей на аппаратном уровне.

Универсальность ПЛИС достигается избыточностью базовых элементов в конструкции, что увеличивает стоимость по отношению к жестко функциональным микросхемам, но гораздо дешевле производства специализированных БИС и СБИС. То же можно сказать и о быстродействии – оно выше по отношению к серийной логике, уступая высоко интегрированным, но плата за снижение скорости – многофункциональность.

Применение ПЛИС в логических устройствах становится целесообразным, в том случае, когда количество корпусов микросхем малой и средней степени интеграции достигает в конструкции 60-70 шт.

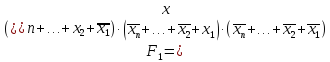

Принцип ПЛИС заложен основой теории алгебры логики, согласно которой логическую функцию Fi любого элемента (функция алгебры логики – ФАЛ) можно представить в форме системы уравнений, состоящих из сумм произведений входных логических переменных или их произведений сумм (см. рисунок 14.1).

Рисунок 14.1 – Элемент ПЛИС

Первая система уравнений известна, как совершенная дизьюнктивная нормальная форма (СДНФ), вторая – совершенная коньюнктивная нормальная форма (СКНФ).

В общем случае СДНФ имеет вид:

· · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · ·

Число произведений (коньюнкций) входных переменных в каждом уравнении не может быть больше, чем максимальная емкость двоичного кода, составленного из входных переменных, т.е. 2n (n – количество входных переменных). Каждая коньюнкция составляется на основе таблицы истинности (состояния).

При построении каждого уравнения системы применяют несложный алгоритм:

- для ФАЛ равной единице (согласно таблице состояния) записывают произведения всех входных (логических) переменных, при этом переменные равные нулю включаются в элементарную коньюнкцию с инверсией; полученные, таким образом произведения называют конституентами единицы (в конституенту единицы переменная или ее инверсия может входить только один раз);

- полученные конституенты единицы суммируют.

Полученная функция, состоящая из сумм конституент единицы и есть СДНФ.

Построение СКНФ с использованием таблицы истинности – процедура подобна предыдущей, с той лишь разницей, что создают конституенты нуля, суммируя переменные с ФАЛ равной нулю, при этом переменные равные единице входят в сумму с инверсией. Полученные конституенты нуля перемножают:

· · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · · ·

Реализация ФАЛ в форме СДНС или СКНС требует логических элементов трех типов: «И» (логическое умножение), «ИЛИ» (логическое сложение), «НЕ» (логическая инверсия). Для примера в таблице 14.1 приведена ФАЛ трех входового логического элемента, СДНС которого имеет вид:

Таблица 14.1 – Таблица истинности (состояний)

|

X2 |

X1 |

X0 |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

Универсальная функциональная схема ПЛИС, построенная на основе СДНФ представлена на рисунке 14.2

Входные (выходные) каскады формируют инверсные переменные (выборочно), согласуют параметры входа с выходом источника информации, обеспечивают нагрузочную способность выходов и т. д.

На матрицу «И» поступают прямые информационные сигналы Хi либо инвертированные (согласно разработанной ФАЛ). С выхода матрицы «И» конституенты единицы подаются в матрицу «ИЛИ», на соответствующем выходе которой формируется требуемая логическая функция.

Рисунок 14.2 – Функциональная схема ПЛИС

Структуры логических матриц «И», «НЕ»(входные), «ИЛИ» являются перестраиваемые пользователем (программируемые, перепрограммируемые) подобно РПЗУ, поэтому разработчик имеет возможность динамично реализовать ФАЛ произвольного вида.

С учетом структурно-архитектурных особенностей ПЛИС могут быть разделены на группы (см. рисунок 14.3):

- программируемые логические матрицы (ПЛМ);

- программируемая матричная логика (ПМЛ);

- базовые матричные кристаллы (БМК);

- программируемые вентильные матрицы (ПВМ);

- программируемые коммутируемые матричные блоки (ПКМБ);

- комбинированные ПЛИС.

Рисунок 14.3 – Классификация ПЛИС

14.1 Программируемая матричная логика

Программируемая матричная логика (ПМЛ) появилась в начале 80-х годов 20 столетия. Она позволяет изменять выборочно структуру связей либо в матрице «И», либо в матрице «ИЛИ». Функциональная схема ПМЛ с программируемой матрицей «И», приведенная на рисунке 14.4, реализует ФАЛ таблицы 14.1.

Рисунок 14.4 – Функциональная схема ПМЛ

Входной блок инверторов формирует соответствующие инверсные входные сигналы, которые совместно с прямыми поступают на входную матрицу «И». Трех входовые логические перемножители за счет комбинируемой пользователем структуры коммутации позволяют корректировать архитектуру ФАЛ (конституенты единицы) по каждому «И» элементу. Коммутация входных цепей матрицы «ИЛИ» не требует доступности пользователя.

В зависимости от конструктивных особенностей ПМЛ могут иметь изменяемую структуру матрицы «И» при неизменной структуре «ИЛИ» или - постоянную «И», но изменяемую «ИЛИ».

Среди отечественных ПМЛ следует отметить микросхемы К1556ХЛ8, К1556ХП4, К1556ХП6, К1556ХП8, относящиеся к ТТЛШ логике.

14.2 Программируемые логические матрицы

В программируемых логических матрицах (ПЛМ) разработчику доступна структура как матрицы «И», так и «ИЛИ». Функциональная схема ПЛМ приведена на рисунке 14.5. В изображении программируемой матрицы часто многовходовые матрицы «И» и «ИЛИ» условно изображают в форме одновходовых. Количество входов в каждом конкретном случае определяется числом пересечений с выходной сигнальной линией.

Рисунок 14.5 – Функциональная схема ПЛМ

Контакт выходной сигнальной лини со входом матрицы «И» («ИЛИ») осуществляется в подобных микросхемах пережиганием разработчиком нихромовой (диодной, транзисторной) перемычки, подобно программированию ППЗУ.

Примером отечественных ПЛМ является микросхема К556РТ1, РТ2, РТ3, имеющие 16 входных и 8 выходных разрядов. Максимальное количество термов (конституент единицы) – 48. Для расширения числа обрабатываемых информационных входов и выходов можно наращивать разрядность увеличением количества микросхем.

14.3 Базовые матричные кристаллы

Базовые матричные кристаллы (БМК) появились на рынке в качестве альтернативы заказным БИС и СБИС. Они получили название полузаказных БИС и СБИС.

Они представляют собой полупроводниковый кристалл с расположенными на нем электронными (функционально законченными) элементами (базовыми ячейками - БЯ), которые могут быть различным образом соединяться и объединяться в более сложные схемы. Для создания соединений между БЯ на кристалле остаются свободными зоны, названные горизонтальными и вертикальными каналами (см. рисунок 14.6) для трассировки.

БМК в зависимости от требований потребителя (полузаказная БИС) делятся на аналоговые, логические и аналого-цифровые. В аналоговых в качестве БЯ используют операционные усилители и коммутаторы. В цифровых – буферные элементы, многовходовые элементы «И», «ИЛИ», контактные площадки.

Рисунок 14.6 – Функциональная схема БМК

Примером отечественной БМК является микросхема К1520ХМ6 (ЭСЛ логика). БМК выполняются по ТТЛШ, ЭСЛ, КМОП технологиям.

14.4 Программируемые вентильные матрицы

Программируемые вентильные матрицы (ПВМ) являются результатом модернизации БМК. В ПВМ часть базовых ячеек выполняют более сложную функцию, например, многовходовых «исключающее «ИЛИ», а вместо контактных площадок для соединения и разводки используют шифраторы-дешифраторы, мультиплексоры – законченные электронные блоки ввода-вывода. Наличие в ПВМ программируемых матриц соединений переводит их из разряда полузаказных в разряд готовых микросхем, но имеющих функцию программирования пользователем.

Отечественная электронная промышленность ПВМ не выпускает.

14.5 Программируемые коммутируемые матричные блоки

СПИСОК ИСПОЛЬЗОВАНЫХ ИСТОЧНИКОВ

1. Лачин В.И., Савелов Н.С. Электроника: Учеб. пособие. 4-е изд. – Ростов н/Д: изд-во «Феникс», 2004г.- 576 с. ил.

3. Аналоговые и цифровые интегральные микросхемы: Справочное пособие /С.В. Якубовский, Н.А. Барканов, Л.И. Ниссельсон и др.; Под ред. С.В. Якубовского. – М.: Радио и связь, 1984.- 432с., ил. – (Проектирование РЭА на интегральных микросхемах).