Логическое устройство

Вх2

Вх2

t

Вых

t

а

ВхA1

t

t

t

t

ВхA2

t

ВхA1

ВхA2

ВхB1

ВхB2

Вых1

Вых2

ВхB2

ВхB1

Логическое устройство

t

ВхB2

t

t

t

Вых1

Вых2

б

а – последовательное логическое устройство и диаграммы его работы, б – параллельное логическое устройство и диаграммы его работы

Рисунок 3.1 – Последовательное и параллельное логические устройства

ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Для потенциального способа (используются напряжения двух уровней условно принятых за уровень «логического нуля» и «логической единицы» - см. раздел 1.1) среди элементарных логических устройств по функциональным особенностям (реализуемой функции) можно выделить следующие элементы:

- элемент ИЛИ (логическое сложение - Увых= Х1 + Х2 + … +Хn);

- элемент И (логическое умножение - Увых= Х1 ∙ Х2 ∙ … ∙Хn);

- элемент НЕ

(логическоя отрицание, инверсия -

);

);

- повторитель (Увых= Х).

Обозначение на принципиальных схемах элементов, реализующих выше представленные функции, приведено на рисунке 4.1.

1

1

&

Х1

Х2

У

У

Х1

У

«ИЛИ»

Х2

1

У

Х

«И»

«НЕ»

Рисунок 4.1 – Простейшие логические элементы

4.1 Основные параметры логический элементов

Наиболее часто в цифровой технике используются следующие характеристики логических элементов:

- коэффициент объединения по входу;

- нагрузочная способность;

- быстродействие;

- помехоустойчивость.

Коэффициент объединения по входу определяет число входов элемента способных принимать логические переменные. Этот параметр характеризует потенциальные возможности: чем он больше, тем шире функциональная характеристика элемента.

Нагрузочная способность (коэффициент разветвления по выходу) говорит о числе логических входов (однотипных), на которые одновременно (параллельно) может подаваться выходной сигнал. От нагрузочной способности зависит число элементов, входящих в законченное цифровой устройство.

Быстродействие можно отнести к важнейшим показателям функционирования логического элемента. Этот параметр зависит от времени задержки передачи сигнала с входа на выход. Иными словами, быстродействие определяется временем между изменением сигнала на входе до появления функционально соответствующих изменений выходного логического сигнала. Задержка сигнала с учетом параметров формы импульса (см. рисунок 1.2) в полной мере связана с соотношением tИ , tФ и tС. Чем больше tФ и tС , тем ниже быстродействие. Время задержки рассчитывается по справочным характеристикам. На рисунке 4.2 представлены идеализированный пример формы входного и выходного сигналов обычного инвертора.

t

t

tЗ1,0

tЗ0,1

Рисунок 4.2 – Параметры задержки импульсных элементов

tЗ1,0 – время задержки переключения элемента из состояния лог.1 в состояние лог.0.

tЗ0,1– время задержки переключения элемента из состояния лог.0 в состояние лог.1.

Среднее время

задержки определяется как

Среднее время задержки используется при расчете суммарного времени распространения сигналов в сложных цифровых схемах.

Помехоустойчивость – есть максимальное значение внешнего фактора, не вызывающего нарушения работы логического элемента в статическом режиме.

U1

U0вых

Uвх

U0п

U1п

U1вых

Рисунок 4.3 – Диапазон помехоустойчивости дискретного элемента

На рисунке 4.3 изображена форма зависимости выходного сигнала инверсного логического устройства от уровня входного напряжения. В статическом режиме при увеличении Uвх до U0п выходное напряжение незначительно падает. В интервале U0п < Uвх < U1п выходной сигнал резко меняет свою амплитуду U1вых < Uвых < U0вых.

Таким образом, амплитуда помехи, не приводящая к изменению статического состояния элемента без изменения входной информационной составляющей (например, при короткозамкнутых входных цепях) называется предельной.

Помехозащищенность характеризуется предельной амплитудой помехи.

4.2 Диодные ключи

Импульсные сигналы получают путем коммутации электрических цепей. При этом в качестве коммутирующих электронных элементов применяют:

- диоды;

- биполярные транзисторы;

- полевые транзисторы.

Основное достоинство диодных матриц – их простота – при интегральной технологии не дает никаких преимуществ. На практике подобные схемные решения применяют при использовании навесного монтажа РЭА и в случае вынужденной замены вышедших из строя простейших логических элементов.

На рисунке 4.4 изображен диодный логический элемент, реализующий функцию «И». Разрядный разомкнутый переключатель формирует на катоде соответствующего диода запирающий потенциал. В этом случае при Rн >> R, все напряжение источника питания Uп приложено к активно-емкостной нагрузке, форма сигнала на которой будет определяться постоянной времени заряда зар = R Cн (ток через закрытый диод не проходит). Если разрядный переключатель соединить с общим проводом, диод откроется и емкость нагрузки Сн начнет разряжаться через малое сопротивление открытого диода rd (rd << Rн). Форма спада формируется постоянной времени цепи разряда раз = rd Cн . Наличие хотя бы одного нулевого уровня на входных клеммах приведет к шунтированию Rн малым входным сопротивлением источника и, как следствие, нулевому сигналу на выходе (напряжение питания будет падать на R). Единичный уровень, поданный на все разрядные входы (все переключатели разомкнуты) приведет к появлению единицы на выходе – классический пример реализации логической функции «И» («1» на выходе появляется только тогда, когда в состоянии «1» находится И 1-ый вход, И 2-ой вход И … n – ый вход) .

Диодный логический элемент «ИЛИ» представлен на рисунке 4.5. Посредством разомкнутого многоразрядного переключателя единичный информационный уровень подается на диодную матрицу. Появление хотя бы одного единичного сигнала на любом из разрядов откроет соответствующий диод и единица с учетом постоянной времени заряда цепи нагрузки (ЗАР = RНСН) через открытый диод установится на выходе элемента. Нулевой выходной сигнал будет сформирован только после размыкания всех переключателей и разряда нагрузочной емкости через сопротивления RБ и RН). Форма спада определяется постоянной времени цепи разряда (раз = CН RН RБ /( RН + RБ)).

+Uп

Uвх1

VD1

Uвх2

VD2

Uвых

(Rн, Сн)

Uвх

VDn

Uвхn

а

Uвых

Uвхn

t

б

а – принципиальная схема; б – форма выходного сигнала

Рисунок 4.4 – Диодный элемент «И»

Uвх1 VDn VD1 Uвых (Rн,

Сн)

Uвых t а

Uвх2

VD2

Uвхn

+Uп

Uвых

зар

Uвхn

раз

б

а – принципиальная схема; б – форма выходного сигнала

Рисунок 4.5 – Диодная схема «ИЛИ»

Инвертор (элемент «НЕ», см. рисунок 4.6) образуют ключевым транзисторным инвертирующим каскадом. При низком уровне входного напряжения на выходе присутствует единица (транзистор закрыт, все напряжение питания приложено к нему) и, наоборот, при единичном входном воздействии на коллекторе транзистора установится ноль (транзистор входит в зону насыщения, напряжение питания падает на RК).

+Uп

Uвх

Uвых

RК

а

0

1

0

1

0

Uвх

Uвх

Uвых

0

t

1

0

1

1

б

t

а – принципиальная схема; б – рабочая диаграмма

Рисунок 4.6 – Транзисторный элемент «НЕ»

4.3 Классификация основных типов логических элементов

Кроме рассмотренных в предыдущем разделе диодных логических элементов существует исторически сложившаяся схемотехническая классификация основных типов транзисторных логических элементов.

В ней выделены следующие классы (типы логики) элементов:

- транзисторно-транзисторная логика (ТТЛ);

- эмиттерно-связанная логика (ЭСЛ);

- транзисторно-транзисторная логика с диодами Шотки (ТТЛШ);

- логика на полевых транзисторах (каналы n-МДП, p-МДП; комплементарные ключи на МДП-транзисторах – КМДП, КМОП);

- интегрально-инжекционная логика (И2Л);

- логика на основе полупроводника из арсенида галлия (GaAs).

Наиболее широко в настоящее время используются ТТЛ, ТТЛШ, КМОП, ЭСЛ. Перспективными сериями являются КМОП и GaAs технологии.

Серии на полевых транзисторах характеризуются малым потреблением энергии, что крайне актуально сегодня. Кроме того, хотя они и уступают ТТЛ и ТТЛШ логике в быстродействии, но имеют преимущество в помехозащищенности и перспективном потенциале.

В ближайшие годы серьезное внимание уделяется развитию технологии изготовления интегральных микросхем (ИМС) на арсениде галлия. Впятеро большая подвижность электронов в монокристаллах этого двухэлементного полупроводника, чем в кремнии, позволяет создавать в объеме арсенида галлия активные структуры с кратно более высоким быстродействием. Преимущество в быстродействии востребовано, прежде всего, в маломощных больших интегральных схемах (БИС). Широкому внедрению арсенида галлия в производство ИМС препятствуют трудности, связанные с обеспечением переноса параметров элементов на кристаллические структуры. Разброс характеристик получается намного больше, чем в случае использования кремния. Для сравнения: минимальное время задержки сигнала на КМОП структурах с диодами Шоттки составляет 0,12 нс, на арсениде галлия – 0,019нс.

Логические элементы и другие цифровые электронные устройства выпускаются в составе серий интегральных микросхем. Серия – это совокупность цифровых элементов, которые характеризуются общими технологическими и схемотехническими решениями, а также уровнями электрических сигналов и напряжений питания.

В обозначении серий логических элементов заключается ряд ключевых параметров. Для интегральных схем широкого применения перед обозначением серии ставится буква К, например, К561ЛА7.

Следующая за буквой цифра, в примере это 5, говорит о технологии производства интегральной микросхемы (ИМС). 1, 5, 6, 7 – полупроводниковые ИМС; 2, 4, 8 – гибридные; 3 – прочие.

Полупроводниковая ИМС – это микросхема, все элементы и внутренние соединения которой выполнены в объёме и на поверхности полупроводниковой пластинки.

Плёночная ИМС – это микросхема, все элементы и внутренние соединения которой выполнены в виде плёнок. Различаются толстоплёночные и тонкоплёночные ИМС.

Толстоплёночная ИМС – это микросхема, в которой все пассивные элементы, проводники и контактные площадки выполнены по толстоплёночной технологии на диэлектрическом основании, то есть подложке. Толстоплёночная технология – это вжигание резистивных, проводящих и диэлектрических паст в подложку. Толщина плёнок от 1 … 2 до 10 … 25 микрон.

Тонкоплёночная ИМС – это микросхема, в которой все пассивные элементы (проводники и контактные площадки) выполнены методом тонкоплёночной технологии на поверхности общего диэлектрического основания, подложки.

Тонкоплёночная технология – напыление тонких плёнок в вакууме.

Гибридная интегральная микросхема (ГИС) – это микросхема, в которой кроме тонкоплёночных элементов (проводников и контактных площадок на диэлектрической подложке) расположены навесные, бескорпусные дискретные элементы – транзисторы, диоды, резисторы, конденсаторы, катушки индуктивности.

Второй цифровой элемент (три цифры) обозначает порядковый номер разработки серии (от 000 до 999).

Третий элемент – две буквы, обозначающие подгруппу соответствующую функциональным особенностям элемента.

Четвертый элемент – условный номер разработки микросхемы по функциональному признаку.

И наконец замыкает ряд обозначений буква, характеризующая функциональные особенности, например, К573ПВ1А (Б,В). Данная ИМС (АЦП) с буквой «А» имеют линейность преобразования 0,1%, Б–1%, В–3%.

Транзисторно-транзисторные интегральные микросхемы – один из самых распространенных типов ИМС. Существует много разновидностей ТТЛ схем, однако, несмотря на некоторые различия, их объединяет принцип работы и основные характеристики. Упрощенная схема базового ТТЛ элемента приведена на рисунке 4.7.

VT1

VT2

Uвх1

Uвх2

VD2

R

RК

Uвх3

E

VD3

1

&

Х1

Х2

У

Рисунок 5.3– Приоритетный шифратор К555ИВ1

VD1

Х3

a

б

а – принципиальная схема ЛЭ «3И – НЕ» ТТЛ, б – условное обозначение

Рисунок 4.7 – Базовый элемент ТТЛ

На схеме можно выделить два основных каскада: входной на много эмиттерном транзисторе VT1, реализующем функцию «И» и усилительный с инвертированием на VT2. Если на всех входах присутствует логическая единица, эмиттерный переход VT1 оказывается смещенным в обратном направлении, на базе транзистора VT2 появляется ток через резистор R и смещенный в прямом направлении переход коллектора VT1, что открывает транзистор VT2 и потенциал его коллектора падает до нуля. При нулевом уровне хотя бы одного входного разряда соответствующий p-n переход шунтирует остальные переходы и нулевой сигнал снижает ток базы VT2, закрывая его и устанавливая на выходе единицу.

Диодные элементы во входных цепях защищают транзистор VT1 от пробоя. На рисунке 4.8 представлена форма входного тока в зависимости от уровня входного напряжения.

IВХ,mA

1

UВХ, В

-2

0

2

4

-1

-2

Рисунок 4.8 – Входная характеристика базового ЛЭ ТТЛ для Uп = 5 В

При единичном входном сигнале величина входного тока незначительна, т.к. эмиттерный переход смещен в обратном направлении вплоть до значения напряжения 5 В. При напряжении более 5,5 В на входе ток резко возрастает и достигает величины 1 мА. Это предельное значение тока, а следовательно и входного напряжения. Поэтому питание элементов ТТЛ ограничено значением UП = 5В 10% . Аналогично идет рост входного тока при наличии отрицательного входного потенциала. Для большинства ТТЛ ИМС эта величина не может превышать значение UВХ > - 0,4В. Для защиты эмиттера входного транзистора от выбросов отрицательного потенциала устанавливаются демпфирующие диоды VD1÷VD3.

В динамическом режиме (tФ и tС) в оконечных каскадах реальных ТТЛ элементов существует момент короткого замыкания, объясняемый задержками переключения активных структур. В это время от источника потребляется большой ток. Следовательно, чем выше частота цифрового сигнала, тем выше энергопотребление. Кроме того броски тока вносят помехи в информационные сигналы. С целью защиты от помех такого рода цепи питания ТТЛ микросхем шунтируют емкостями СШ 100 нФ на каждый корпус.

Микросхемы эмиттерно-связанной логики (ИМС ЭСЛ) представляют собой транзисторные переключательные схемы с объединенными эмиттерами и обладают по сравнению с другими типами цифровых ключей наибольшим быстродействием и большой потребляемой мощностью. Большое быстродействие (малое tСР) определяется работой активных элементов в ненасыщенном (линейном) режиме, ограничения перепада выходного логического сигнала, включения в выходных каскадах эмиттерных повторителей [ 3 ]. Из разработанных ИМС ЭСЛ наиболее широкое распространение получили серии 100 и К500 являющиеся аналогами импортной серии МС 10000 фирмы Motorola.

Рисунок 4.9 – Элемент ЭСЛ «ИЛИ-НЕ, ИЛИ»

Питание ЭСЛ осуществляется от источника напряжения UП = -5В, (см. рисунок 4.9) коллекторные цепи заземляются. Такое включение обеспечивает меньшую зависимость выходного сигнала от наводок по цепи питания и лучшую помехоустойчивость. Уровень логического нуля лежит в пределах U0 = - 1,7 B, логической единицы - U1 = - 0,9 B (ЭСЛ считается положительной логикой). Значение перепада напряжения для ЭСЛ составляет 0,7-0,8 В. Отрицательные и малые перепады уровней требуют для стыковки с элементами серии ТТЛ применения специальных схем (преобразователи уровней), которые входят в состав всех указанных серий ЭСЛ.

На примере элемента «ИЛИ-НЕ и ИЛИ» (см. рисунок 4.9) представлен принцип работы ключа ЭСЛ. Схема состоит из сложного дифференциального каскада, собранного на транзисторах VT1-VTn, VTд. В этом каскаде потенциал VTд базы определяется напряжением смещения (UОП = - 2В), которое стабилизируется каскадом (VTэс, Rc1, VD1, VD2, Rэс) эмиттерного повторителя с элементами термостабилизированной цепи в базе транзистора. При напряжении на входных транзисторах большем напряжения смещения VT1-VTn будут закрыты, а транзистор VTд будет открыт и его коллекторный потенциал низкого уровня (U0 = - 1,7 B) будет через выходной эмиттерный повторитель (VTэ2) присутствовать на прямом выходе «Вых. ИЛИ» элемента. Если хотя бы на одном входном транзисторе появиться уровень логической единицы (U1 = - 0,9 B), он откроется и за счет ООС на Rэ закроет VTд. На выходе первого эмиттерного повторителя VTэ1 появится сигнал инверсный входному (U0 = - 1,7 B), VTэ2 установит сигнал единицы (U1 = - 0,9 B).

Выходные эмиттерные повторители подключаются к источнику смещения (UСМ = - 2,0 B 5%) через внешние нагрузочные резисторы RН1 и RН2 с номиналом 51 Ом. Малое выходное сопротивление элемента обеспечивает согласование выходных и входных напряжений уровней логических элементов при их совместной работе и возможность непосредственно подавать сигналы в коаксиальный кабель с волновым сопротивлением 50 Ом.

Функциональные возможности серий ЭСЛ не уступают другим сериям. В их состав входят элементарные логические элементы («И», «ИЛИ») дешифраторы, мультиплексеры, запоминающие и арифметические устройства.

Транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ) уменьшает время переключения элементов ТТЛ до единиц наносекунд. Это быстродействие достигается введением в схему диодов Шоттки, у которых практически отсутствует диффузионная емкость р-n перехода, что поднимает частотный диапазон подобных полупроводниковых диодов до десятков ГГЦ. Диоды Шоттки добавляются в обычный базовый элемент ТТЛ (см. рисунок 4.10). Включение диодов в обратном направлении параллельно коллекторному переходу транзистора и такого же диода в цепь базы в прямом направлении (для компенсации падения напряжения на открытом диоде) позволяет избежать насыщения транзистора, свести время рассасывания к нулю и тем самым значительно увеличить быстродействие элемента.

К серии ТТЛШ микросхем относятся ИМС К1533, К530, К531, К555. Все они характеризуются следующими параметрами:

- напряжение питания + 5 В;

- напряжение низкого уровня не более 0,4 В;

а – принципиальная схема каскада, б – изображение на схеме транзистора Шотки

Рисунок 4.10 – Входной каскад базового ТТЛШ элемента

- напряжение высокого уровня не менее 2,4 В;

- среднее время задержки распространения сигнала tСР 5нс;

- максимальная частота 50 МГц.

ИМС ТТЛШ совместимы по уровню с микросхемами ТТЛ. Мощность потребляемая ТТЛШ элементами меньше соответствующих ТТЛ схем в 5-10 раз.

Интегрально-инжекционная логика (И2Л) построена на основе биполярных транзисторов с непосредственными связями. Элементы И2Л отличаются относительно высоким быстродействием (tСР 5-7нс), низкими уровнями питания (0,5-0,9 В) и логических сигналов, очень малым перепадом напряжения переключения.

Логика функционирует на транзисторах с инжекционным питанием. Подобные полупроводниковые структуры реализованы только в интегральном исполнении и не имеют аналогичных решений в дискретной схемотехнике.

Инжекционные схемы питаются через инжекторный переход смещенный в прямом направлении, что дает возможность снизить напряжение питания до 0,6-0,7 В для кремниевых и 0,3-0,4 В для германиевых структур. Число внутрисхемных соединений в элементах с инжекционным питанием ниже, чем в остальных сериях, что приводит к повышению надежности устройств. Схемы с инжекторным питанием могут нормально работать при изменении тока инжектора в пределах нескольких порядков, следовательно, допускают большие колебания напряжения питания.

На рисунке 4.10 изображен инжекторный транзистор, у которого можно выделить две транзисторные структуры, имеющие общие области. Первым транзистором является Р1-N1-P2, вторым – N1-P2-N2. Область Р1 является инжектором носителей (дырок) для области N1 (переход р1-n1 смещен в прямом направлении).

Рисунок 4.10 – Инжекторный транзистор

При подключении к инжектору плюсового полюса источника питания и подаче единичного логического уровня на «Б» транзистор оказывается в насыщенном состоянии. Уровень нуля составляет U0 0,02 В, уровень U1 0,4 В.

На рисунке 4.11 приведена в упрощенном виде принципиальная схема «ИЛИ-НЕ» структуры для И2Л. Отличительной особенностью базовых элементов И2Л является многоколлекторный транзистор (на рисунке коллекторы показаны пунктиром), используемый для улучшения развязки при подаче выходного сигнала на несколько входных каскадов (повышение коэффициента разветвления по выходу).

При нулевом Uвх1 ток транзистора Т1.1 не протекает в базу Т1.2, (входной ноль шунтирует р-n переход «база-эмиттер» транзистора Т1.2) закрывая и устанавливая его в единичное состояние. Подобно действует и второй инжекционный транзистор. Если на оба транзистора подано нулевое напряжение – на выходе будет протекать в нагрузку единичный инжекционный ток, в случае наличия на выходе хотя бы одного открытого транзистора (любого), он будет шунтировать второй, фиксируя сигнал нуля на выходе ЛЭ.

И2Л применяются в микропроцессорах, запоминающих устройствах с произвольной выборкой, в ЦАП и АЦП, в бытовых приборах (электронные часы, калькуляторы, электронные затворы для фотоаппаратов). Перспективно применение И2Л ИМС в устройствах и системах с автономных питанием.

Рисунок 4.11 – Базовый элемент «ИЛИ-НЕ» инжекционной логики

Цифровые ИМС на МОП структурах. В цифровой интегральной схемотехнике применение нашли полевые транзисторы с изолированным затвором. Как известно, подобные транзисторы делятся на два вида: с встроенным и индуцированным (наведенным) каналами (n-типа, р-типа). В отличие от биполярных транзисторов ток в канале полевого переносится основными носителями. В зависимости от напряжения, поданного на управляющий электрод (затвор) ток в канале можно легко изменить, а значит изменить и его сопротивление. Входной ток полевого транзистора практически равен нулю, т.е. он, как аналог электронной лампы, управляется напряжением.

Большинство выпускаемых в настоящее время цифровых интегральных схем (ЦИС) на МОП структурах базируется на транзисторах с индуцированным каналом.

UВЫХ

б

а

UВЫХ

Т2

а – с индуцированным каналом n-типа; б – на комплементарных транзисторах

Рисунок 4.12 – Базовый ЛЭ «ИЛИ-НЕ на МОП транзисторах

Пример реализации функции «ИЛИ-НЕ» на МОП транзисторах с n-каналом представлен на рисунке 4.12а. ЛЭ состоит из нагрузочного Т3 (активная нагрузка) и двух управляющих Т1 и Т2 транзисторов. Когда Т1 и Т2 закрыты (входной сигнал логического «0») на UВЫХ устанавливается высокий уровень. Если UВХ1 или UВХ2 имеют единицу на входе UВЫХ будет нулевым.

Для получения функции «И-НЕ» управляющие транзисторы включаются не параллельно, а последовательно по цепи исток-сток.

Для снижения мощности, потребляемой элементами в статическом режиме используются комплементарные МОП структуры, имеющие обозначение КМОП-логика.

На рисунке 4.12б представлена принципиальная схем базового КМОП-элемента с функцией «ИЛИ-НЕ».

При закрытых Т1 и Т2 транзисторах (низкий уровень входа) Т3 и Т4 открыты и на выходе ЛЭ присутствует логическая «1», если на Т1 или Т2 – «1», на истоке-затворе либо Т3, либо Т4 малое напряжение закрывает один или оба транзистора с установкой выходного сигнала в нулевой уровень.

Достоинствами КМОП –логики по отношению к ТТЛ являются:

- низкая потребляемая мощность в статическом режиме;

- очень высокое входное сопротивление;

- большая нагрузочная способность (коэффициент разветвления 50-100);

-большой диапазон напряжения питания (3-15 В);

- малая зависимость характеристик от температуры;

- технологичность в производстве.

В числе недостатков следует отметить повышенное выходное сопротивление и сравнительно низкий частотный диапазон (до 5 МГц).

Среди известных серий микросхем на КМОП структурах следует отметить К176 и более раннюю 564. Предельная частота сигнала для этих серий составляет 1 МГц. Напряжение питания - 8÷15В.

Более современной серией является К561, для которой предельная частота доходит до 5 МГц, а UП лежит в пределах 3-15 В, при этом выход ИМС К561 серии можно нагружать на ТТЛ логику (в определенном ограничении).

Логика на основе полупроводника из арсенида галлия (GaAs) в сравнении с кремниевыми структурами обладает более высоким быстродействием (в 3-6 раз), определяемым подвижностью электронов. Верхняя граница частоты ИМС на GaAs лежит в пределах 10 ГГц и более.

В таблице 4.1 приведены сравнительные параметры ЛЭ по основным своим характеристикам. «1» условно присвоена лучшему значению параметра, 7 – худшему [ 1 ].

При разработке цифрового устройства выбор типа ИМС зависит от того, какой параметр, из перечисленных в таблице, является определяющим, а чем можно поступиться. В последнем столбце сведена сумма условных оценок, минимум которой характеризует обобщенное относительное превосходство соответствующего типа микросхем. Первое второе и третье места занимают ЛЭ на полевых структурах.

Таблица 4.1 – Сравнительные характеристики ЛЭ

КОМБИНАЦИОННЫЕ ЦИФРОВЫЕ УСТРОЙСТВА

Цифровые устройства, построенные на основе элементарных (базовых) ЛЭ можно разделить на два класса: комбинационные и последовательностные.

Комбинационными называются устройства, если его выходные сигналы в каждый момент времени однозначно определяются входными сигналами в этот момент времени.

Все другие конструкции следует отнести к последовательностным устройствам. Данный тип устройств обязательно имеет память. Его выходная информация зависит не только от параметров входных сигналов в данный момент времени, но также от предыстории.

5.1 Шифраторы, дешифраторы, преобразователи кодов

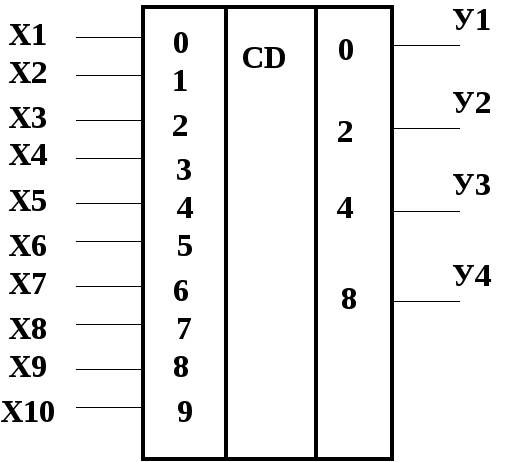

Шифратор (кодер)

– цифровой комбинационный элемент

преобразующий число из десятичной

системы счисления в двоичную. Входам

шифратора последовательно присваивается

значения десятичных чисел, поэтому

подача единичного логического сигнала

на соответствующий вход воспринимается

шифратором как подача определенного

десятичного числа. На выходе шифратора

устанавливается двоичный код. Число

выходов и входов шифратора связано

равенством:

,

где Х – число входных разрядов,Y

– выходных. Если количество входов

меньше, чем возможная информационная

емкость выходных, такой шифратор

называется неполным,

при

соответствии числа разрядов на входе

информационному пределу выходных

шифратор называется

полным.

Например, 10 разрядов на входе и 4 на

выходе образуют неполный шифратор.

Полным будет шифратор с числом входных

разрядов равным 16.

,

где Х – число входных разрядов,Y

– выходных. Если количество входов

меньше, чем возможная информационная

емкость выходных, такой шифратор

называется неполным,

при

соответствии числа разрядов на входе

информационному пределу выходных

шифратор называется

полным.

Например, 10 разрядов на входе и 4 на

выходе образуют неполный шифратор.

Полным будет шифратор с числом входных

разрядов равным 16.

Обозначение шифратора на принципиальных схемах представлено на рисунке 5.1.

Рисунок 5.1 – Неполный шифратор 10 х 4

По таблице соответствия (см. таблицу 5.1) легко проследить значение выходного сигнала при наличии единичного уровня на любом из входов шифратора (сигнал логической единицы в каждый момент времени подается только на один вход). На выходе У1 единица будет только тогда когда логическая единица будет присутствовать ИЛИ на входе Х1, ИЛИ Х3, ИЛИ Х5, ИЛИ Х7, ИЛИ Х9. В виде математической модели :

У1 = Х1+Х3+Х5+Х7+Х9,

У2 = Х2+Х3+Х6+Х7,

У3 = Х4+Х5+Х6+Х7,

У4 = Х8+Х9.

С учетом вышеприведенных соотношений можно устройство шифратора представить в виде совокупности элементарных ЛЭ «4 ИЛИ» (см. рисунок 5.2).

На практике находит применение шифратор с приоритетом. В таких шифраторах код двоичного числа соответствует наивысшему коду, присутствующему на входе, т.е. на входные разряды допускается одновременно подавать любое число «1», но он выставляет на выходе код числа соответствующего старшего разряда.

Таблица 5.1 – Таблица истинности для неполного шифратора 10 х 4

|

Десятичное число |

Двоичный код 8-4-2-1 | |||

|

У4 |

У3 |

У2 |

У1 | |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

Рисунок 5.2 – Шифратор 10 х 4 на ЛЭ «ИЛИ»

Практическое использование шифраторов – преобразование порядкового номера объекта (датчик, кнопка клавиатуры и т.д.) в двоичный код. При необходимости преобразовать большее десятичное число (наращивание входных разрядов) существуют шифраторы с дополнительными входами разрешения выборки. Например, микросхема К555ИВ1 (см. рисунок 5.3) представляет собой приоритетный полный шифратор 8 х 3 с восемью инверсными входами и тремя инверсными выходами. Кроме инверсного разряда выборки ЕI со стороны входов, со стороны выхода имеются разряды переполнения Е0 и признака наличия ненулевого входного кода G.

Рисунок 5.3– Приоритетный шифратор К555ИВ1

Дешифратором называется комбинационное устройство, предназначенное для преобразования входного двоичного кода в десятичный. По аналогии с шифраторами дешифраторы могут быть полными и неполными. В полном дешифраторе максимальное десятичное число равно пределу информационной емкости входных двоичных разрядов. В противном случае дешифратор называют неполным. Например, дешифратор 3 х 8 будет полным, но 4 х 10 – неполным.

В обозначении ЛЭ реализующего функцию дешифратора используют латинские буквы «DC». На рисунке 5.4 представлено обозначение на принципиальной схеме дешифратора К555ИД6. Он, имея четыре прямых входа и десять инверсных выходов, является неполным дешифратором.

На выходе У0 активный уровень (ноль) будет присутствовать в момент наличия нулевого уровня на всех входных разрядах, при этом на всех остальных выходных разрядах будет логическая единица. Появление единицы на любом входе приведет к появлению нуля на соответствующем двоичному коду десятичном выходе. Если на входе появится двоичный код превышающий цифру «9» (например, двоичный код «1101» – десятичный код «13»), во всех выходных разрядах будет «1».

Рисунок 5.4 – Вид дешифратора К555ИД6 на принципиальной схеме

Помимо информационных входов в дешифраторе может встраиваться вход разрешения считывания. Например, в ИМС К531ИД14 (см. рисунок 5.5 а), состоящей из двух полных дешифраторов 2 х 4, в каждом из которых имеется инверсный вход «Е», позволяющий дешифрировать входной сигнал только при разрешающем нулевом уровне. Если на входе «Е» находится логическая единица, независимо от состояния входных информационных разрядов на инверсных выходах будет присутствовать единица. Наличие входа разрешения позволяет наращивать размерность дешифратора. Например, из нескольких дешифраторов с размерностью 2 х 4 можно легко сформировать дешифратор 4 х 16 (см. рисунок 5.5 б).

Дешифраторы применяются в сложных цифровых устройствах для:

- преобразования двоичной информации (например, кода адреса внешнего блока, датчика и т.д., с которого необходимо получить данные или направить сигнал управления), формируемой вычислительным модулем (например, контроллером);

- преобразования кода (например, из двухразрядного в трехразрядный);

а

б

Рисунок 5.5 – Дешифратор К531ИД14 (а) и его схемотехнические возможности (б).

- мультиплексирования (объединения) и демультиплексирования (разветвления) цифровых сигналов.

Преобразователь кода – в общем случае, устройство, служащее для преобразования одного кода в другой (рассмотренные выше устройства дешифрации есть ни что иное, как преобразователи кода двоичного в десятичный). Функцию преобразования кода обозначают через Х / У.

Преобразователи кода широко применяют, например, в устройствах цифрового отображения информации, где в качестве элементов индикации используют семисегментные индикаторы (люминесцентные или светодиодные). На рисунке 5.6 представлен вариант принципиальной схемы вывода двоичного числа на светодиодный индикатор в виде десятичной цифры.

Кроме информационных двоичных разрядов преобразователь кода К176ИД2 содержит дополнительные входы управления. Вход «А» - разрешения индикации, нулевой уровень которого гасит индикаторы, единичный отображает входное двоичное число. Вход «М» - позволяет выбрать вид входной кодировки: в прямом или дополнительном коде представлена входная информация. Вход «К» - передает информацию с внутреннего накопительного регистра на выход, что позволяет избавиться от эффекта мелькания цифр при реализации индикации методом досчета: коротким единичным импульсом данные переписываются на выход микросхемы.

Рисунок 5.6 – Дешифратор К176ИД2 в роли преобразователя кода 4 / 7 для вывода информации на светодиодную матрицу с общими катодами

При построении преобразователя кода требуемой размерности первоначально формируют таблицу истинности. Для примера рассмотрим построение преобразователя 2 / 3. Соответствие кодов сведено в таблицу 5.2.

Таблица 5.2 – Таблица истинности преобразования кода 2 / 3

|

N п/п

|

Х1 |

Х2 |

У1 |

У2 |

У3 |

|

1 |

0 |

0 |

0 |

1 |

1 |

|

2 |

1 |

0 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

1 |

0 |

|

4 |

1 |

1 |

0 |

0 |

1 |

Устройство, реализующее условия таблицы истинности, представлено на рисунке 5.7. Для этих целей использован дешифратор К531ИД14 и три ЛЭ «3 ИЛИ».

5.2 Мультиплексоры, демультиплексоры.

Мультиплексор – комбинационное устройство, обеспечивающее передачу в требуемом порядке цифровой информации с нескольких входных разрядов на один выходной. Функцию мультиплексирования обозначают «MS» или «MUX». По своим функциональным особенностям мультиплексор аналогичен многоразрядному коммутатору-переключателю, который последовательно соединяет один из нескольких входов по заданному алгоритму с единственным выходным разрядом.

Рисунок 5.7 – Принципиальная схема преобразователя кода, соответствующая таблице истинности 5.2

Кроме информационных входных разрядов в мультиплексоре имеются адресные входы, предназначенные для выбора того входного разряда, информация которого передается на выход «F». По аналогии мультиплексор называется полным, если число входных разрядов соответствует максимальной емкости шины адреса, который, как правило, формируется в двоичном коде, в противном случае мультиплексор называют неполным. На рисунке 5.8 показана принципиальная схема коммутатора

Рисунок 5.8 – Принципиальная схема мультиплексора 21 на базовых ЛЭ «НЕ», «2-И» и «2-ИЛИ»

2 1, организующего передачу входной цифровой информации с двух входов (Х1 и Х2) на один выход (F). В обозначении типа микросхемы- мультиплексора используются буквы КП.

На рисунке 5.9 приводится изображение мультиплексора К155КП5 на принципиальных схемах.

Рисунок 5.9 – Мультиплексор К155КП5 формата 8 1

Мультиплексоры являются универсальными логическими устройствами, на основе которых создаются различные комбинационные и последовательностные схемы. Часто используют мультиплексоры для преобразования двоичного параллельного кода в последовательный. Для этого на информационные входные разряды подается информация, а посредством шины адреса, по очереди каждый разряд коммутируется на единственный выход. По такому принципу работают сдвигающие регистры, о которых речь пойдет несколько позже.

Все серии ИМС широкого применения имеют в своем составе мультиплексоры: К155КП1, К555КП17, К561КП3, К531КП18 и т.д.

Демультиплексором называется комбинационное устройство, предназначенное для передачи одного цифрового сигнала на один из нескольких выходов, согласно коду адресной шины. Демультиплексор противоположен по реализуемой функции, обозначаемой DMХ или DMS, мультиплексору.

Демультиплексор может быть полным, в случае равенства числа выходов, максимальной емкости адресной шины и неполным при меньшем числе выходов.

Реализация демультиплексора на основе базовых ЛЭ («ИЛИ» и дешифратора 2 х 4) представлена на рисунке 5.10.

Рисунок 5.9 – Функциональная схема демультиплексора формата 1 3

Работа демультиплексора очень схожа по функциональным особенностям с дешифратором. Поэтому в обозначении демультиплексоров используются те же буквы ИД. В описании названия ИМС в этом случае функции дешифратора и демультиплексора объединяют, например известны дешифратор-демультиплексор (дешифратор 4 х 16 или демультиплексор 1 16) К155ИД3, или К531ИД7(дешифратор 3 х 8 или демультиплексор 1 8), в которых для организации функции демультиплексирования в качестве адресных шин используют информационные разряды, а входной разряд – вход разрешения Е.

При использовании КМОП-технологии организация мультиплексирования-демультиплексирования становится возможной на основе двунаправленных ключей, управляемых адресными сигналами. При этом поток информации, передаваемой с входа на выход, может быть как цифровым, так и аналоговым. Благодаря такой возможности функции мультиплексора-демультиплексора реализуются одной ИМС, например, К561КП1.

Данная ИМС содержит два мультиплексора-демультиплексора 4↔1 в корпусе(см. рисунок 5.10), имеет общие адресные шины и один инверсный разряд выбора (Е). Соединение входа и выхода осуществляется на основе соответствующего разряда шины адреса и, обязательно, нулевого активного уровня на входе Е. Поскольку передача информации осуществляется через аналоговый ключ, при неактивном уровне на входе Е выходной разряд оказывается в особом состоянии, который носит название Z-состояние или высокоимпедансное состояние (третье состояние). Подобные ИМС входят в состав серий на основе КМОП структур: К561, К564, К590, К176, К591, К1564.

Рисунок 5.10 – Сдвоенный мультиплексор-демультиплексор К561КП1 формата 4 ↔ 1 со входом выборки микросхемы (Е).

5.4 Арифметико-логические устройства

Арифметико-логическим устройством (АЛУ) называется функционально законченный узел ЭВМ, предназначенный для реализации логических и арифметических операций с входной информацией. АЛУ является одним из основных узлов ЭВМ.

Анализ работы вычислительных машин показал, что 50% выполняемых ими операций – операции арифметического умножения, в то время как арифметическому сложению отводится 45%. Важность этих операций подтверждается тем, что при описании характеристик ЭВМ указывают продолжительность именно этих процессов.

Выполнение арифметических действий в ЭВМ осуществляется аппаратным и программным путем. В данном курсе рассматриваются только аппаратные способы.

Сумматоры, цифровые компараторы.

Сумматором называется комбинационное логическое устройство, предназначенное для выполнения операции арифметического сложения двоичных чисел. Сумматоры – один из основных блоков арифметико-логического устройства.

Чтобы понять принцип аппаратной реализации процесса арифметического сложения двух двоичных чисел рассмотрим таблицу истинности операции их сложения. Для простоты возьмем два одноразрядных числа А и В (см. рисунок 5.11).

Рисунок 5.11 – Принцип сложения двоичных чисел и таблица истинности.

Операция логического сложения двух одноразрядных чисел в двоичном коде характеризуется следующими правилами:

- ноль плюс единица = единица;

- единица плюс ноль = единица:

- ноль плюс ноль = ноль

- единица плюс единица = ноль плюс единица в разряде переполнения (переносится в следующий старший разряд).

Сказанное выше сведено в таблицу состояния (истинности), где за А и В обозначены логические переменные, S – разряд результата сложения и Р – разряд переполнения на выходе ЛЭ. Особенностью устройств логического сложения многоразрядных переменных является поразрядное выполнение сложения с формированием сигнала переноса (Р) для каждого разряда (см. рисунок 5.12).

При рассмотрении таблицы рисунка 5.11 столбец S есть, не что иное как реализация логической функции «ИСКЛЮЧАЮЩЕЕ ИЛИ» , а столбец Р – результат умножения переменных, т.е. S = A B, Р = АВ.

Рисунок 5.12 – Принципиальная схема одноразрядного полусумматора

Устройство, выполняющее таблицу истинности (см. рисунок 5.11), называемое полусумматором, изображено на рисунке 5.12. Полусумматор, как устройство, имеющее только два входа, может использоваться для сложения лишь младших разрядов.

Суммирование двух многоразрядных двоичных чисел производится поразрядно с применением дополнительного входа, куда подается выходной сигнал от разряда переполнения суммирования в предыдущем разряде. Функциональная схема такого устройства приведена на рисунке 5.13 на основе уже рассмотренного полусумматора и ЛЭ «ИЛИ».

Рисунок 5.13 – Принципиальная схема одноразрядного сумматора

Для того, чтобы суммировать аппаратно два многоразрядных числа, необходимо обвязать полные сумматоры и один полусумматор (для младшего разряда). Пример выполнения суммирования двух трехразрядных чисел с применением вышеперечисленных средств представлен на рисунке 5.14.

Рисунок 5.14 – Принципиальная схема трехразрядного сумматора

В интегральном исполнении выпускают одноразрядные, двухразрядные и четырехразрядные двоичные сумматоры. Примером четырехразрядного сумматора является ИМС К155ИМ3 (см. рисунок 5.15). Функция суммирования обозначается SM

Рисунок 5.15 – Четырехразрядный двоичный сумматор К155ИМ3

При наращивании разрядности суммируемых чисел сумматоры соединяются последовательно. При этом выходные разряды переноса соединяют с Р0 сумматора более высоких разрядов.

На вход Р0 первого в иерархии сумматоров подают уровень нуля (соединяют с общим проводом).

Рассмотренные сумматоры могут легко применяться для построения схем вычитания двоичных чисел. Операция вычитания заменяется операцией сложения, путем представления вычитаемого в дополнительном коде:

Рассмотрим, например процедуру вычитания: А = 12, В = 7. Двоичный код числа А (12) – 1100, числа В (7) – 0111. Дополнительный код числа ВДОП (9) – 1001, ВОБР – 1000.

Следовательно, разность А – В будет равна:

1100 – 0111 = 1100 + 1001 = 1100 + 1000 + 1 = 0101(1) (десятичное число 5, (1) – говорит о наличии единицы, переносимой в пятый старший разряд).

В данном примере сложение двух единиц старшего разряда дает единицу в разряде переполнения – это говорит только о том, что число А больше чем В, т.е. результат вычитания есть положительное число. В случае, когда в разряде переполнения результата замены вычитания сложением остается ноль – число В больше А и перед разностью ставится знак минус, но при этом число результата выражено в дополнительном коде. Например, пусть А = 6, а В = 24.

А – В = 00110 – 11000 = 00110 + 00111 + 1 = 01110(0) (дополнительный код десятичного числа – 18). Процедура восстановления прямого кода по обратному достаточно проста: дополнительное число рассматривают с младшего разряда, все нули и первую встретившуюся единицу переписывают, остальное инвертируют. В последнем примере прямой код результата вычисления разности получается из дополнительного: 01110(0) 10010 и знак минус перед разностью (-18). Второй способ получения прямого кода из дополнительного – двоичное число, выраженное дополнительным кодом инвертируют и прибавляют к нему единицу: 01110 10001 + 1 = 10010 (-18).

Реализация вычитания двух 4-х разрядных чисел на сумматоре К155ИМ3 представлена на рисунке 5.16.

На входы А подается код уменьшаемого, В – вычитаемого. С разряда переполнения Р4 единица поступает на вход Р0 (прибавляется единица в преобразовании прямого кода числа В в дополнительный код). Посредством инверторов на входах В на входы сумматора поступают инверсные сигналы (для преобразования прямого кода числа В в дополнительный код).

Таким образом, если на выходе Р4 появляется единица – число А больше чем В и на выходах сумматора код разницы представлен прямым кодом. В случае наличия нуля на выходе переполнения - число А меньше числа В, а код результата является дополнительным.

Рисунок 5.16 – Четырехразрядный двоичный сумматор-вычитатель (для А > В) на основе К155ИМ3

Рассмотренные сумматоры применяют и для аппаратного умножения двоичных чисел, хотя раньше традиционно эти операции выполнялись программно. Применение специализированных ИМС позволило значительно увеличить быстродействие.

На рисунке 5.17 представлена блок-схема реализации арифметического умножения двух двухразрядных чисел А и В с использованием одноразрядных сумматоров.

Рисунок 5.17 – Блок схема умножения двух двухразрядных чисел

Процедура умножения является стандартной, какой пользуются повсеместно – умножение столбиком. Операция проводится поразрядно. Формируются парные произведения, которые с учетом веса перемножаемых разрядов складываются. В результате получается новое число.

Структурная схема устройства приводится на рисунке 5.18.

Рисунок 5.18 – Структурная схема умножителя двухразрядных чисел.

Цифровые компараторы

Цифровые компараторы предназначены для сравнения двух чисел выраженных в двоичном коде. Сравнение производится для двух двоичных чисел с одинаковым числом разрядов. Выходной сигнал компаратора содержит три информационных разряда: разряд равенства двух чисел (например, А = В) и два разряда неравенства (А > В, А < В, см. рисунок 5.19).

Рисунок 5.19 – Цифровой одноразрядный компаратор на базовых логических элементах

Цифровой одноразрядный компаратор представляет собой логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ» с дополнительными информационными выходами.

В обозначении функции сравнения используется двойной знак равенства « = = ».

Промышленностью цифровые компараторы выпускаются в виде самостоятельных микросхем, например К561ИП2 – четырехразрядный компаратор (см. рисунок 5.20).

Рисунок 5.20 – Четырех разрядный компаратор К561ИП2

При необходимости наращивания разрядов сравниваемых двоичных чисел компараторы включают каскадно, при этом выходные разряды предыдущего компаратора (сравнение младших разрядов) подают на соответствующие входы последующего (сравнение старших разрядов). Вариант включения двухразрядного компаратора для сравнения четырехразрядных кодов представлен на рисунке 5.21.

Рисунок 5.21 – Двух разрядный компаратор в каскадном включении

ПОСЛЕДОВАТЕЛЬНОСТНЫЕ УСТРОЙСТВА

Особенностью последовательностных логических устройств является зависимость выходного сигнала не только от значения действующих в настоящий момент на входе логических переменных, но и от тех значений переменных, которые действовали на входе в предыдущие моменты времени, т.е. для последовательностного устройства существенное значение имеет предыстория состояния входных информационных переменных. Следовательно, в подобных элементах должна существовать ячейка памяти, хранящая значение переменных в предыдущие моменты времени. Данную функцию во всех цифровых схемах выполняют триггерные устройства или триггеры

Триггеры

Триггерами называют большой класс электронных устройств, обладающих способностью длительно находится в одном из двух (трех) устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко расшифровывается по значению выходного напряжения. По принципу работы триггеры относятся к импульсным элементам.

Слово «триггер» в переводе с английского означает спусковое устройство, курок. В технической литературе на английском языке термин «trigger» обычно применяют в значении глагола «запускать».

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера понимается способность оставаться в одном из двух устойчивых состояний и после прекращения действия переключающего сигнала. С учетом представления информации в виде нулей и единиц можно констатировать, что триггер помнит (хранит) один разряд числа, записанного в двоичном коде. Первые триггерные схемы на электронных лампах (катодные реле) были описаны в 1918 году М.А. Бонч-Бруевичем.

Классификация триггеров. По способу представления информации триггеры делятся на статические и динамические.

Динамические триггеры представляют систему, одно из состояний которой (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определенной частоты, а другое – отсутствием выходных импульсов (нулевое). Смена состояний производится внешними импульсами управления. Динамические триггеры имеют ограниченное использование и в данном курсе не рассматриваются.

Статические триггеры характеризуются выходным состоянием с неизменным уровнем напряжения: высоким – близким к напряжению питания и низким – около нуля. Статические триггеры часто называют потенциальными.

Статические триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы – симметричные и несимметричные. Название определяется внутренней структурой устройства.

Симметричные триггеры имеют симметрию схемы двухкаскадного усилителя с положительной обратной связью, а также идентичность характеристик параметров симметричных элементов и связей между ними. В несимметричных триггерах симметрии плеч нет.

Основную массу триггерных устройств составляют симметричные триггеры.

Особенностью всех

триггеров является наличие двух выходов:

прямого

и инверсного

и инверсного ,

связанных функциональным единством,

т.е. при наличии единицы на

,

связанных функциональным единством,

т.е. при наличии единицы на -выходе

потенциал

-выходе

потенциал будет нулевым и наоборот.

будет нулевым и наоборот.

По способу приема информации различают асинхронные и синхронные триггеры (см. рисунок 6.1).

Асинхронные триггеры изменяют свое состояние непосредственно в момент появления соответствующего входного информационного сигнала.

Синхронные триггеры изменяют свое состояние в строго определенные (тактовые) моменты времени, соответствующие действию активного сигнала на специализированном входе, который называется тактовый или синхронизирующий «С».

Рисунок 6.1 – Классификация триггеров по способу ввода информации

По способу управления синхронные триггеры подразделяются на статические, управляемые постоянным уровнем на входе синхронизации и динамические – их управление осуществляется перепадом напряжения (фронтом).

Входные управляющие сигналы могут быть прямыми и инверсными.

Кроме того, синхронизируемые триггеры делятся на однотактные и двухтактные. В однотактных триггерах информация передается на выход за один такт, в двухактных – за два. Однотактные триггеры в обозначении функции имеют «Т», двухтактные – «ТТ».

По функциональным особенностям триггеры подразделяют на следующие классы:

- с раздельной установкой состояния 0 и 1 (RS – триггеры);

- универсальные (JK – триггеры);

- с памятью (D _триггеры);

- со счетным входом (Т – триггеры).

Входы управления триггерами обозначают:

R – вход установки в нулевое состояние;

S – вход установки в единичное состояние;

J – вход установки в состояние «1» в универсальном JK- триггере

K - вход установки в состояние «0» в универсальном триггере

Т – счетный (общий) вход;

D – информационный вход установки в состояние «1» или «0»;

V – дополнительный управляющий вход для разрешения приема информации (вход выборки);

С – вход синхронизации (тактовый вход).

Асинхронный RS – триггер – простейшее устройство, представляющее собой бистабильную ячейку памяти. Относится к симметричным триггерам. Асинхронные RS - триггеры применяются в качестве самостоятельных устройств, а также входят в состав других, более сложных триггеров в качестве ячеек памяти. На рисунке 6.2 изображен простейший RS – триггер и его таблица истинности.

Рисунок 6.2 – Асинхронный RS – триггер и таблица истинности его состояния

Согласно таблице в единичное состояние триггер переключается при единице на входе S, а в нулевое – при единице на входе R. Наличие единичных уровней на обоих информационных входах дает неопределенное состояние выхода и в эксплуатационных режима не предусматривается.

RS – триггер – устройство с раздельными входами управления, функцию которого можно легко реализовать двумя элементами «ИЛИ – НЕ» (прямое управление) или двумя элементами «И – НЕ» (инверсное управление) (см. рисунок 6.3).

а

б

а - прямое управление; б – инверсное управление;

Рисунок 6.3 – Асинхронный RS – триггер и таблица истинности его состояния

а - прямое управление; б – инверсное управление;

Рисунок 7.3 – Асинхронный RS – триггер и таблица истинности его состояния

В интегральном исполнении практически все серии широкого применения включают в свой состав асинхронные RS – триггеры (например, 4 асинхронных триггера с прямым управлением имеет ИМС К564ТР2, см. рисунок 6.4).

Рисунок 6.4 – Счетверенный асинхронный RS – триггер К564ТР2 с входом выборки

Кроме информационных входов R и S данная ИМС снабжена общим вспомогательным входом выборки V, при наличии нуля на котором микросхема переходит в высокоимпедансное (третье) состояние.

Синхронные (тактируемые) RS – триггеры получают из асинхронных путем подключения к его входам схем управления на базовых ЛЭ (см. рисунок 6.5).

Рисунок 6.5– Тактируемый RS – триггер со статическим управлением

Информационные сигналы по входам R и S воспринимаются триггером только при наличии единичного уровня на тактовом входе «С». Так работают синхронные триггеры со статическим управлением. Во время действия высокого уровня на входе «С» этот триггер функционирует как обычный асинхронный, поэтому смена информационных сигналов должна производится в момент паузы тактового импульса, иначе возникнут нарушения в работе устройства.

В динамических синхронных триггерах информация на входах R и S может обновляться и в период действия импульса синхронизации и в моменты паузы. Такой порядок работы стал возможен благодаря использованию в схемном решении вместо двух элементов совпадения на входе (см. рисунок 6.5) четырех RS – триггеров.

Работа триггера с динамическим управлением основана на эффекте переключения соответствующим фронтом импульса синхронизации. Например, триггер на рисунке 6.6 управляется отрицательным перепадом (из единицы в ноль) тактового импульса, а переключение по информационным R и S входам осуществляется единичными уровнями сигналов.

На принципиальных схемах триггеры с динамическим управлением обозначают с помощью стрелки-треугольника входа тактирования, при этом стрелка, обращенная внутрь триггера, говорит о прямом управлении (положительным фронтом импульса синхронизации), наружу – инверсное управление (см. рисунок 6.7).

Рисунок 6.6– Синхронный RS – триггер с динамическим инверсным управлением

Рисунок 6.6– Изображение синхронного RS – триггера с динамическим инверсным управлением на принципиальных схемах

Шестиэлементные триггерные системы широко используются для организации триггеров других типов, например D – триггеров, JK – триггеров, Т – триггеров.

JK – триггеры для всех входных комбинаций, кроме одной (Jn=1, Kn=1), функционируют подобно RS – триггеру, при этом вход «J» играет роль входа S, а «K» - входа R. Входная комбинация Jn = Kn = 1 приводит к опрокидыванию триггера и смене выходных сигналов на противоположные по приходу каждого тактового импульса.

JK – триггеры выпускаются только тактируемыми (см. рисунок 6.7). Как правило, устойчивая работа данных триггеров обеспечивается их двухступенчатой структурой (по положительному фронту тактового импульса информация передается на выход первого триггера, по отрицательному – на выход второго).

Рисунок 6.7– Изображение JK – триггера с прямым динамическим управлением на принципиальных схемах (К561ТВ1)

Таблица истинности состояния JK – триггера приведена в таблице 6.1.

Таблица 6.1 Таблица состояния JK – триггера (К561ТВ1) для динамического управления по входам J и K

Асинхронная установка триггера в нулевое и единичное состояние осуществляется входам R и S независимо от состояния уровней на J и K входах.

D – триггеры в отличии от рассмотренных выше имеют для установки в состояние 0 и 1 один информационный вход D.

Применение находят D – триггеры в асинхронном и синхронном исполнении.

Асинхронные D – триггеры обеспечивают передачу сигнала с входа D на выход, не обладая при этом свойством памяти (см. рисунок 6.8).

Рисунок 6.8– Структурная схема асинхронного D - триггера

Подобные схемные решения используются для формирования импульсных сигналов с крутыми фронтами (см.рисунок 6.9).

Рисунок 6.9– Форма сигналов на входе D и выходе Q формирователя

импульсов на основе асинхронного D - триггера

В практических целях асинхронные D – триггеры, как элементы памяти не используют и в этом ключе их относят к D – триггерам достаточно условно.

Хранения информации у D – триггеров обеспечивается за счет цепей синхронизации и, поэтому, все D – триггеры – тактируемые. Управление по входу синхронизации может быть статическим, динамическим и двухступенчатым. Для примера на рисунке 6.10 приведены ИМС реализующие функцию статического и динамического D – триггера.

а

б

а – статический D – триггер (К155ТМ7); б – динамический D – триггер (К561ТМ2)

Рисунок 6.10 – Синхронные D - триггеры

Т – триггеры – последовательностные устройства, изменяющие свое логическое состояние на противоположное по каждому активному сигналу на входе «Т».

В сериях ИМС широкого применения Т – триггеры как таковые не используют, однако функционально Т – триггер находит применение как счетное устройство. Его легко получить из синхронного RS – триггера и D – триггера (см. рисунок 6.11).

Двухступенчатый Т – триггер строится на двух синхронных RS – триггерах (см. рисунок 6.12).

Т – триггер также легко получить из универсального JK – триггера. Для этого необходимо информационные входы J и K объединить вместе и использовать их, как вход разрешения, при этом счетные импульсы подаются на вход синхронизации «С», выполняющего в данном случае функцию счетного входа «Т» (см. таблицу 6.1).

а

б

а – Т – триггер на базе синхронного RS – триггера, б - Т – триггер на базе D – триггера

Рисунок 6.11 – Счетный Т - триггер

б

а

а – Т – триггер на базе синхронного RS – триггера, б – изображение двухступенчатого Т – триггера на принципиальных схемах

Рисунок 6.12 – Двухступенчатый счетный Т - триггер

DV и TV – триггеры представляют собой модификацию соответственно D и T – триггеров. Дополнительный вход V используется как разрешающий – запрещающий. Наличие входа V расширяет функциональные возможности D и T - триггеров. На рисунке 6.13 приводятся функциональные схемы DV и TV – триггеров.

а

б

а – DV – триггер на базе синхронного D – триггера, б - TV – триггер на базе JK - триггера

Рисунок 6.13 – DV и TV – триггеры

Несимметричные триггеры Шмитта. Основу несимметричных триггеров, как и симметричных, составляет двухкаскадный усилитель, охваченный положительной обратной связью. Эти триггеры обладают двумя устойчивыми состояниями, смена которых происходит скачкообразно под действием входных сигналов. Для триггеров такого типа в отличии от симметричных характерны не идентичность обеих каскадов и видов связи между ними.

По функциональным характеристикам несимметричные триггеры ближе к импульсным устройствам, чем к цифровым.

Несимметричные триггеры входят в состав некоторых серий широкого применения, например К155ТЛ2 (шесть триггеров в одном корпусе), но чаще всего собираются из отдельных дискретных элементов.

На рисунке 6.14 приведена базовая схема транзисторного несимметричного триггера с эмиттерной связью. Этот вид триггера был впервые описан в 1938 году О. Г. Шмиттом, отчего его второго название – триггер Шмитта.

Согласно приведенной схеме транзистор VT1 при малом входном сигнале находится в закрытом состоянии, а VT2 – в открытом (выходным уровнем коллекторного напряжения первого каскада). При открытии первого транзистора, за счет закрытия второго каскада и резистора RЭ , играющего роль элемента положительной обратной связи опрокидывание триггера происходить лавинообразно. В первоначальное состояние триггер возвращается обратным путем.

а

б

а – принципиальная схема триггера Шмитта, б – временные диаграммы работы триггера Шмита

Рисунок 6.14 – Несимметричный триггер Шмитта

Счетчики импульсов

Счетчиком называется последовательностное устройство, предназначенное для счета входных импульсов и фиксации их числа в соответствующем коде. Основной параметр счетчика – модуль счета. Это максимальное число единичных сигналов, которое может быть сосчитано счетчиком. В обозначении счетчика применяют буквы «СТ» (от англ. counter).

Счетчики классифицируют:

По модулю счета:

- двоично-десятичные;

- двоичные;

- с произвольным постоянным модулем счета;

- с переменным модулем счета.

По направлению счета:

- суммирующие;

- вычитающие;

- реверсивные.

По способу внутренних связей (тип структурной схемы):

- с последовательным переносом;

- с параллельным переносом;

- с комбинированным переносом;

- кольцевые.

На рисунке 6.15 представлен счетчик импульсов, построенный на основе трех JK –триггеров, включенных каждый по схеме счетного Т – триггера.

Рисунок 6.15 – Счетчик импульсов

Временные диаграммы работы данного трехразрядного двоичного счетчика приведены на рисунке 6.16.

t

t

t

Рисунок 6.16 – Временные диаграммы работы трехразрядного суммирующего счетчика

Микросхема К155ИЕ5 является суммирующим счетчиком с последовательным переносом (см. рисунок 6.17).

2

2

3

Рисунок 6.17 - Структура микросхемы К155ИЕ5 и ее графическое

изображение

Для наращивания разрядности счетчиков их соединение в каскад осуществляют путем подачи сигнала старшего разряда предыдущей ИМС на счетный «Т» вход следующей (см. рисунок 6.18).

Рисунок 6.18 - Каскадное включение счетчиков для наращивания

разрядности

Вычитающий счетчик с последовательным переносом строится на основе тех же счетных триггеров (см. рисунок 6.19) с той лишь разницей, что передача информации от триггера к триггеру производится с применением инверсных выходов, а выходными разрядами являются выходы прямые.

На рисунке 6.20 изображена временная диаграмма состояний выходных разрядов вычитающего счетчика при подаче на вход «Т» цифрового сигнала в виде меандра.

Рисунок 6.19 - Функциональная схема вычитающего трехразрядного

счетчика

Если принять состояние выходных разрядов Q0 = Q1 = Q2 = 1 (соответствует десятичному числу 7), каждый последующий спад импульса на входе «Т» будет уменьшать итоговое значение выходного двоичного числа.

Рисунок 6.20 - Временная диаграмма работы вычитающего счетчика

Кроме счетчиков с последовательным переносом (импульсы с выхода одного счетного триггера поступают на вход следующего) существуют счетчики с параллельным переносом. Для этого переносимый со входа на выход двоичный код необходимо первоначально сформировать и только затем осуществить перенос по сигналу синхронизации.

Счетчики с параллельным переносом комплектуются дополнительными комбинационными ЛЭ, позволяющими реализовать данную функцию. Счетчики с параллельным переносом экономят время преобразования (счета).

На рисунке 6.21 приведены ИМС комбинированного типа. Структура последовательного счета реализуется подачей на входы суммирования «+1» (вход «-1» = 0) или вычитания «-1» (вход «+1» = 0) счетных импульсов. Для параллельного счета на входы D1-D8 предварительно необходимо подать соответствующий двоичный код, который по инверсному уровню входа «С» переносится на выходные разряды.

Рисунок 6.21 - Реверсивные счетчики с комбинированным переносом

Во всех предыдущих примерах информация на выходе счетчиков представляется в двоичном коде. Однако, в некоторых случаях требуется получить на выходных разрядах десятичный код, т.е. чтобы каждому счетному импульсу на входе соответствовал бы импульс на определенном выходе устройства (десятичный код). Реализация подобной задачи, в принципе уже рассматривалась, для этого необходимо выходные разряды двоичного счетчика подать на дешифратор. Но гораздо проще эта задача решается при использовании кольцевого счетчика (см. рисунок 8.8).

Временные диаграммы, поясняющие работу кольцевого счетчика, приведены на рисунке 8.9. Название счетчика определяется кольцом информации, подаваемой с выхода последнего счетного триггера на соответствующий вход устройства.

Рисунок 8.8 - Кольцевой счетчик

Рисунок 8.9 - Временные диаграммы работы кольцевого счетчика