9. Регистры

Регистром называется последовательностное логическое устройство, предназначенное для записи, хранения и (или) сдвига информации, представленной в виде многоразрядного двоичного кода.

Регистр состоит из упорядоченной последовательности триггеров (как правило, D-триггеры), число которых равно числу разрядов входного (выходного) двоичного кода. В состав каждого регистра кроме триггеров входят комбинационные устройства, посредством которых обеспечивается выполнение операций над входными словами.

Регистр может выполнять следующие операции:

- установка в исходное состояние (запись нулевого кода);

- запись входной информации в последовательной форме;

- запись входной информации в параллельной форме;

- хранение информации;

- сдвиг хранимой информации вправо или влево;

- выдача хранимой информации в последовательной форме;

- выдача хранимой информации в параллельной форме.

Все регистры можно разделить на накопительные (регистры памяти, хранения) и сдвигающие (см. рисунок 9.1). Сдвигающие, в свою очередь, по способу ввода информации делятся на:

- параллельные;

- последовательные;

- комбинированные.

По направлению передачи информации сдвигающие регистры могут быть однонаправленными и реверсивными.

Рисунок 9.1 - Классификация регистров

На рисунке 9.2 приведена функциональная схема накопительного регистра с параллельным вводом и выводом информации. Основой

Рисунок 9.2 - Накопительный регистр с параллельным вводом и выводом информации

регистра являются D – триггеры, которые на своих прямых выходах повторяют значения сигналов на информационных входах X1-X4 при Y1=1 (параллельная запись). Сигналы с выходов триггеров попадают на выход устройства при наличии «1» на управляющем входе «Y2» (параллельное считывание).

На принципиальных схемах регистры обозначают «RG». Практически все серии ИМС имеют в своем составе регистры. Примером может служить четырехразрядный параллельный регистр памяти К155ИР15 (см. рисунок 9.3).

Рисунок 9.3 - Четырехразрядный параллельный регистр памяти с тремя выходными состояниями

При Е1 = Е2 = 0 (активное состояние) осуществляется параллельная запись информации со входов D1 - D8 по положительному фронту сигнала синхронизации «С» (см. таблицу 9.1).

Хранение информации осуществляется при смене активного уровня входов Е1, Е2 с 0 на 1.

Таблица 9.1 - Таблица состояния четырехразрядного параллельного регистра для Ez1 = Ez2 = 0

* - любое значение (0 или 1).

Обнуление регистра производится единичным импульсом по входу R. При единичном уровне на любом из входов Еz1, Ez2 выходные разряды Q1-Q4 регистра переходят в третье высокоимпедансное состояние.

На рисунке 9.4 представлена функциональная схема четырехразрядного сдвигающего регистра.

Рисунок 9.4 - Четырехразрядный сдвигающий регистр

Рисунок 9.4 - Четырехразрядный сдвигающий регистр

Импульсный сигнал «1» с входного Хi разряда по положительному фронту тактового импульса последовательно переписываются в Q1, затем в Q2, … Q4.

Таблица 9.2 - Таблица состояния четырехразрядного сдвигающего регистра

|

№ такта |

Данные |

Q1 |

Q2 |

Q3 |

Q4 |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

|

2 |

0 |

0 |

1 |

0 |

0 |

|

3 |

0 |

0 |

0 |

1 |

0 |

|

4 |

0 |

0 |

0 |

0 |

1 |

Сдвиг двоичного числа осуществляется от младшего разряда к старшему. С учетом правильности записи двоичного числа (младший разряд справа, старший слева) подобный сдвиг называют «сдвиг влево». При сдвиге вправо информация на выходе регистра должна последовательно перемещаться от старшего разряда к младшему.

В сериях широкого применения предлагаются регистры универсального (комбинированного) типа, в которых совмещены функции параллельного ввода-вывода и последовательного реверсивного сдвига. Примером может служить сдвигающий регистр К155ИР13 (см. рисунок 9.5).

Рисунок 9.5 – Восьмиразрядный комбинированный реверсивный сдвигающий регистр К155ИР13

Микросхема имеет информационные входы:

- D1-D8 – разряды параллельного ввода информации;

- DR, DL – входы ввода последовательной информации (DR – сдвиг вправо, DL – сдвиг влево);

- S1, S0 – входы выбора режима работы ИМС;

- С – динамический вход синхронизации;

- R – вход обнуления выходных разрядов (Q1 - Q8) регистра.

Обнуление выходных разрядов регистра осуществляется инверсным сигналом, подаваемым на R.

При S1 = 0, S0 = 1 осуществляется последовательный ввод (сдвиг) информации со входа DR в младший разряд регистра со сдвигом влево.

При S1 = 1, S0 = 0 осуществляется последовательный ввод информации со входа DL в Q8 (старший) разряд регистра со сдвигом вправо.

При S1 = 1, S0 = 1 может быть проведена параллельная запись информации со входов D1-D8 при положительном перепаде на входе синхронизации С.

При S1 = 0, S0 = 0 – реализуется режим хранения информации.

ЦИФРОВЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА

Для кратковременного хранения небольших объемов цифровых слов (информация, выраженная определенным числом разрядов, содержащих нули и единицы) используют регистры. При необходимости длительного хранения или хранения больших массивов цифровой информации применения нашли запоминающие устройства (ЗУ), которые являются специализированными ИМС и входят в состав практически всех серий интегральных схем. Наличие функциональных ЗУ позволяет упростить организацию аппаратной части и методики доступа к информации.

ЗУ называют устройства, предназначенные, в общем случае, для записи, хранения и считывания информации, представленной многоразрядным цифровым кодом. На рисунке 10.1 представлена классификация ЗУ по назначению, способу адресации и технологии изготовления.

Рисунок 10.1 – Классификация ЗУ

По назначению все ЗУ можно разделить на оперативно-запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ).

ОЗУ служит для записи, хранения и быстрого доступа к информации в процессе ее обработки, при этом является энергозависимым, что влечет за собой обнуление всей хранимых цифровых слов в случае потери напряжения питания ЗУ.

ПЗУ предназначены для хранения и считывания большого объема цифровых данных. Режим записи для ПЗУ является вспомогательным и часто отделен аппаратно, методически и во временном интервале от процесса считывания.

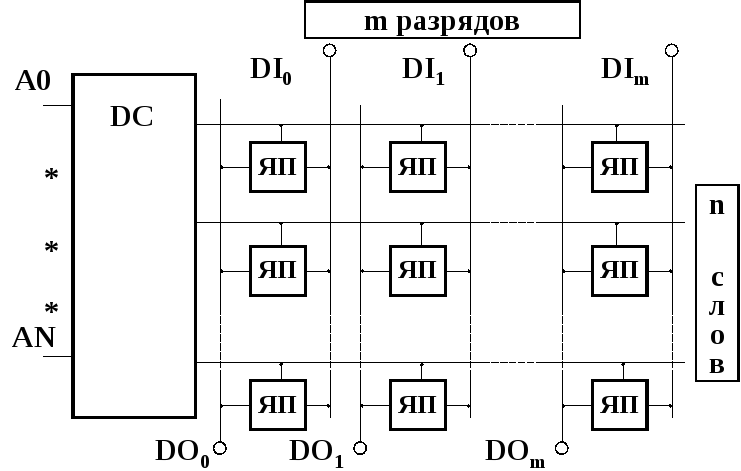

По способу адресации ЗУ делятся на одномерные и двухмерные. Структура ЗУ с одномерной адресацией представляет собой матрицу ячеек памяти (ЯП), связанных с устройствами ввода-вывода и управления в форме строк, число которых соответствует числу хранимых слов, а число столбцов – их разрядности. С помощью дешифратора адреса (устройство управления выборкой-записью информации) хранимые данные выбранной строки поступают на выход.

Одномерная адресация при большом объеме памяти требует дешифраторов с огромным числом выходных разрядов, например, для организации ЗУ 512 х 4 необходим дешифратор с 8 входными двоичными и 512 – ю десятичными разрядами, что не всегда технологично. Кроме того, при одномерной адресации доступ осуществляется ко всей строке (цифровому слову) целиком, при этом поэлементный опрос и запись невозможны.

С другой стороны одномерная адресация снижает время записи-считывания информации, что в ряде случаев является неоспоримым достоинством.

Для доступа к каждой ячейке памяти используют двухмерную адресацию – дешифратор адреса строки и дешифратор адреса столбца.

Технология изготовления ЗУ подобна общей технологии производства ИМС. ЗУ делятся на биполярные (ТТЛ, ТТЛШ, ЭСЛ, И2Л) и полевые (n-МОП, КМОП) структуры с соответствующими плюсами и минусами.

К основным параметрам ЗУ можно отнести информационную емкость, потребляемую мощность, время хранения и быстродействие.

Информационная емкость N определяется выражением N = n m, где n - число хранимых цифровых слов, m – число разрядов в слове. Емкость измеряется в битах. Емкость восьмиразрядного слова имеет особую единицу – байт. Емкость ЗУ составляет от нескольких десятков до нескольких миллионов бит.

Потребляемая мощность – мощность, которую ЗУ отбирает от источника энергии в установившемся режиме работы.

Время хранения информации – временной отрезок, в пределах которого ЗУ сохраняет информацию в заранее оговоренном режиме.

Быстродействие – интервал времени между моментом подачи команды записи-считывания и моментом ее реализации.

Оперативно запоминающие устройства

К оперативным запоминающим устройствам (ОЗУ, random access memory) относят ЗУ использующиеся для хранения информации, получаемой в процессе работы цифрового устройства и обеспечивающие соизмеримые времена ее считывания и записи.

Как и все ЗУ ОЗУ подразделяются на устройства с одномерной и двухмерной адресацией. Кроме того ОЗУ могут быть статическими и динамическими (см. рисунок 10.2).

Рисунок 10.2 – Классификация ОЗУ

В статических ОЗУ записанная информация постоянно хранится в выделенном для нее месте и не разрушается при считывании. Разрушение информации возможно при ее принудительном удалении, перезаписи или отключении напряжения источника питания. На сегодняшний день статические ОЗУ выполняют на биполярных и полевых транзисторах. ОЗУ на биполярных структурах являются самыми быстродействующими, но имеют более высокую потребляемую мощность и менее технологичны по сравнению с полевыми.

В динамических ОЗУ информация постоянно циркулирует в массиве, отведенном для ее хранения. Процесс считывания сопровождается разрушением информации, поэтому требует перезаписи считываемых данных. Информация в динамических ОЗУ хранится в виде заряда на конденсаторе.

Основным требованием, предъявляемым к ОЗУ, является обеспечение максимально возможного быстродействия при заданных объеме и организации.

Для обозначения функции ОЗУ на принципиальных схемах используют латинскую аббревиатуру «RAM».

10.2 ОЗУ с одномерной адресацией

В качестве примера ОЗУ с одномерной адресацией на рисунке 10.3 приведена функциональная схема устройства с организацией N = n m. Адрес выбираемой строки дешифрируется дешифратором DC, при этом информация, хранимая во всех ячейках памяти (ЯП) соответствующей строки выводится на выходные разряды DO0 - DOm . Данная структура называется структурой 2D и основным недостатком ее является значительное увеличение выходов DC при наращивании объемов памяти.

Так для ЗУ с размерностью 4 х 4 требуется дешифратор с четырьмя выходами, но для ЗУ с организацией 256 х 4 требуется комбинационное устройство с 256 выходами, что значительно усложняет аппаратную реализацию.

Рисунок 10.3 – ОЗУ с одномерной организацией шины доступа к информации

В определенной мере избежать этого можно, при использовании матрицы, длина строки которой многократно превышает разрядность хранимых слов. Это уменьшает число выбираемых строк, а, следовательно, и уменьшает число выходов дешифратора. Из выбранной строки матрицы, выбирается ее часть, соответствующая тому или иному слову.

Структура такого ЗУ, приведенная на рисунке 10.4, помимо дешифратора строки дополнительно содержит мультиплексоры (индекс М в обозначении) для выбора разрядов слова.

В этом случае адресный код для выбора информации делится на две части. Первая часть характеризует номер строки, вторая – номер столбца коммутируемого соответствующим мультиплексором. Так для ЗУ с объемом 256 х 4 структура 2DM будет содержать матрицу 32 х 32, для доступа к строке которой нужно 5 двоичных разрядов. Еще 3 разряда необходимы, чтобы передать один из восьми разрядов приходящих на четыре мультиплексора.

Рисунок 10.4 – ОЗУ со структурой шины адреса 2DM

10.3 ОЗУ с двухмерной адресацией

В ЗУ с двухмерной адресацией возможно заносить и выбирать информацию по одному биту (см. рисунок 10.5). Адресный код делится на две части – первая часть позволяет определить строку, вторая – столбец. На пересечении строки и столбца будет находится ЯП, информацию из которой необходимо выбрать.

Рисунок 10.5 – ОЗУ с двухмерной организацией шины адреса

Во всех сериях широкого применения имеются элементы ОЗУ. В обозначении ИМС после номера серии используют буквы РУ. Например, К155РУ2 – статическое ОЗУ емкостью 64К со структурой 16 х 4 (см. рисунок 10.6).

Микросхема К537РУ8 (см. рисунок 10.7) – это статическое ОЗУ объемом 2Кбайта, выполнена на основе КМОП технологий, совместима с ТТЛ уровнями. Имеет двунаправленную 8-ми разрядную шину данных, которая используется и для записи и для считывания информации.

Рисунок 10.6 – Микросхема К155РУ2, статическое ОЗУ

Рисунок 10.7 – Микросхема К537РУ8, статическое ОЗУ

Микросхема К565РУ5 (см. рисунок 10.8) – динамическое ОЗУ на основе n-МОП – структур, по входам и выходам совместима с ТТЛ уровнями, имеет организацию 64К х 1. Шина адреса работает в мультиплексированном режиме. Вначале на ней выставляются адреса строк, которые запоминаются во внутреннем регистре по спаду сигнала RAS. Затем выставляются адреса столбцов, которые запоминаются по спаду сигнала CAS.

К537РУ8 и К565РУ5 имеют выходы с тремя состояниями.

Рисунок 10.8 – Микросхема К565РУ5, динамическое ОЗУ

При необходимости увеличить разрядность шины данных, ОЗУ включают в параллель. При этом шину адреса одновременно подают на все ИМС, в каждой из которых хранятся по соответствующему адресу данные, считываемые в разные выходные разряды (см. рисунок 10.9).

Рисунок 10.9 – Способ расширения разрядности ОЗУ

Постоянные запоминающие устройства (ПЗУ)

Постоянно запоминающие устройства (ПЗУ, ROM – read only memory) предназначены для хранения информации, которая остается неизменной в течение всего времени работы устройства. ПЗУ отличает его энергонезависимость. Процесс считывания информации не разрушает ее.

Классификация ПЗУ представлена на рисунке 10.10.

Рисунок 10.10 – Классификация ПЗУ

Информация в ПЗУ представляется в виде наличия или отсутствия соединения между шиной адреса и шиной данных. В этом смысле ПЗУ очень похож на преобразователь кодов.

Иллюстрация функционирования ПЗУ масочного типа представлена на рисунке 10.11.

Рисунок 10.11 – ПЗУ масочного типа

К масочным ПЗУ относятся цифровые устройства памяти, в которые информация заносится непосредственно в процессе их изготовления. Название этим элементам было присвоено благодаря применению технологии маскирования определенных связей при формировании цифровой структуры на кристалле полупроводника.

Масочные ПЗУ применяют в решении стандартных задач: преобразовании кодов (клавиатуры, знаковые генераторы, стандартные загружаемые программы – BIOS и т.д.)

С учетом совмещения процесса производства и программирования ПЗУ масочного типа характеризуются низкой стоимостью, но малой гибкостью в приложениях.

На принципиальных схемах масочные ПЗУ обозначают ROM или ПЗУ. К ним относятся ИМС, в названии которых имеются буквы РЕ, например К155РЕ21, К155РЕ22

Прожигаемые ПЗУ (однократно программируемые) – относятся к классу устройств, программируемых однократно пользователем. По структуре программируемые ПЗУ являются устройствами с одномерной адресацией типа 2DM (см. рисунок 10.12). Обозначают данные элементы на схемах ППЗУ или PROM.

Рисунок 10.12 – Структурная схема однократно прожигаемых ППЗУ

В ППЗУ матрица накопления информации построена чаще всего на плавких перемычках, изготовленных из тугоплавкого материала, например нихрома. Запись информации заключается в пережигании данных перемычек управляющим сигналом.

В некоторых случаях в качестве ячейки памяти используют два встречно включенных диода, соединяющих соответствующую строку и столбец. При подаче повышенного напряжения диод, включенный в обратном направлении пробивается, соединяя тем самым две цепи.

ППЗУ выпускают в составе многих серий микросхем. В названии ППЗУ присутствуют буквы РТ, например К541РТ1 – ППЗУ с матрицей 256 х 4.

Для программирования ППЗУ используют специальные программаторы.

Перепрограммируемые ПЗУ строятся на основе МОП-технологий, связанные, как правило, с явлением хранения заряда на границе между двумя диэлектрическими средами.

На рисунке 10.13 представлена схема ЛИЗМОП (лавинно-инжекционный транзистор с плавающим затвором) транзистора выполненного по МОП технологиям. Высокое напряжение на стоке ( 20 В) создает лавинный пробой диэлектрика и на плавающий затвор инжектируются заряды, которые удерживаются в окружающем его диэлектрике годами. Для стирания информации достаточно подать напряжение на прямой затвор. При этом рассасывание заряда происходит за счет туннельного эффекта.

ИМС с электрическим перепрограммированием называют E2PROM.

Рисунок 10.13 – Структурная схема ЛИЗМОП транзистора – основы РППЗУ с электрической записью-стиранием

С использованием ЛИЗМОП транзисторов строятся и РПЗУ с ультрафиолетовым стиранием информации. В корпусах данных РПЗУ имеется окошко для облучения кристалла. Информация при облучении стирается полностью. Подобные ИМС обозначаются EPROM.

Флеш-память подобна ППЗУ с электрической записью и стиранием. В ее организации имеется особенность, связанная с быстродействием: стирание осуществляется или всей записанной информации, или больших блоков.

Флеш-пямять не предназначена для частой перезаписи.

Матрица памяти построена на ЛИЗМОП транзисторах с их параллельным включением, обеспечивающим быстрый доступ к хранимой информации. Число циклов стирания для лучших вариантов лежит в пределах 105. Время стирания всего объема находится в диапазоне 0,5 ÷ 4,0с для N 2 Мбит, доступ при чтении составляет примерно 100 нс.

АНАЛОГО-ЦИФРОВЫЕ ПРЕОБРАЗОВАТЕЛИ

Аналого-цифровые преобразователи (АЦП) – это устройства, предназначенные для преобразования аналоговых сигналов в цифровую форму.

Основной принцип преобразования лежит в реализации округления аналоговой величины до ближайшего уровня квантования, при этом погрешность процесса (методическая) лежит в пределах 0,5τ (см. рисунок 11.1).

Рисунок 11.1 – Принцип идеального квантования по уровню

К основным характеристикам АЦП относятся:

- число цифровых разрядов на выходе преобразователя;

- время процесса;

- погрешность преобразователя (нелинейность в том числе).

Число разрядов – предельное количество разрядов кода, связанного с преобразуемой аналоговой величиной. Число разрядов определяет разрешающую способность АЦП, под которой понимают значение шага квантования, приведенного к аналоговой величине. Например, для 10-ти разрядного АЦП (количество уровней квантования τ∑ = 1024) разрешающая способность преобразования аналогового напряжения величиной в 10В не превышает 10 мВ, т. е. преобразовать в цифровую форму сигнал меньше 10 мВ подобным АЦП невозможно.

Время процесса – это время, затрачиваемое на преобразование аналоговой величины в цифровую форму. Время преобразования для различных типов АЦП варьируется в широких пределах. Наиболее быстродействующие устройства затрачивают на процесс преобразования несколько наносекунд (АЦП параллельного типа на основе ЭСЛ логики).

Под погрешностью преобразователя понимается отклонение значения цифрового кода от величины аналогового сигнала. Чаще всего погрешность выражается процентом нелинейности () характеристики:

где Аm – максимальное значение преобразуемого аналогового сигнала;

С – значение цифрового кода.

Классификация АЦП по методу преобразования представлена на рисунке 11.2.

Рисунок 11.2 – Классификация аналого-цифровых преобразователей

11.1 АЦП последовательного приближения

Аналого-цифровые преобразователи, работающие по методу последовательного приближения (счета), осуществляют уравновешивание входной аналоговой величины суммой одинаковых эталонов. Момент равенства этих величин фиксируется сравнивающим устройством (компаратором). На выходе таких АЦП формируется последовательный единичный код, который с помощью обычных счетчиков (дешифраторов) преобразуется в двоичную форму.

Функциональная схема (один из вариантов) АЦП последовательного счета изображена на рисунке 11.3.

Для упрощения понимания работы, как правило, используют графическую форму анализа (см.рисунок 11.4).

УС – устройство сравнения (компаратор), Г – генератор импульсов, Глн – генератор линейного напряжения, К – цифровой ключ (логический элемент «И»), СТ2 – двоичный счетчик, БУ – блок управления

Рисунок 11.3 – Функциональная схема АЦП последовательного приближения

По сигналу блока управления (БУ) запускается генератор линейного напряжения (ГЛН). Входной преобразуемый UВХ сигнал и сигнал ГЛН подаются на устройство сравнения. Пока входное напряжение больше линейно нарастающего напряжения, на выходе компаратора будет уровень логической единицы, который разрешит прохождение меандра от генератора импульсов (Г) на счетный вход двоичного счетчика (СТ2). На выходе СТ2 будет формироваться двоичный код пропорциональный линейно нарастающему напряжению. В момент, когда напряжение ГЛН превысит значение UВХ компаратор закроет цифровой ключ, прекратит подачу импульсов на СТ2. В выходных разрядах СТ2 сформируется код пропорциональный уже UВХ.

Единственным достоинством подобного АЦП является простота его аппаратной реализации.

К недостаткам следует отнести длительность процесса преобразования, который каждый раз начинается с нулевого уровня напряжения ГЛН, сравнительно высокую погрешность преобразования, объясняемую тем, что СУ реагирует на мгновенное значение UВХ, величина которого может содержать сигнал помехи (как правило, это наводка на входные цепи сигнала частотой промышленной сети).

АЦП последовательного приближения используется в устройствах, не отличающихся высоким быстродействием и точностью аналоговой части.

Рисунок 11.4 – Графический анализ работы АЦП последовательного счета

11.2 АЦП «напряжение – частота»

АЦП «напряжение – частота» используется в простейших устройствах, чаще всего в датчиках технологических параметров. Назначение подобных преобразователей – повысить надежность передачи информации на расстояние, т. к. цифровой код имеет более высокую степень помехозащиты, чем аналоговый сигнал.

На рисунке 11.5 приведена функциональная схема преобразователя постоянного напряжения (-UВХ)в частоту импульсов (f)

А1

Рисунок 11.5 – Функциональная схема АЦП «напряжение- частота»

Графическая форма анализа работы устройства приведена на рисунке 11.6.

Основой функционирования данного преобразователя является интегратор, построенный на базе операционного усилителя А1. При подаче на его вход постоянного напряжения –UВХ на выходе интегратора будет формироваться линейно возрастающее напряжение:

Величина преобразуемого напряжения определяет в этом случае скорость изменения напряжения на выходе интегратора. Выходной сигнал А1 поступает на вход аналогового компаратора, где сравнивается с опорным напряжением UОП . В момент равенства компаратор формирует посредством формирователя импульса сброса быстрый разряд интегратора, после чего процесс преобразования повторяется. АЦП «напряжение – частота» имеют коэффициент преобразования 10 кГц / В.

Рисунок 11.6 – Графический анализ работы АЦП «напряжение- частота»

Как и в АЦП последовательного счета АЦП «напряжение – частота» требуют качественной фильтрации входных преобразуемых сигналов, поскольку реагируют на мгновенное значение входного напряжения.

Вследствие указанных недостатков рассмотренные выше АЦП при разработке ИМС не используются.

11.3 АЦП поразрядного уравновешивания

Основой данного АЦП (см. рисунок 11.7) является регистр последовательного поразрядного приближения (РПП). По каждому импульсу генератора тактовых импульсов (ГТИ) производится предустановка соответствующего RS - триггера на выходе РПП в единичное состояние, что последовательно пошагово изменяет двоичный код, поступающий на цифро – аналоговый дешифратор. При этом цифровой код формируется в порядке убывания – от старшего к младшему.

На рисунке 11.8 приведены временные диаграммы, поясняющие работу рассматриваемого АЦП.

K

Рисунок 11.7 – Блок-схема АЦП поразрядного уравновешивания

Рисунок 11.8 – Временные диаграммы функционирования АЦП поразрядного уравновешивания

По импульсу запуска преобразования (ПУСК) производится:

- обнуление регистра RG, занесение в его младший разряд единицы;

- запись единицы в старший разряд выходного регистра РПП (через дифференцирующую цепочку);

- запись в остальные выходные разряды РПП нулевых уровней.

Установившийся код на выходе РПП преобразуется дешифратором в аналоговую форму напряжения, которое подается на сравнивающее устройство (компаратор К) совместно с входным преобразуемым сигналом (UВХ). Если напряжение (код РПП) меньше UВХ на выходе компаратора сохранится низкий уровень, обеспечивая запись единицы в выходном триггере РПП «1» и следующим импульсом ГТИ единица из младшего разряда RG сдвинется влево. Появление высокого уровня на соответствующем выходе RG вызовет предустановку следующего по порядку выходного триггера РПП в активный режим. Вновь сформировавшийся код в аналоговой форме сравнивается с UВХ . В случае, когда UВХ < UРПП, на выходе К появляется короткий импульс, который перебрасывает активный предустановленный разряд выходного триггера РПП в нулевой уровень – записывает в данный разряд ноль.

Таким образом, осуществляется перебор всех разрядов входного регистра RG (см. рисунок 11.8) и подбор цифрового кода, соответствующего UВХ. Время преобразования составляет единицы микросекунд. Данный вид АЦП является одним из самых быстродействующих.

К недостаткам следует отнести невысокую помехозащищенность преобразователя – сформированный код сравнивается с мгновенным значением UВХ , в составе которого может быть помеха.

Примером ИМС, реализующей метод поразрядного уравновешивания является микросхема К572ПВ1, 12-ти разрядный АЦП с временем преобразования 10мкс и нелинейностью 3 ед. младшего разряда.

11.4 АЦП двойного интегрирования

АЦП с двойным интегрированием является разновидностью устройств, реализующих метод последовательного приближения (см. рисунок 11.9). Однако, от рассмотренных выше аппаратных средств его отличает повышенная точность и помехозащищенность.

В процессе преобразования UВХ проходит операцию интегрирования, в процессе которой гармонические помехи (чаще всего сетевые), обнуляются за счет равенства или кратности времени интегрирования периоду следования помехи.

Принцип работы АЦП двойного интегрирования поясняется временными диаграммами, приведенными на рисунке 11.10. Функционирование устройства начинается с подачи пускового импульса (t0) блока управления (БУ), который подключает посредством аналогового ключа (К1) UВХ к входной цепи интегратора А1.

RИ

А1

Рисунок 11.9 – Блок-схема АЦП двойного интегрирования

t0

t1

t2

t3

t0

Рисунок 11.10 – Временные диаграммы функционирования АЦП двойного интегрирования

Режим замкнутого состояния ключа К1 находится в промежутке времени t0 – t2, в интервале времени t2 – t3 ключ К1 размыкается, но замыкается ключ К2, при этом на вход интегратора поступает напряжение образцового источника ЕО, противоположное по знаку UВХ, приводя к перезарядке конденсатора. Скорость перезарядки определяется только стабильностью ЕО , а время – напряжением, до которого зарядился интегратор. Напряжение же интегратора в момент времени t2 зависит от величины преобразуемого UВХ, т.к. время зарядки стабилизировано режимом работы БУ. Ненулевая величина опорного напряжения, подаваемого на вход сравнивающего устройства UОП подавляет нестабильность выходного напряжения интегратора в режиме паузы. Формирователь временного интервала разряда интегратора (Фt) выдает разрешение на запись сигнала генератора тактовых импульсов (ГТИ) двоичному счетчику с четырех разрядным семисегментным дешифратором на выходе (СТ2/7). Начало счета импульсов ГТИ определяется сигналом дифференцирующего элемента (d/dt), синхронизированного БУ.

Время интегрирования t0 – t2 выбирается (задается БУ временем замкнутого состояния ключа К1) с учетом кратности периода действующей помехи (частота силовой сети 50-60Гц). Для стабильности времязадающих цепей к внешним управляющим разрядам АЦП подключают кварцевый резонатор.

Время преобразования АЦП двойного интегрирования лежит в диапазоне нескольких десятков миллисекунд.

11.5 АЦП параллельного преобразования

АЦП данного типа реализует метод непосредственного считывания и на сегодняшний день является самым быстродействующим. Принцип его работы поясняется блок – схемой, приведенной на рисунке 11.11.

Устройство содержит 2(m-1) входных компараторов, на которые через делитель напряжения поступает UВХ.

Рисунок 11.11 – Блок-схема АЦП параллельного преобразования

С выходов компараторов снимается N-разрядный единичный код, который подается на вход дешифратора – преобразователя кодов. На выходе преобразователя кодов формируется двоичный код с числом разрядов m = lg2N, через элементы совпадения считываемый статическим выходным регистром по сигналу «ЗАПИСЬ» .

Особенностью данных АЦП является ограничение разрядности аппаратной реализации. Так для восьми разрядного преобразователя требуется 255 входных компараторов. С учетом дополнительных элементов функционирования общее число внутренних структур достигает 3104, при потребляемой мощности 2,5 Вт.

Компромисс между быстродействием и сложностью достигается путем объединения элементов в параллельно-последовательную схему (см. рисунок 11.12).

Рисунок 11.12 – Блок-схема АЦП параллельного последовательного типа

Реальное время преобразования АЦП параллельного типа составляет 10-20 нс (для 5 – 6 разрядного выходного кода).

12 ЦИФРО – АНАЛОГОВЫЕ ПРЕОБРАЗОВАТЕЛИ

Цифро-аналоговые преобразователи (ЦАП) предназначены для преобразования цифрового, как правило, двоичного, кода в аналоговую величину. Эта операция необходима, например, при связи внешнего устройства (двигатель, клапан, нагреватель) с управляющим контроллером.

К основным параметрам ЦАП относятся:

- разрешающая способность;

- время преобразования (установления);

- погрешность (нелинейность).

Разрешающая способность – это величина обратная максимальному числу шагов квантования выходного аналогового сигнала.

Время установления (tуст) - интервал времени между моментом изменения цифровой информации на входе устройства и моментом установления аналогового сигнала на выходе.

Погрешность преобразования - максимальное отклонение характеристики ЦАП во всем диапазоне изменения цифрового сигнала от идеальной прямой линии.

Из широкого круга известных способов реализации преобразования цифрового кода в аналоговый сигнал в настоящее время применяются только ЦАП суммирующего типа. Они имеют две разновидности: с матрицей «R2n» (n – число цифровых разрядов) и «R – 2R» (см. рисунок 12.1). Суммирование осуществляется на основе использования операционного усилителя, включенного по схеме сумматора.

Функциональная схема ЦАП с матрицей «R2n» представлена на рисунке 12.2.

При нулевом цифровом коде на входе преобразователя аналоговые ключи К0 ÷ Кn замкнуты на общий провод, что формирует на выходе напряжение равное нулю.

Рисунок 12.1 – Классификация ЦАП

Появление единицы в любом разряде входного кода посредством соответствующего ключа замыкает весовое сопротивление Ri на источник опорного напряжения (UОП). Вклад от разрядного тока в выходное напряжение пропорционально весу соответствующего разряда и определяется величиной входного сопротивления. Другими словами, одно и тоже UОП вносит вклад в выходное напряжение пропорционально коэффициенту передачи:

Рисунок 12.2 – ЦАП весового типа с матрицей R2n

Величина R0 младшего разряда больше Rn в старшем разряде в 2n раз. Это является недостатком аппаратной реализации, т.к. в технологии производства ИМС сложно обеспечить точную подгонку сопротивлений отличающихся порой на несколько порядков (например, для n = 12 резистор R12 = 1 кОм, а R0 = 4,096 Мом).

Рисунок 12.3 – ЦАП весового типа с матрицей R-2R

Гораздо проще в реализации весовые (суммирующие) ЦАП с матрицей сопротивлений «R – 2R». На рисунке 12.3 представлена функциональная схема этого устройства. От предыдущей конструкции его отличает иная организация цепей суммирования. Вместо изменения весового сопротивления введено изменение величины опорного напряжения пропорционально весу суммируемого разряда. В этом случае матрица резисторов выглядит вполне симметричной и легко реализуемой технологически в микросхемотехнике.

13 ГЕНЕРАТОРЫ НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ, ТАЙМЕРЫ

На основе логических элементов достаточно просто строятся релаксационные генераторы – генераторы прямоугольных и пилообразных импульсов. Релаксационные генераторы могут работать в режиме автогенератора, в ждущем режиме и как таймеры (см. рисунок 13.1).

Автоколебательный режим служит для получения импульсов заданной формы без постороннего запускающего сигнала. Ждущие генераторы формируют импульс заданной конфигурации по приходу запускающего напряжения. Таймер относится к специализированным средствам, предназначенным для формирования импульсов с заданной скважностью и длительностью.

Рисунок 13.1 – Классификация релаксационных генераторов

13.1 Автогенераторы на БЛЭ

Импульсные автогенераторы делятся на мультивибраторы и блокинг-генераторы. И первые, и вторые могут работать в автоколебательном и ждущем режимах.

Генераторы прямоугольных импульсов строятся на дискретных, логических элементах и операционных усилителях. В данном разделе основное внимание будет уделено построению генераторов на базовых логических элементах.

На рисунке 13.2 изображена функциональная схема релаксационного генератора на базе двух инверторов и интегрирующей RC – цепи.

Рисунок 13.1 – Генератор на элементах «2И-НЕ»

Особенностью

данного решения является использование

одной времязадающей RC

– цепи для самовозбуждения и сдвига

фазы выходного сигнала с целью получения

ПОС. В первый момент времени после подачи

напряжения на инверторы резистор R

создает отрицательную обратную связь,

выводя каскад первого инвертора на

линейный участок ВАХ, обеспечивая тем

самым значение петлевого усиления β·К

> 1. В последующем по мере нарастания

напряжения на емкости за счет инверсии

фазы формируется ПОС, что приводит к

формированию стабильных импульсных

колебаний с частотой

Для данного RC генератора характерно различие в постоянных времени заряда (τЗАР) и разряда (τРАЗ) из-за неравенств входного и выходного сопротивлений инвертора, следовательно, в общем случае, скважность импульсов на выходе будет отлична от q = 2.

Характерной особенностью релаксационных генераторов является с одной стороны зависимость частоты выходного прямоугольного сигнала от напряжения питания и температуры, с другой ограниченный частотный диапазон самовозбуждения, как снизу, так и сверху. Нижняя граница частоты самовозбуждения определяется величиной петлевого усиления – при сравнительно небольшом К и малом β (большое значение R) релаксационные колебания не возникают. Верхний частотный диапазон ограничен частотными свойствами активных элементов инверторов. Колебания напряжения питания и температуры изменяют положение рабочей точки каскада и параметры времязадающей RC – цепи, что в итоге приводит к уходу периода следования импульсов на выходе генератора.

Для стабилизации частоты используют так называемый кварцевый генератор, принципиальная схема которого приведена на рисунке 13.3

Рисунок 13.3 – Кварцевый релаксационный генератор

Высокая стабильность частоты генерации используется для сложных цифровых устройств, ее относительное изменение часто не должно превышать 0,001%. Такая стабильность частоты в практике может быть достигнута многими способами, но наиболее применимым является кварцевая стабилизация.

Кварцевые резонаторы изготавливают из монокристаллического кварца. Пластину кварца ориентируют определенным образом относительно выбранной кристаллографической оси. В рабочем режиме к пластине, как правило, приложено переменное напряжение, что формирует в ней различного рода колебания: сжатие-растяжение, изгиб, кручение и т.д.

Кварцевую пластину с точки зрения ее электрических свойств можно представить в виде эквивалентной схемы (см. рисунок 13.4).

Рисунок 13.3 – Схема замещения кварцевого резонатора

Согласно этой схеме, в кварцевом резонаторе может наблюдаться последовательный и параллельный резонанс. Для первого, частота резонанса определяется как:

для второго:

Кварцевые пластины

обладают высокой стабильностью свойств

и добротностью. Например, добротность

контура последовательного резонанса

лежит ( )

в пределах

)

в пределах . На частоте резонанса сопротивление

контура резко падает, что позволяет

использовать кварцевые резонаторы в

высокостабильных элементах частотно

зависимых ПОС.

. На частоте резонанса сопротивление

контура резко падает, что позволяет

использовать кварцевые резонаторы в

высокостабильных элементах частотно

зависимых ПОС.

Разновидностью релаксационных генераторов являются генераторы производящие мощные импульсы малой длительности (от долей микросекунды до долей миллисекунды) и скважностью до нескольких тысяч – блокинг-генераторы, которые могут работать как автогенераторы и одновибраторы. Принципиальная схема блокинг-автогенератора приведена на рисунке 13.4.

Рисунок 13.4 – Схема блокинг-генератора

Временные диаграммы работы устройства представлены на рисунке 13.5. Функционирование блокинг-генератора заключается в поочередной перезарядке емкости С, при этом цепи перезаряда имеют разные постоянные времени τ– = C · rВХ_VT1, τ+ = C · R1, где rВХ_VT1 – входное сопротивление открытого транзистора VT1. Направление перезарядки осуществляется в моменты лавинообразного открытия и закрытия транзистора. Лавинообразность процессов определяется наличием положительной обратной связи за счет витков WСВ, включенных встречно с первичной обмоткой трансформатора W1. Напряжение UСВ и UН в виде короткого импульса формируется только в момент перехода транзистора из состояния токовой отсечки в состояние насыщения и обратно.

Рисунок 13.5 – Временные диаграммы работы блокинг-генератора

Открытие транзистора начинается при достижении UБ = UСВ + UC начального нулевого порога. Незначительное увеличение тока базы даже на пологой ветви входной ВАХ транзистора ведет к изменению напряжения в первичной обмотке трансформатора W1, следовательно, и во вторичной обмотке связи Wсв. Напряжение UСВ находящееся в фазе с напряжением UБ опрокидывает VT1, он мгновенно открывается и емкость С начинает перезарядку через входное сопротивление открытого транзистора от напряжения UСВ. По мере перезарядки UБ уменьшается (отсутствие изменения тока коллектора – VT1 находится в насыщении, уменьшает и UСВ) и в некоторый момент становится меньше нуля, возвращая транзистор в запертое состояние. К базе оказывается приложено отрицательное напряжение емкости UС . Она начинает перезаряжаться от источника питания +UП через сопротивление R1. За счет того, что τ+ = C · R1 >> τ– = C · rВХ_VT1 импульс, в течение которого энергия накопленная в трансформаторе сбрасывается в нагрузку, является очень коротким, а пауза продолжительной (скважность превышает несколько тысяч).

13.2 Одновибраторы

Логические элементы могут найти использование и в одновибраторах, которыми называют автогенераторные устройства с наличием одного устойчивого состояния, при этом второе состояние квазиустойчивого равновесия приводит к формированию на выходе импульса с заданными временными характеристиками.

Принципиальная схема одной из множества возможных конструкций одновибратора, собранного на БЛЭ представлена на рисунке 13.6.

Импульс возбуждения подается на один из входов элемента «И» структуры, по организации связей напоминающей RS – триггер с инверсным управлением. Наличие емкостей (С1 и С2) в цепях перекрестных обратных связей и независимый вход управления (UУПР) позволило переводить устойчивое состояние структуры в квазиустойчивое по приходу управляющего сигнала.

Рисунок 13.6 – Принципиальная схема одновибратора на элементах «2И – НЕ» и временные диаграммы, поясняющие его работу

В режиме устойчивого равновесия на выходе DD1 присутствует логическая единица (на входе «0»), DD2 – логический ноль (на входе «1»). Нулевой управляющий сигнал приводит к нарушению режима равновесия – на выходах элементов DD1 и DD2 сигналы инвертируются на время заряда емкостей, которое зависит от произведения R1C2 и R2C1. Возврат одновибратора в прежнее состояние определяется временем зарядки конденсаторов до уровней срабатывания логических элементов (горизонтальные пунктирные линии, см. рисунок 13.6).

Одновибратор на основе RS – триггера может быть также сформирован с помощью одной времязадающей цепи (цепь R3C, см. рисунок 13.7).

13.3 Таймеры в интегральном исполнении

Таймером называют цифровое устройство, предназначенное для формирования импульсов напряжения с изменяемыми длительностью и скважностью.

В современной электронике таймер выполняется в виде специализировнанной интегральной схемы или отдельного модуля, входящего в состав БИС (СБИС). В последнем случае времязадающие RC элементы (в некоторых случаях кварцевые резонаторы) подключают к выделенным входным цепям.

а

б

а – принципиальная схема, б – временные диаграммы

Рисунок 13.7 – Принципиальная схема одновибратора с одной времязадающей цепью на RS – триггере и диаграммы, поясняющие работу устройства

С точки зрения функциональных особенностей таймеры могут быть разделены на два класса: однотактные и многотактные (см. рисунок 13.8).

Рисунок 13.8 – Классификация таймеров

Первые имеют более простую схему и предназначены для формирования импульсов с длительностью от единиц микросекунд до одного часа. Функциональная схема однотактного таймера приведена на рисунке 13.9 и содержит в своем составе компаратор (DA1), RS- триггер (DD1), электронный ключ (VT1) и внешнюю RC цепь (R3C).

Рисунок 13.9 – Функциональная схема однотактного таймера

Рисунок 13.9 – Функциональная схема многотактного таймера

Рисунок 13.10 – Функциональная схема таймера К1006ВИ1

а – принципиальная схема мультивибратора; б – временные диаграммы работы

Рисунок 13.11 – Схема мультивибратора на таймере К1006ВИ1