- •Release History

- •Contents

- •List of Figures

- •List of Tables

- •1 TMS320TCI6616 Features

- •1.1 KeyStone Architecture

- •1.2 Device Description

- •1.3 Functional Block Diagram

- •2 Device Overview

- •2.1 Device Characteristics

- •2.2 CPU (DSP Core) Description

- •2.3 Memory Map Summary

- •2.4 Boot Sequence

- •2.5 Boot Modes Supported and PLL Settings

- •2.5.1 Boot Device Field

- •2.5.2 Device Configuration Field

- •2.5.2.1 No Boot Device Configuration

- •2.5.2.2 Serial Rapid I/O Boot Device Configuration

- •2.5.2.3 Ethernet (SGMII) Boot Device Configuration

- •2.5.2.4 PCI Boot Device Configuration

- •2.5.2.5 I2C Boot Device Configuration

- •2.5.2.6 SPI Boot Device Configuration

- •2.5.2.7 HyperLink Boot Device Configuration

- •2.5.3 PLL Settings

- •2.6 Second-Level Bootloaders

- •2.7 Terminals

- •2.8 Terminal Functions

- •2.9 Development

- •2.9.1 Development Support

- •2.9.2 Device Support

- •Related Documentation from Texas Instruments

- •3 Device Configuration

- •3.1 Device Configuration at Device Reset

- •3.2 Peripheral Selection After Device Reset

- •3.3 Device State Control Registers

- •3.3.1 Device Status (DEVSTAT) Register

- •3.3.2 Device Configuration Register

- •3.3.3 JTAG ID (JTAGID) Register Description

- •3.3.4 Kicker Mechanism (KICK0 and KICK1) Register

- •3.3.5 LRESETNMI PIN Status (LRSTNMIPINSTAT) Register

- •3.3.6 LRESETNMI PIN Status Clear (LRSTNMIPINSTAT_CLR) Register

- •3.3.7 Reset Status (RESET_STAT) Register

- •3.3.8 Reset Status Clear (RESET_STAT_CLR) Register

- •3.3.9 Boot Complete (BOOTCOMPLETE) Register

- •3.3.10 Power State Control (PWRSTATECTL) Register

- •3.3.11 NMI Even Generation to CorePac (NMIGRx) Register

- •3.3.12 IPC Generation (IPCGRx) Registers

- •3.3.13 IPC Acknowledgement (IPCARx) Registers

- •3.3.14 IPC Generation Host (IPCGRH) Register

- •3.3.15 IPC Acknowledgement Host (IPCARH) Register

- •3.3.16 Timer Input Selection Register (TINPSEL)

- •3.3.17 Timer Output Selection Register (TOUTPSEL)

- •3.3.18 Reset Mux (RSTMUXx) Register

- •3.4 Pullup/Pulldown Resistors

- •4 System Interconnect

- •4.1 Internal Buses, Bridges, and Switch Fabrics

- •4.2 Data Switch Fabric Connections

- •4.3 Configuration Switch Fabric

- •4.4 Bus Priorities

- •5 C66x CorePac

- •5.1 Memory Architecture

- •5.1.1 L1P Memory

- •5.1.2 L1D Memory

- •5.1.3 L2 Memory

- •5.1.4 MSM SRAM

- •5.1.5 L3 Memory

- •5.2 Memory Protection

- •5.3 Bandwidth Management

- •5.4 Power-Down Control

- •5.5 CorePac Resets

- •5.6 CorePac Revision

- •5.7 C66x CorePac Register Descriptions

- •6 Device Operating Conditions

- •6.1 Absolute Maximum Ratings

- •6.2 Recommended Operating Conditions

- •6.3 Electrical Characteristics

- •7 TMS320TCI6616 Peripheral Information and Electrical Specifications

- •7.1 Parameter Information

- •7.1.1 1.8-V Signal Transition Levels

- •7.1.2 Timing Parameters and Board Routing Analysis

- •7.2 Recommended Clock and Control Signal Transition Behavior

- •7.3 Power Supplies

- •7.3.1 Power-Up Sequencing

- •7.3.1.1 Core-Before-IO Power Sequencing

- •7.3.1.2 IO-Before-Core Power Sequencing

- •7.3.1.3 Prolonged Resets

- •7.3.2 Power-Down Sequence

- •7.3.3 Power Supply Decoupling and Bulk Capacitors

- •7.3.4 SmartReflex

- •7.4 Enhanced Direct Memory Access (EDMA3) Controller

- •7.4.1 EDMA3 Device-Specific Information

- •7.4.2 EDMA3 Channel Synchronization Events

- •7.5 Interrupts

- •7.5.1 Interrupt Sources and Interrupt Controller

- •7.5.2 INTC Registers

- •7.5.2.1 INTC0 Register Map

- •7.5.2.2 INTC1 Register Map

- •7.5.2.3 INTC2 Register Map

- •7.5.3 Inter-Processor Register Map

- •7.5.4 NMI and LRESET

- •7.5.5 External Interrupts Electrical Data/Timing

- •7.6 Memory Protection Unit (MPU)

- •7.6.1 MPU Registers

- •7.6.1.1 MPU Register Map

- •7.6.1.2 Device-Specific MPU Registers

- •7.6.2 MPU Programmable Range Registers

- •7.6.2.1 Programmable Range n Start Address Register (PROGn_MPSAR)

- •7.6.2.2 Programmable Range n - End Address Register (PROGn_MPEAR)

- •7.6.2.3 Programmable Range n Memory Protection Page Attribute Register (PROGn_MPPA)

- •7.7 Reset Controller

- •7.7.1 Power-on Reset

- •7.7.2 Hard Reset

- •7.7.3 Soft Reset

- •7.7.4 Local Reset

- •7.7.5 Reset Priority

- •7.7.6 Reset Controller Register

- •7.7.7 Reset Electrical Data/Timing

- •7.8 Main PLL and the PLL Controller

- •7.8.1 Main PLL Controller Device-Specific Information

- •7.8.1.1 Internal Clocks and Maximum Operating Frequencies

- •7.8.1.2 Main PLL Controller Operating Modes

- •7.8.1.3 Main PLL Stabilization, Lock, and Reset Times

- •7.8.2 PLL Controller Memory Map

- •7.8.2.1 PLL Secondary Control Register (SECCTL)

- •7.8.2.2 PLL Controller Divider Register (PLLDIV2, PLLDIV5, PLLDIV8)

- •7.8.2.3 PLL Controller Clock Align Control Register (ALNCTL)

- •7.8.2.4 PLLDIV Divider Ratio Change Status Register (DCHANGE)

- •7.8.2.5 SYSCLK Status Register (SYSTAT)

- •7.8.2.6 Reset Type Status Register (RSTYPE)

- •7.8.2.7 Reset Control Register (RSTCTRL)

- •7.8.2.8 Reset Configuration Register (RSTCFG)

- •7.8.2.9 Reset Isolation Register (RSISO)

- •7.8.3 Main PLL Control Registers

- •7.8.4 Main PLL Controller/SRIO/HyperLink/PCIe Clock Input Electrical Data/Timing

- •7.9.1 DDR3 PLL Control Register

- •7.9.2 DDR3 PLL Device-Specific Information

- •7.9.3 DDR3 PLL Input Clock Electrical Data/Timing

- •7.10 PASS PLL

- •7.10.1 PASS PLL Control Register

- •7.10.2 PASS PLL Device-Specific Information

- •7.10.3 PASS PLL Input Clock Electrical Data/Timing

- •7.11 DDR3 Memory Controller

- •7.11.1 DDR3 Memory Controller Device-Specific Information

- •7.11.2 DDR3 Memory Controller Electrical Data/Timing

- •7.12 I2C Peripheral

- •7.12.1 I2C Device-Specific Information

- •7.12.2 I2C Peripheral Register Description(s)

- •7.12.3 I2C Electrical Data/Timing

- •7.12.3.1 Inter-Integrated Circuits (I2C) Timing

- •7.13 SPI Peripheral

- •7.13.1 SPI Electrical Data/Timing

- •7.13.1.1 SPI Timing

- •7.14 HyperLink Peripheral

- •7.15 UART Peripheral

- •7.16 PCIe Peripheral

- •7.17 Packet Accelerator

- •7.18 Security Accelerator

- •7.19 Ethernet MAC (EMAC)

- •7.20 Management Data Input/Output (MDIO)

- •7.21 Timers

- •7.21.1 Timers Device-Specific Information

- •7.21.2 Timers Electrical Data/Timing

- •7.22 Rake Search Accelerator (RSA)

- •7.23 Enhanced Viterbi-Decoder Coprocessor (VCP2)

- •7.24 Third-Generation Turbo Decoder Coprocessor (TCP3d)

- •7.25 Turbo Encoder Coprocessor (TCP3e)

- •7.26 Serial RapidIO (SRIO) Port

- •7.27 General-Purpose Input/Output (GPIO)

- •7.27.1 GPIO Device-Specific Information

- •7.27.2 GPIO Electrical Data/Timing

- •7.28 Semaphore2

- •7.29 Antenna Interface Subsystem 2

- •7.32 FFTC

- •7.33 Emulation Features and Capability

- •7.33.1 Advanced Event Triggering (AET)

- •7.33.2 Trace

- •7.33.2.1 Trace Electrical Data/Timing

- •7.33.3 IEEE 1149.1 JTAG

- •7.33.3.1 IEEE 1149.1 JTAG Compatibility Statement

- •7.33.3.2 JTAG Electrical Data/Timing

- •8 Mechanical Data

- •8.1 Packaging Information

- •8.2 Package CYP

TMS320TCI6616

Communications Infrastructure KeyStone SoC

SPRS624A—January 2011 |

www.ti.com |

|

8 Mechanical Data

8.1 Packaging Information

The following packaging information reflects the most current released data available for the designated device(s). This data is subject to change without notice and without revision of this document.

INFORMATION ADVANCE

196 |

Copyright 2011 Texas Instruments Incorporated |

TMS320TCI6616

Communications Infrastructure KeyStone SoC

www.ti.com |

SPRS624A—January 2011 |

|

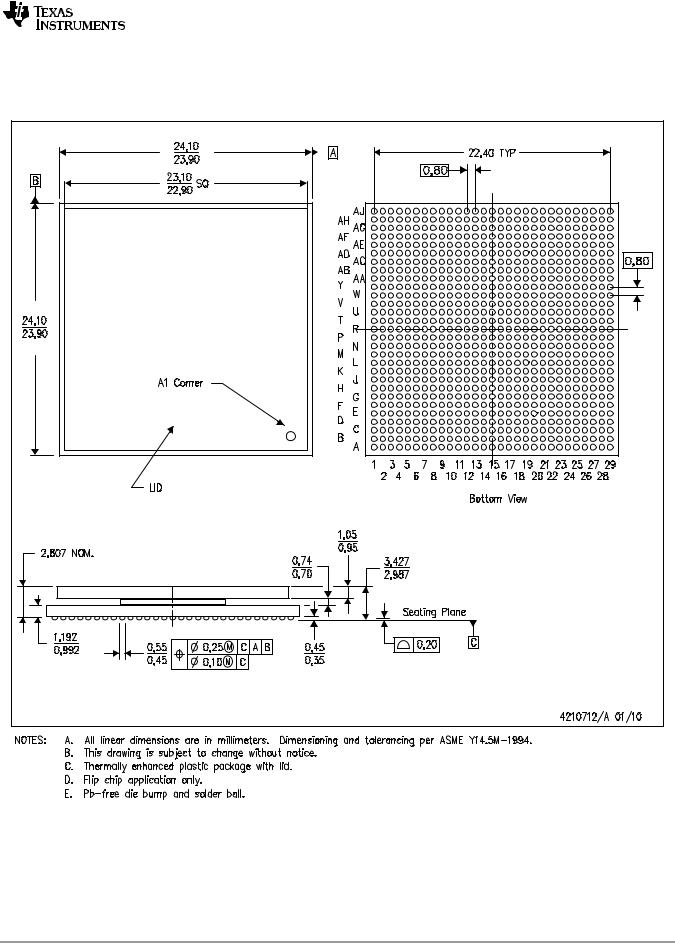

8.2 Package CYP

Figure 8-1 CYP (S–PBGA–N841) Plastic Ball Grid Array

ADVANCE INFORMATION |

Copyright 2011 Texas Instruments Incorporated |

197 |

TMS320TCI6616

Communications Infrastructure KeyStone SoC

SPRS624A—January 2011 |

www.ti.com |

|

INFORMATION ADVANCE

198 |

Copyright 2011 Texas Instruments Incorporated |

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products |

|

Applications |

|

Audio |

www.ti.com/audio |

Communications and Telecom |

www.ti.com/communications |

Amplifiers |

amplifier.ti.com |

Computers and Peripherals |

www.ti.com/computers |

Data Converters |

dataconverter.ti.com |

Consumer Electronics |

www.ti.com/consumer-apps |

DLP® Products |

www.dlp.com |

Energy and Lighting |

www.ti.com/energy |

DSP |

dsp.ti.com |

Industrial |

www.ti.com/industrial |

Clocks and Timers |

www.ti.com/clocks |

Medical |

www.ti.com/medical |

Interface |

interface.ti.com |

Security |

www.ti.com/security |

Logic |

logic.ti.com |

Space, Avionics and Defense |

www.ti.com/space-avionics-defense |

Power Mgmt |

power.ti.com |

Transportation and |

www.ti.com/automotive |

|

|

Automotive |

|

Microcontrollers |

microcontroller.ti.com |

Video and Imaging |

www.ti.com/video |

RFID |

www.ti-rfid.com |

Wireless |

www.ti.com/wireless-apps |

RF/IF and ZigBee® Solutions |

www.ti.com/lprf |

|

|

|

TI E2E Community Home Page |

e2e.ti.com |

|

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2011, Texas Instruments Incorporated