logic4(уплотнен)

.docЛАБОРАТОРНА РОБОТА № 4

Тема: Дослідження шифратора і дешифратора.

Мета роботи: Вивчення принципів проектування шифраторів і дешифраторів в заданому базисі логічних елементів, а також дослідження функціонування спроектованих шифраторів та дешифраторів.

Обладнання та програмне забезпечення: ПЕОМ, програмний комплекс Electronics Workbench.

Теоретичні відомості.

Дешифратори і шифратори (як і елементи І, АБО, НЕ, І-НЕ, АБО-НЕ) є комбінаційними елементами: сигнали на їх виходах залежать від стану входів, такі елементи не зберігають попередній стан після зміни сигналу на входах, тобто не мають пам’ять.

Дешифратори можуть бути повними й неповними. Повні дешифратори реагують на всі вхідні коди, неповні - на коди, величина яких не перевершує деякого заздалегідь встановленого значення. Виходи дешифраторів можуть бути прямими і інверсними.

Шифратори випускаються пріоритетними і непріоритетними. У пріоритетного шифратора входи мають різний пріоритет. Сигнал логічної «1» на вхід з більшим пріоритетом відміняє дію раніше діючого входу і встановлює на виходах код, який відповідає його значенню.

Дешифратор, або декодер, - це пристрій, призначений для перетворення двійкового коду на вході в керуючий сигнал на одному з виходів. Дешифратори широко використовуються в ЕОМ для вибору інформації за певною адресою, для розшифровки коду операції, в пристроях управління, для побудови розподільників імпульсу і інших.

Дешифратором, називають комбінаційний логічний пристрій для перетворення чисел з двійкової системи числення в десяткову. Згідно визначення дешифратор відноситься до класу перетворювачів кодів. Тут також кожному вхідному двійковому числу відповідає сигнал, що формується на відповідному виході пристрою. Таким чином дешифратор виконує операцію, зворотну шифратору.

Якщо дешифратор має n входів, то вихідних шин повинно бути N=2n, тому що для кожному з 2n значень вхідного коду повинен відповідати одиничний сигнал на одному із виходів дешифратора.

Якщо кількість адресних входів дешифратора n пов’язана з числом виходів N співвідношенням N=2n, то дешифратор називається повним. В іншому випадку тобто, коли N<2n, дешифратор називається неповним.

Дешифратор працює відповідно до таблиці 1.1.

Таблиця 1.1 - Таблиця істинності дешифратора

|

Х1 |

Х2 |

Х3 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

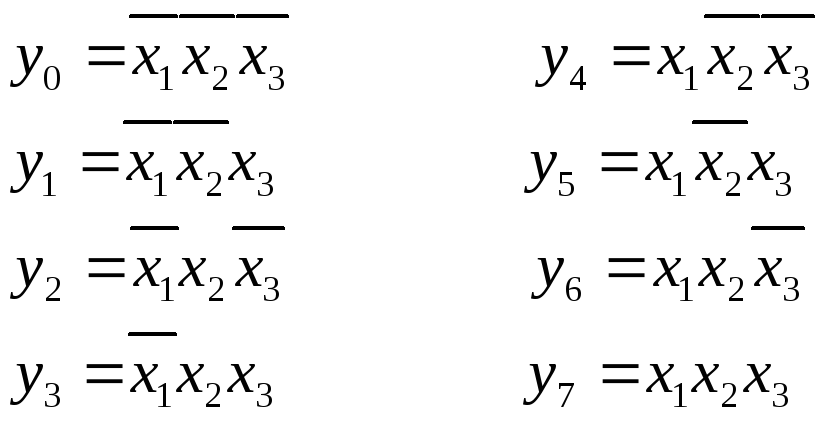

Логічні залежності дешифратора:

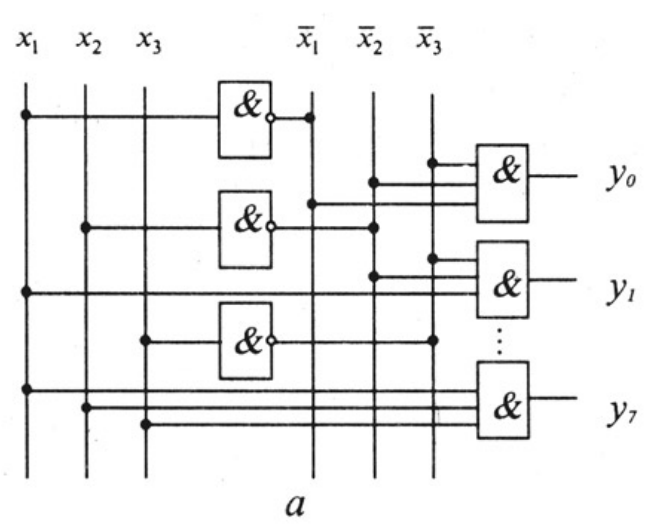

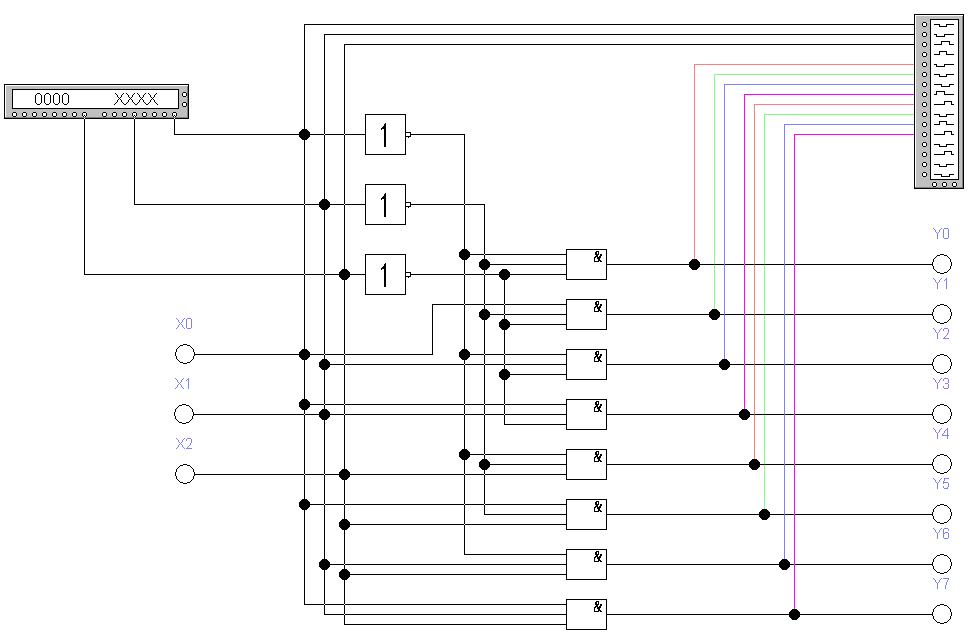

На рис. 1.1 представлені структурна схема дешифратора, побудована в базисі (І-НЕ, І), і умовне позначення на принципових електричних схемах.

Рисунок 1.1 – Структурна схема дешифратора (а) і позначення дешифратора на принципових електричних схемах (б)

Шифратором, або кодером, називають комбінаційний логічний пристрій для перетворення чисел з десяткової системи числення у двійкову. Входам шифратора послідовно надаються значення десяткових чисел, тому подача активного логічного сигналу на один з входів сприймається шифратором як подача відповідного десяткового числа. Цей сигнал на вході шифратора перетворюється в двійковий код. Згідно цього, якщо шифратор має n виходів, число його входів повинно бути не більше ніж 2n. Шифратор, що має 2n входів та n виходів, називається повним. Якщо число входів шифратора менше ніж 2n, він називається неповним.

При подачі на один із входів шифратора сигналу “лог. 1” на виході формується двійковий код, що відповідає номеру входу, на який подано сигнал логічної «1».

Шифратор працює відповідно до таблиці 1.2.

Таблиця 1.2 - Таблиця істинності шифратора

|

Входи |

Виходи |

||||||||

|

x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

x7 |

y1 |

y2 |

y3 |

|

1 0 0 0 0 0 0 |

0 1 0 0 0 0 0 |

0 0 1 0 0 0 0 |

0 0 0 1 0 0 0 |

0 0 0 0 1 0 0 |

0 0 0 0 0 1 0 |

0 0 0 0 0 0 1 |

0 0 0 1 1 1 1 |

0 1 1 0 0 1 1 |

1 0 1 0 1 0 1 |

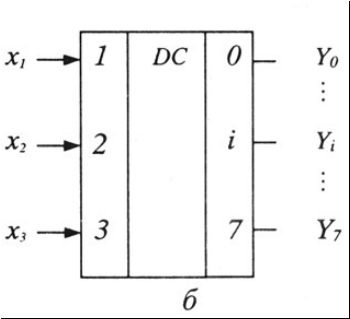

Робота шифратора описується системою логічних рівнянь складених на основі таблиці істинності:

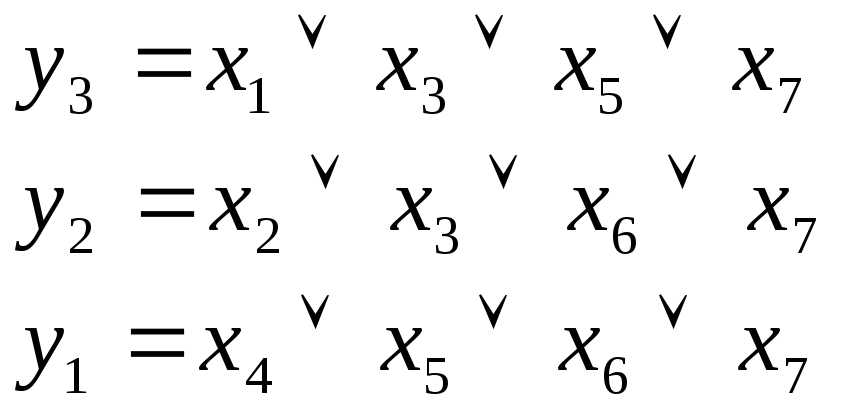

На рис. 1.2 представлені структурна схема шифратора і умовне її позначення на принципових електричних схемах ЕОМ.

а б

Рисунок 1.2 – Структурна схема шифратора (а) і позначення шифратора на принципових електричних схемах (б)

Основне застосування шифратора в цифрових схемах – це введення первинної інформації з клавіатури. При натисненні будь-якої клавіші на відповідний вхід шифратора подається сигнал логічної «1», який і перетворюється на виході в двійково-десятковий код.

Хід роботи.

Завдання 1.

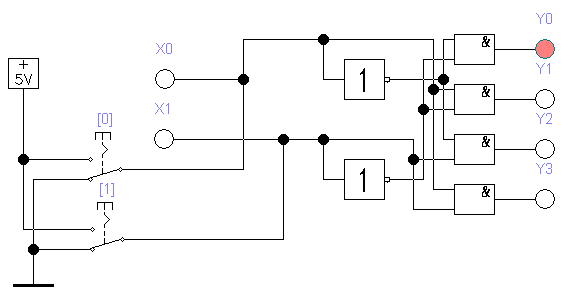

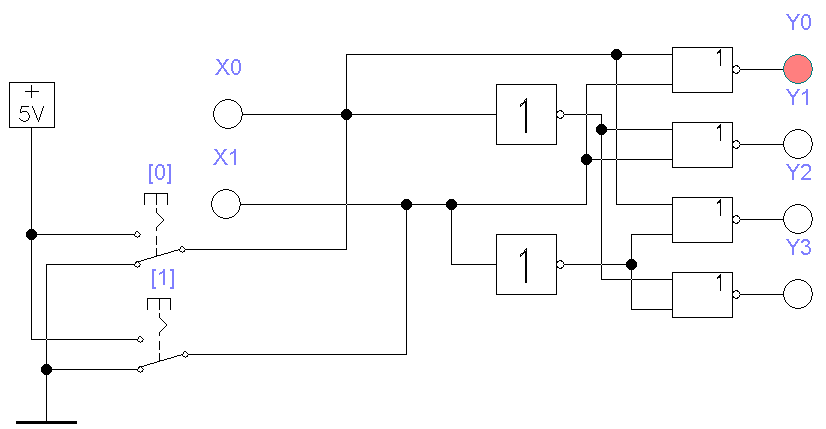

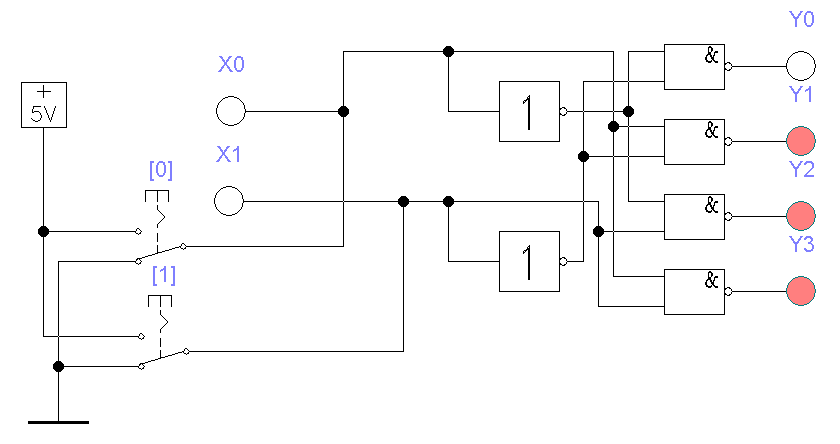

Дослідити схеми дешифраторів 2х4, реалізованих на логічних елементах І (рисунок 1.3 а), АБО (рисунок 1.3 б), АБО-НЕ (рисунок 1.3 в), І-НЕ (рисунок 1.3 г). Заповнити таблиці істинності (зразки таблиці істинності для дешифратора 2х4 наведені в таблиці 1.3) та визначити активний вихідний рівень для кожного з наведених дешифраторів.

Таблиця 1.3 – Шаблони таблиці істинності дешифратора 2х4

|

Х1 |

Х0 |

Y0 |

Y1 |

Y2 |

Y3 |

|

Х1 |

Х0 |

Y0 |

Y1 |

Y2 |

Y3 |

|

0 |

0 |

|

|

|

|

|

0 |

0 |

|

|

|

|

|

0 |

1 |

|

|

|

|

|

0 |

1 |

|

|

|

|

|

1 |

0 |

|

|

|

|

|

1 |

0 |

|

|

|

|

|

1 |

1 |

|

|

|

|

|

1 |

1 |

|

|

|

|

|

Активний вихідний рівень: |

|

Активний вихідний рівень: |

||||||||||

|

Х1 |

Х0 |

Y0 |

Y1 |

Y2 |

Y3 |

|

Х1 |

Х0 |

Y0 |

Y1 |

Y2 |

Y3 |

|

0 |

0 |

|

|

|

|

|

0 |

0 |

|

|

|

|

|

0 |

1 |

|

|

|

|

|

0 |

1 |

|

|

|

|

|

1 |

0 |

|

|

|

|

|

1 |

0 |

|

|

|

|

|

1 |

1 |

|

|

|

|

|

1 |

1 |

|

|

|

|

|

Активний вихідний рівень: |

|

Активний вихідний рівень: |

||||||||||

а

а

б

б

в

в

г

г

Рисунок 1.3 – Схеми дешифраторів на логічних елементах

Завдання 2.

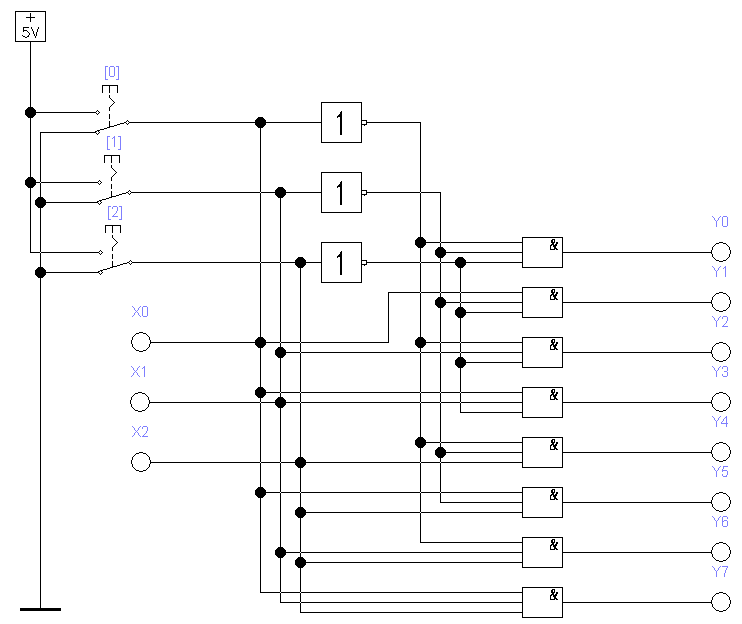

Дослідити схему дешифратора 3х8, наведену на рисунку 1.4. Заповнити таблицю істинності (зразок таблиці істинності для дешифратора 3х8 наведений у таблиці 1.4) та визначити активний вихідний рівень наведеного дешифратора.

Таблиця 1.4 – Шаблон таблиці істинності дешифратора 3х8

|

Х2 |

Х1 |

Х0 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

Активний вихідний рівень: |

||||||||||

Рисунок 1.4 – Схема лінійного дешифратора 3х8 на логічних елементах І

Підключити до схеми генератор двійкових слів та аналізатор сигналів, як показано на рисунку 1.5, і отримати часову діаграму роботи дешифратора в режимі послідовної інкрементації вхідного двійкового коду.

Рисунок 1.5 – Схема дослідження часової діаграми дешифратора

Завдання 3.

Дослідити схему пірамідального дешифратора, наведену на рисунку 1.6. Заповнити таблицю істинності (зразок таблиці істинності для дешифратора 4х16 наведено у таблиці 1.5) та визначити активний вихідний рівень дешифратора.

Рисунок 1.6 – Схема пірамідального дешифратора 4х16, побудованого на логічних елементах І

Таблиця 1.5 – Шаблон таблиці істинності дешифратора 4х16

|

Х3 |

Х2 |

Х1 |

Х0 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

Y10 |

Y11 |

Y12 |

Y13 |

Y14 |

Y15 |

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Активний вихідний рівень: |

|||||||||||||||||||