- •В.Ф. Гузик проектирование проблемно - ориентированных вычислительных систем

- •Часть 1

- •Предисловие

- •Производительность суперкомпьютеров

- •Почему в России не построили одну из самых мощных эвм в мире Компьютер завис

- •Упакованные узлы

- •Да здравствует вчерашний день

- •450 Миллионов рублей потрачено рф на создание суперкомпьютера «скиф»

- •Суперкомпьютеры помогут подтянуть экономику

- •Просто супер! «скиф» ведет в счете: суперкомпьютерный центр открылся в Белгосуниверситете

- •Подводный странник

- •Россия на пороге квантовой революции

- •Строим сами России по плечу создание национальной киберинфраструктуры

- •Вперед - за облаками! Программа "Университетский кластер" выходит на новый этап развития

- •Квантовый компьютер...

- •Глава первая. Концепция построения многопроцессорных вычислительных систем с программируемой архитектурой (мвс па)

- •Глава вторая. Организация математического обеспечения мвс с программируемой архитектурой

- •2.1. Основы математического обеспечения многопроцессорных вычислительных систем с программируемой архитектурой

- •2.2. Организация машинных языков высокого уровня и технология программирования мвс с программируемой архитектурой

- •2.3. Организация параллельных вычислительных процессов в мвс с программируемой архитектурой

- •Глава третья. Проблемно-ориентированные мвс па

- •3.1.Методика перехода от систем дифференциальных и алгебраических уравнений к системе уравнений Шеннона

- •3.1.1.Представление исходной задачи в форме, удобной для реализации на цифровых интегрирующих машинах (цим)

- •3.1.2. Методика перехода от заданных функций к системе уравнений Шеннона

- •3.1.3. Методика перехода от заданных дифференциальных уравнений к системе уравнений Шеннона

- •3.1.4.Методика перехода от систем линейных алгебраических уравнений к системе уравнений Шеннона

- •3.1.5.Получение программных матриц соединений цифровых решающих модулей

- •3.1.6.Методика перехода от программных матриц к схеме соединения цифровых решающих модулей (црм) в цим с жесткими связями

- •3.2.Примеры структурной организации вычислительного процесса в цим.

- •3.2.1.Задача №1

- •3.2.2.Задача №2

- •3.2.3.Задача №3

- •Приложение 3.2

- •3.2.4.Задача №4

- •3.2.5.Задача №5

- •Глава четвёртая. Теоретические основы построения интегрируЮщих вычислительных структур модульного типа

- •4.1. Общая структурно-логическая схема проектирования (анализа и синтеза) модульных ивс

- •4.2. Представление задач для модульных ивс в операторном пространстве

- •4.3. Построение базиса в операторном -пространстве для ивс модульного типа

- •4.4. Разработка эффективного машинного алгоритма выбора базиса в операторном -пространстве

- •4.5. Математическая модель ивс модульного типа на основе t -алгоритмов

- •4.6. Примеры, иллюстрирующие работу базовой машины ивс

- •Глава пятая. Анализ и синтез универсальных решающих блоков интегрирующих вычислительных структур (ивс)

- •5.1. Синтез алгоритма универсального решающего блока интегрирующих вычислительных структур

- •5.2. Разработка алгоритма автоматического масштабирования переменных и приращений в универсальном решающем блока ивс

- •5.3. Построение структурных схем универсальных решающих блоков ивс с автоматическим масштабированием переменных

- •5.4 Разработка алгоритма универсального решающего блока, основанного на принципе цифрового слежения и синтез его структурной схемы

- •5.5.Проектирование решающей части интегрирующих вычислительных структур

- •Глава шестая. Проектирование функциональных модулей интегрирующих вычислительных структур

- •6.1. Исследование принципов построения коммутационных систем модульных интегрирующих вычислительных структур

- •6.2. Разработка волновых каскадных коммутирующих сред для интегрирующих вычислительных структур

- •6.3. Принципы построения цифровых решающих и функциональных модулей ивс

- •6.4.Определение параметров функциональных модулей интегрирующих вычислительных структур

- •6.5.Матричное представление функциональных модулей интегрирующих вычислительных структур

- •6.6. Построение специализированного микропроцессора интегрирующей вычислительной структуры

- •Глава седьмая. Система математического обеспечения модульных интегрирующих вычислительных структур

- •7.1. Структура системы математического обеспечения модульных ивс

- •7.2. Разработка языка структурного программирования высокого уровня для модульных ивс

- •7.3.Разработка транслятора, загрузчика и диспетчера системы программного обеспечения модульных ивс

- •7.4. Построение пакета системных программ для программного обеспечения ивс

- •7.5. Организация вычислительных процессов в модульных ивс

- •Глава восьмая. Однородные цифровые интегрирующие структуры

- •8.1. Цифровые интеграторы для оцис

- •8.2. Интерполяционные и экстраполяционные, одноразрядные и многоразрядные однородные цифровые интегрирующие структуры

- •Глава девятая. Примеры проектирования проблемно- ориентированных мвс на интегрирующих структурах

- •9.1. Моделирующий вычислительный комплекс для исследования систем инерциальной навигации на основе модульных ивс

- •9.2. Применение интегрирующих вычислительных структур для реализации систем управления манипуляционными устройствами автономных роботов

- •9.3. Специализированная вычислительная система для решения задач управления с прогнозированием

- •9.4. Логико-интегрирующие вычислительные структуры

- •Приложение 1 Примерный перечень

- •Министерство образования и науки российской федерации

- •Курс «Технология программирования»

- •Практические задания

- •Курс «Интерфейсы периферийных устройств»

- •Курс «Конструкторско-технологическое обеспечение производства эвм»

- •Библиографический список

- •Оглавление

5.3. Построение структурных схем универсальных решающих блоков ивс с автоматическим масштабированием переменных

Построим структурную схему универсального решающего блока с автоматическим масштабированием. Структурная схема УРБ, реализующего алгоритм (5.24), приведена на рис. 5.1. В состав ее входят: устройство настройки на операции (УНО), блок коммутации (БК), блок управляемых регистров приращений подынтегральной функции (БУRGПФ), сумматор приращений (SM), блок накопления подынтегральной функции (БНПФ), блок хранения приращений мантиссы и порядка переменной интегрирования (БНМП), множительное устройство (ML), экстраполятор (Э), квантователь (КВ), логический блок (ЛБ), устройство контроля разрядной сетки (УКРС) и устройство автоматического масштабирования (УАМП).

В режиме ввода информации в устройство настройки на операции, представляющее собой 3-разрядный регистр, заносится код операций, в соответствии с которым это устройство осуществляет настройку УРБ на выполнение необходимой арифметической или логической операции.

Выполнение операции автоматического масштабирования в каждом решающем блоке осуществляется с помощью четырех счетчиков, введенных в состав УРБ (рис. 5.1):

![]() - счетчик

изменения порядка приращений на выходе

решающего блока;

- счетчик

изменения порядка приращений на выходе

решающего блока;

МСТ - масштабный счетчик;

![]() -

счетчик изменения порядка приращений

переменной интегрирования;

-

счетчик изменения порядка приращений

переменной интегрирования;

СТМ - счетчик обратных масштабных пульсов.

Масштабирование задачи производится на каждом шаге решения.

Процесс решения можно разбить на четыре последовательных во времени этапа.

Первый

этап – ввод. Мантисса начального значения

функции

![]() заносится

в регистр подынтегральной функции

заносится

в регистр подынтегральной функции

![]() ,

a

порядок - в регистр порядка

,

a

порядок - в регистр порядка

![]() .

Кроме того, в масштабный счетчикМСТ

заносится

величина (-Πyро),

суммируемая

с начальным значением счетчика (п-т),

в которое счетчик МСТ устанавливается

перед вводом информации подачей

потенциала стирания (ПС). После этого

масштабный счетчик принимает значение:

.

Кроме того, в масштабный счетчикМСТ

заносится

величина (-Πyро),

суммируемая

с начальным значением счетчика (п-т),

в которое счетчик МСТ устанавливается

перед вводом информации подачей

потенциала стирания (ПС). После этого

масштабный счетчик принимает значение:![]() Величина

порядка подынтегральной функции

заносится ещё и в счетчик

Величина

порядка подынтегральной функции

заносится ещё и в счетчик

![]() .

.

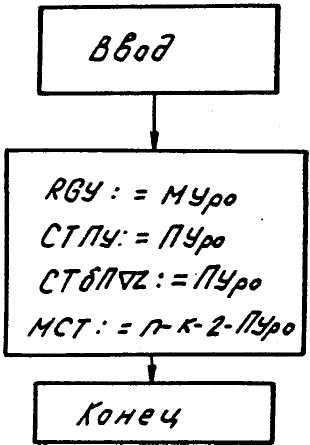

Алгоритм ввода представлен на рис. 5.2.

Рис. 5.1. Структурная

схема УРБ с АМП.

Второй

этап - передача масштабной информации.

Сначала в CTМ

заносится значение

![]() ,

то есть

,

то есть

![]() Затем

осуществляется передача масштабной

информации в обратном направлении и к

содержимому СТМ

прибавляется

минимальное значение масштабного

сигнала обратной связи, то есть в СТМ

зафиксируется

значение

Затем

осуществляется передача масштабной

информации в обратном направлении и к

содержимому СТМ

прибавляется

минимальное значение масштабного

сигнала обратной связи, то есть в СТМ

зафиксируется

значение

![]() После

этого происходит передача содержимого

После

этого происходит передача содержимого

![]() в

"последующие" УРБ, то есть выполняются

операции

в

"последующие" УРБ, то есть выполняются

операции

![]() или

или

![]() .

.

Третий

этап – начальное масштабирование. Он

заключается в том, чтобы от значения

![]() перейти

к

перейти

к![]() – заданный

шаг растения). На этапе начального

масштабирования работают только узлы,

предназначенные для автоматического

масштабирования.

– заданный

шаг растения). На этапе начального

масштабирования работают только узлы,

предназначенные для автоматического

масштабирования.

Рис. 5. 2. Алгоритм ввода начальных данных

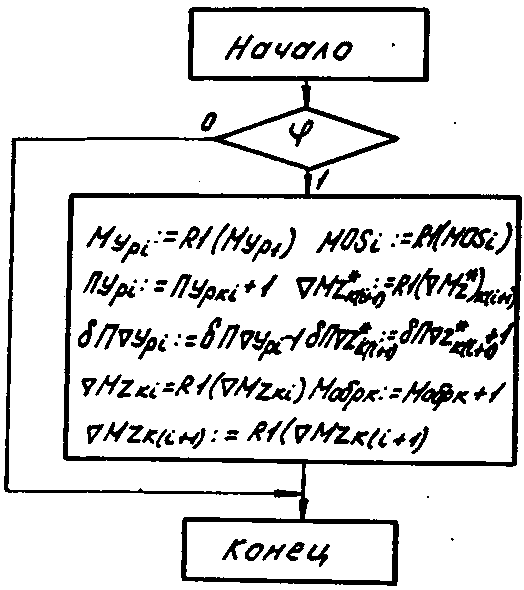

Рис 5.3. Алгоритм отработки переполнения

Четвертый этап - это непосредственное решение задачи с начальным шагом t = 2–a. В процессе решения значение t может изменяться автомати-чески или по желанию оператора.

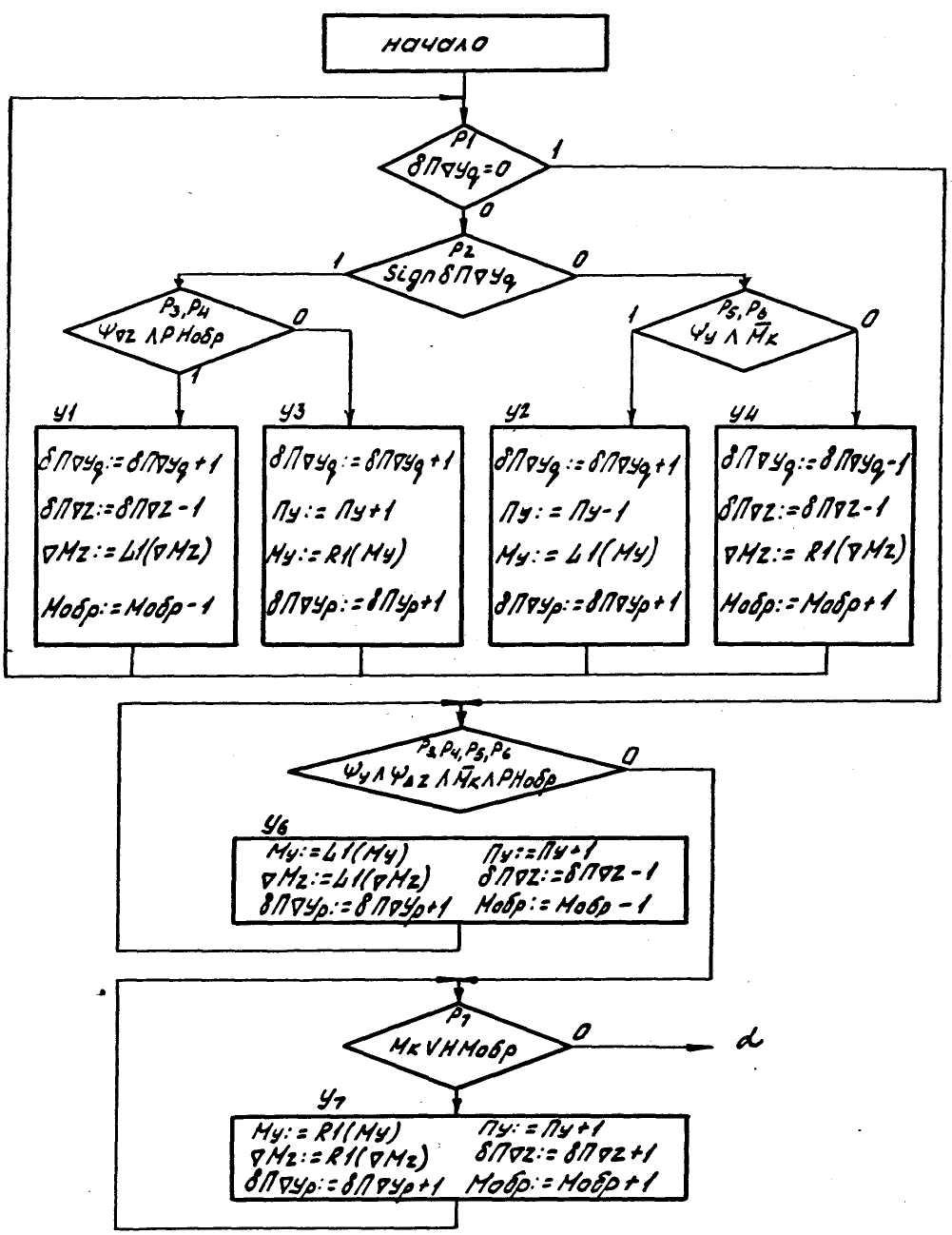

Алгоритм автоматического масштабирования, описанный системой логических уравнений (5.24), можно представить в виде графа микропрограммы, изображенного на рис. 5.4.

В

алгоритме можно выделить три уровня.

На первом уровне достигается выполнение

первых двух масштабных соотношений в

системе (5.21):![]() и

и

![]() ,

то есть происходит отработка в

ноль

приходящих

значений изменения порядка приращений

переменной интегрирования:

,

то есть происходит отработка в

ноль

приходящих

значений изменения порядка приращений

переменной интегрирования:

![]() .

Управляющие параметры:

.

Управляющие параметры:![]() На втором уровне происходит анализ

возможности увеличения разрядности

чисел, то есть осуществляется улучшение

режима вычислений. Управляющий сигнал:

На втором уровне происходит анализ

возможности увеличения разрядности

чисел, то есть осуществляется улучшение

режима вычислений. Управляющий сигнал:![]() .

На третьем уровне происходит анализ

необходимости уменьшения разрядности

чисел при входе приращения

подынтегральной

.

На третьем уровне происходит анализ

необходимости уменьшения разрядности

чисел при входе приращения

подынтегральной

Рис. 5.4. Алгоритм автоматического масштабирования

функции

за старшие разряды или приращения

интеграла за младшие разряды подынтегральной

функции "следующего" решающего

блока, то есть достигается выполнение

третьего условия системы (5.21):

![]() ,

что приводит к выработке управляющего

сигнала

,

что приводит к выработке управляющего

сигнала

![]() .

Выполнение условия

.

Выполнение условия

![]() осуществляется

на всех трех уровнях масштабирования.

осуществляется

на всех трех уровнях масштабирования.

После

осуществления оптимального изменения

разрядности чисел и достижения выполнения

всех масштабных соотношений в системе

(5.21)

выдается

сигнал окончания масштабирования,

который передается в устройство

управления. После окончания масштабирования

во

всех УРБ

в устройстве управления вырабатывается

сигнал

![]() ,

который разрешает выполнение арифметических

операций в данном шаге решения подачей

потенциала работы (ПР).

,

который разрешает выполнение арифметических

операций в данном шаге решения подачей

потенциала работы (ПР).

Схема анализа и отработки переполнений работает самостоятельно в процессе выполнения арифметических операций. При наличии переполнения осуществляется сдвиг числовой информации вправо и изменение значений RGПу, СТМ и MCT "следующего" УРБ. Алгоритм отработки переполнений приведен на рис. 5.3.

Алгоритм автоматического масштабирования пригоден как для операции интегрирования, так и для суммирования, слежения и логических операций, при этом работа УРБ в режиме суммирования или слежения выполняется только по третьему уровню алгоритма.