- •1. Комбинационные цифровые устройства, пример.

- •2. Последовательностные цифровые устройства, пример.

- •3. Модель конечного автомата, основные свойства (зависимости), примеры.

- •4. Диаграмма переходов конечного автомата.

- •5. Таблица переходов конечного автомата.

- •6. Гонки в цифровых устройствах.

- •7. Синхронизация цифровых устройств как средство устранения неопределенности, вызванной гонками.

- •8. Минимизация логических функций методом Вейча-Карно.

- •9. Минимизация логических функций методом Квайна-МакКласки.

- •10. Минимизация логических функций методом свертки таблицы истинности.

- •11. Сравнение методов минимизация логических функций.

- •12. Автоматическое управление движением с помощью конечных выключателей, пример.

- •13. Цикловая схема управления производственным механизмом, пример.

- •14. Импульсная сау на примере электронагревателя.

- •15. Блок-схема алгоритма работы регулятора на примере стабилизатора напряжения с автотрансформатором.

- •16. Пример стабилизатора напряжения с реостатом.

- •17. Электронный усилитель, график возникновения нелинейных искажений.

- •18. Катодный повторитель как пример простой схемы с отрицательной обратной связью.

- •19. P-n переход принцип работы полупроводникового диода.

- •20. Принцип работы биполярного транзистора. 21. Npn- и pnp-транзистор.

- •22. Классы работы усилителя.

- •23. Пример усилителя звуковой частоты. 24. Уменьшение искажений в усилителе с помощью отрицательной обратной связи. 25. Линейная система с отрицательной обратной связью.

- •26. Условия возникновения самовозбуждения. 27. Генератор импульсов.

- •28. Стабилизация частоты импульсов генератора.

- •29. Конструкция электромагнитного реле, условное графическое обозначение.

- •30. Различные типы контактов электроаппаратов.

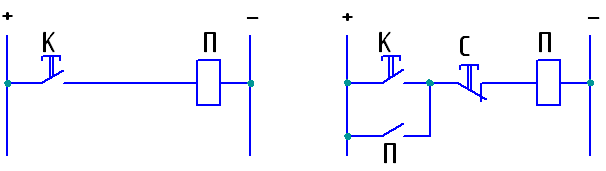

- •31. Схема с памятью для включения-отключения электродвигателя от двух кнопок.

- •38. Таблицы истинности полностью и не полностью определенные.

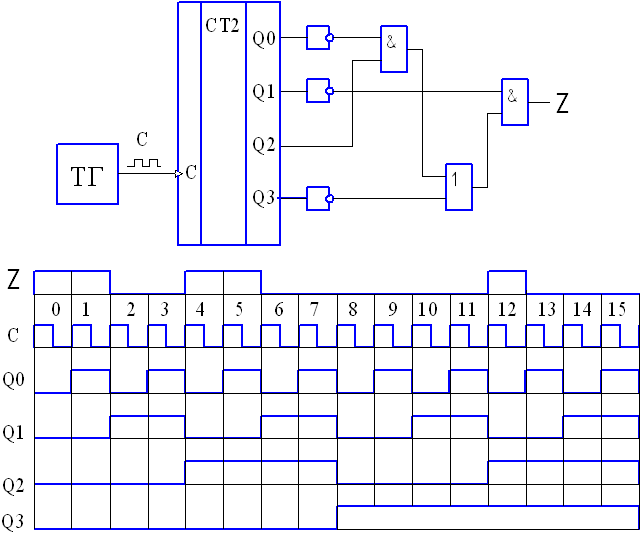

- •39. Схема синхронизации цифрового устройства на логической схеме.

- •40. Схема синхронизации цифрового устройства на дешифраторе.

- •41. Схема информационных потоков на примере микропроцессора к1804 вс1.

- •42. Определение понятий «управление, объект управления, состояние объекта управления»; примеры.

- •43. Асу, сау, асу тп; примеры.

- •44. Применение эвм для управления движением. 45. Влияние времени выполнения управляющей программы на точность остановки механизма.

- •49. Эмиттерный повторитель.

- •50. Комплементарная пара транзисторов.

- •51. Возникновение самовозбуждения усилителя на определенных частотах.

31. Схема с памятью для включения-отключения электродвигателя от двух кнопок.

Здесь

нужно только кратковременно нажать

кнопку К после чего пускатель П включит,

как и ранее, электродвигатель мощными

контактами, а еще одним контактом включит

сам себя по параллельной кнопке К цепи.

При отпускании К пускатель останется

включенным.

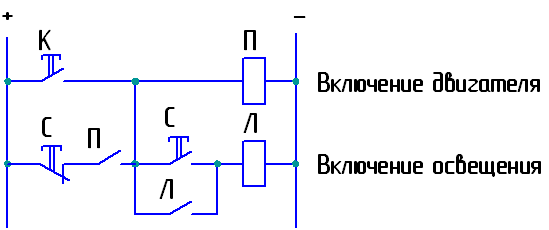

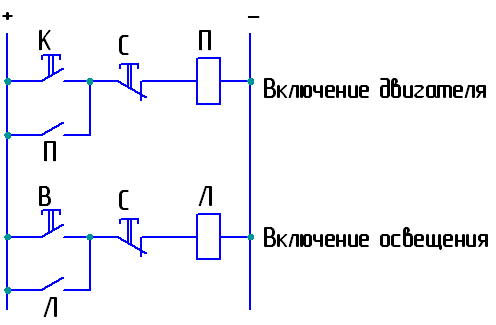

32. Схема включения электродвигателя и освещения от двух кнопок как пример неопределенности в работе.

33. Схема включения электродвигателя и освещения, свободная от неопределенности (гонок).

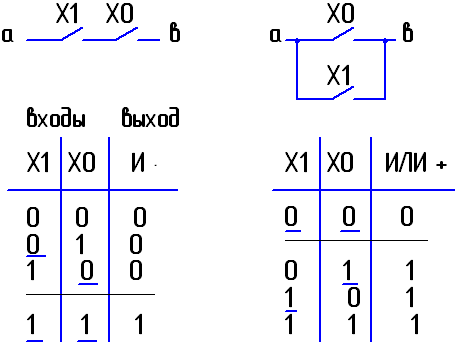

34. Логическая функция «И», таблица истинности, реализация на ключах, микросхема. 35. Логическая функция «ИЛИ», таблица истинности, реализация на ключах, микросхема.

Логическое И обозначают точкой, как умножение, а логическое ИЛИ обозначают, как сложение, знаком +.

Все

возможные случаи цепей “И” при двух

переменных Х1 и Х0 с учетом их инверсии

показаны на рисунке. Инверсия отмечена

черточкой сверху и соответствует

размыкающему (нормально замкнутому)

контакту.

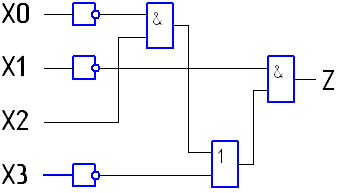

36. Построение логической схемы на ячейках И, ИЛИ, НЕ по логической функции.

Каждая подстановка промежуточной переменной в методе свертки таблицы истинности соответствует логической ячейке. В приведенном выше примере использовались логические ячейки: “И”, “ИЛИ”, “НЕ”, полученная логическая схема изображена на рисунке.

Z

= неХ1 ∙ (не Х3 + неХ0 ∙ Х2). Умножение -

логическая ячейка "И". Сложение -

логическая ячейка "ИЛИ".

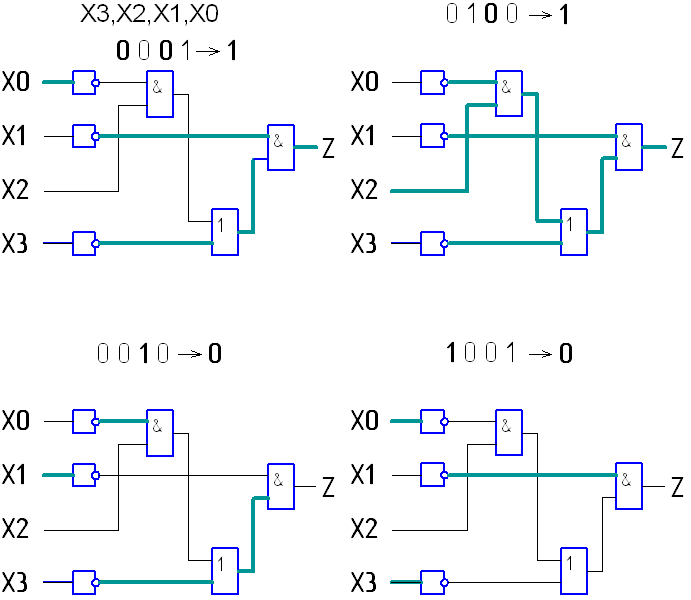

37. Анализ работы логической схемы.

Для анализа правильности схемы и функции можно проверить работу схемы, как показано на рисунке. Здесь можно руководствоваться следующими правилами:

1. в ячейке “И” низкий уровень (0 по умолчанию) с любого входа сразу проходит на выход,

2. в ячейке “ИЛИ” высокий уровень (1 по умолчанию) с любого входа сразу проходит на выход.

Для

некоторых значений входов, указанных

над рисунком в порядке Х3,Х2,Х1,Х0 показано

распространение сигнала слева направо,

при этом высокий уровень отмечен толстой

линией. Следует отметить, что жирно

отмеченные значения входов соответствуют

отмеченным значениям на таблице

истинности и являются критичными для

выхода – их изменение на противоположное

изменяет значение выхода.

38. Таблицы истинности полностью и не полностью определенные.

Не полностью определенные таблицы истинности, где для некоторых значений аргументов значение функции не определено или безразлично. Полностью определенные таблицы истинности, где для всех значений аргументов значение функции определено.

39. Схема синхронизации цифрового устройства на логической схеме.

В

качестве примера практического

использования полученной логической

схемы рассмотрим схему синхронизации

цифрового устройства, приведенную на

рисунке. Это устройство имеет цикл

работы в 16 тактов от 0 до 15. Необходимо

обеспечить синхросигнал Z

высокого уровня в тактах: 0,1,4,5,12, в

остальных тактах синхросигнал должен

быть низким. Для этого подходит полученная

ранее логическая схема, на ее входы

подаются сигналы Q

от счетчика импульсов СТ2, который

получает входные импульсы C

от тактового генератора ТГ. На рисунке

приведена диаграмма сигналов схемы

синхронизации. Краткую выборочную

проверку схемы можно провести по сигналу

Q1

– там, где он высокий, Z

должен быть низким, так как после

инвертора он низкий и сразу проходит

на выход ячейки &.