Лабораторная работа № 22. Регистры.

Цель: Изучение регистров.

Оборудование: Система моделирования Multisim.

Введение

Регистр предназначен для хранения двоичного числа (слова). Поэтому основу его составляют запоминающие элементы – триггеры. Количество триггеров определяет разрядность регистра. В каждом из них должна храниться цифра разряда числа. Кроме хранения регистр может осуществлять сдвиг принятого слова, преобразование двоичного кода из прямого в обратный (когда единицы заменяются нулями, а нули - единицами) и наоборот, логические сложение и умножение.

В общем случае регистр может выполнять следующие микрооперации над кодовыми словами:

-

установка в исходное состояние (запись нулевого кода);

-

запись входной информации в последовательной форме;

-

запись входной информации в параллельной форме;

-

хранение информации;

-

сдвиг хранимой информации вправо или влево;

-

выдача хранимой информации в последовательной форме;

-

выдача хранимой информации в параллельной форме.

Любой N- разрядный регистр состоит из N однотипных ячеек – разрядных схем, выходной сигнал каждой из которых ассоциируется с весовым коэффициентом соответствующего разряда двоичного кода. При этом каждая разрядная схема, как любое последовательное устройство, состоит из триггерной подсистемы (элемента памяти) и некоторой комбинационной схемы, преобразующей входные воздействия и состояния триггерной подсистемы в выходные сигналы регистра.

Регистры могут быть классифицированы по различным признакам. Рассмотрим основные из них.

По способу приема информации регистры подразделяют на:

Параллельные (статистические), в которых информация записывается и считывается в параллельной форме;

Последовательные (сдвиговые), в которых информация записывается и считывается в последовательной форме;

Универсальные (последовательно-параллельные), в которых информация записывается или считывается как в параллельной, так и в последовательной формах.

Последовательных приближений, для преобразования двоичного кода в аналоговый сигнал.

Параллельный регистр. Параллельный регистр предназначен для обработки информации только в параллельной форме.

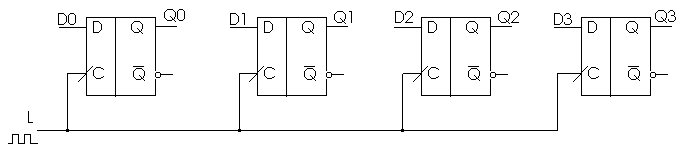

Рис.1. Схема параллельного регистра.

На рис.1. приведена схема параллельного регистра на D- триггерах. Параллельный код подается на D0 – D3. запись осуществляется при подаче логической единицы на вход С триггеров. Код снимается с выходов Q0 -Q3. таблица № 1 является таблицей истинности для данного регистра.

Табл. № 1. Таблица истинности параллельного регистра на D- триггерах.

|

D0 – D3 |

L |

Q0 |

Q1 |

Q2 |

Q3 |

Режим работы |

|

Х |

0 |

Q0-1 |

Q1-1 |

Q2-1 |

Q3-1 |

Хранение (-1 – предыдущее значение) |

|

D0 – D3 |

|

D0 |

D1 |

D2 |

D3 |

Запись |

|

Х |

1 |

D0 |

D1 |

D2 |

D3 |

Хранение |

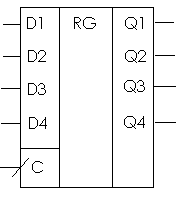

Условное изображение четырехразрядного регистра приведено на рис.2, где Q1 – Q4 – выходы разрядов регистра, D1 – D4 - входы, с которых в регистр одновременно записываются все разряды заносимого слова, С – вход, импульс на котором разрешает запись с входов D1 – D4.

Рис.2. Условное изображение регистра.

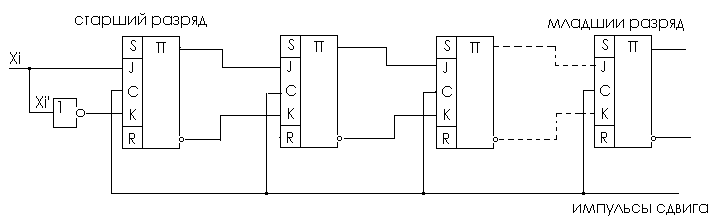

Последовательный регистр. Также последовательные регистры называют сдвиговыми - это устройство, способное хранить и сдвигать информацию каждый такт. В последовательном регистре число вводится и выводится последовательно разряд за разрядом. Разряды такого регистра соединены последовательно. Каждый разряд выдает информацию в следующий и одновременно принимает новую информацию из предыдущего. Для этого каждый разряд должен иметь два запоминающих элемента. В первый передается информация из предыдущего разряда, одновременно второй передает свою информацию в последующий разряд; затем информация, принятая первым элементом, передается во второй, а первый освобождается для приема новой информации. Двухступенчатый триггер (например, JK- триггер, D- триггер) представляет совокупность двух запоминающих элементов, поэтому он один может составлять разряд последовательного регистра. Если в цепи таких триггеров выходы одного соединить с входами другого, то по фронту тактового импульса во входную ступень каждого триггера будет заноситься информация из выходной ступени предыдущего триггера, а по спаду импульса она будет переписываться в выходную ступень. Теперь (по фронту следующего тактового импульса) во входной ступени триггера информация может быть заменена новой (из предыдущего триггера) без опасения, что предыдущая будет потеряна.

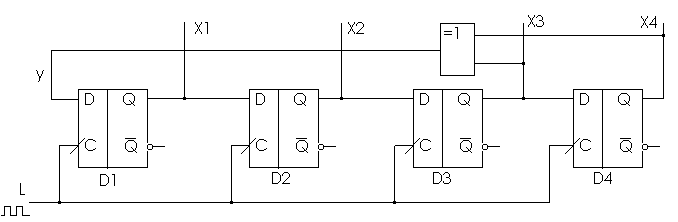

Функциональная схема последовательного регистра приведена на рис.3, где, к примеру, левый триггер предназначен для хранения старшего разряда, а правый – для хранения младшего разряда.

Рис.3. Схема последовательного регистра на JK- триггерах.

Разряды двоичного числа (в виде высоких и низких потенциалов) начиная с младшего разряда последовательно поступают на входы старшего разряда регистра. Поступление разрядов числа чередуется с поступлением импульсов сдвига, которыми вводимые разряды подвигаются вдоль регистра, пока младший разряд n- разрядного числа не окажется в младшем разряде регистра.

Для выдачи в последовательной форме записанного числа надо на входы старшего разряда регистра подать Хi =0, Xi’ =1, а на шину импульсов сдвига – n импульсов. Первый импульс выдвинет из младшего разряда регистра младший разряд числа, на его место передвинется второй разряд числа и т.д. – все число сдвинется вдоль регистра на один разряд.

Одновременно с входов в старший разряд регистра будет записан 0. второй импульс сдвига выдвинет из регистра второй разряд числа и продвинет 0 из старшего разряда регистра в соседний, более младший и т.д. После n импульсов сдвига число будет полностью выведено из регистра, в разряды которого окажутся записанными нули.

Сдвигающий регистр может быть однонаправленным (для сдвига числа в сторону младшего разряда – правый сдвиг, в сторону старшего разряда – левый сдвиг), а также реверсивным, обеспечивающим сдвиг в обе стороны.

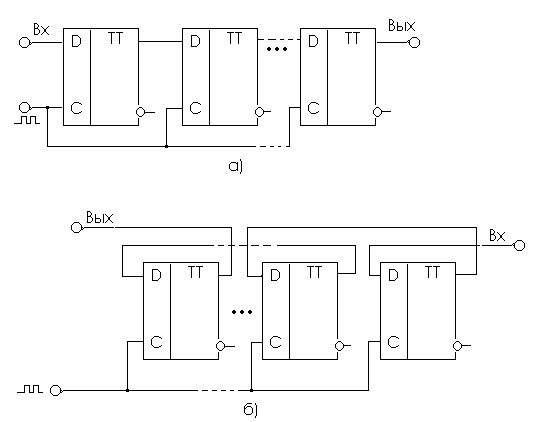

На рис.4 изображены сдвиговые регистры на D- триггерах со сдвигом слова вправо и влево.

Рис.4. Сдвиговые регистры на D- триггерах.

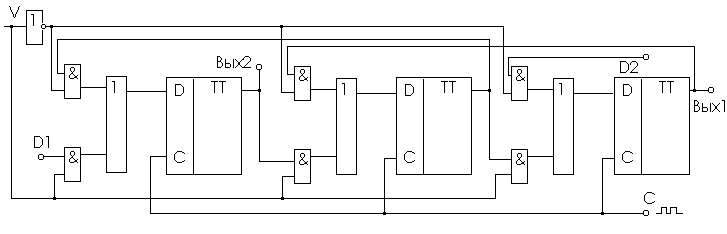

Схема реверсивного сдвигового регистра изображена на рис.5. При V =1 верхний ряд конъюнкторов заблокирован и в регистр сдвиговыми импульсами могут вдвигаться разряды слова слева направо с входа D1. При V =0 блокируется нижний ряд конъюнкторов и слово может вдвигаться в регистр с входа D2 справа налево.

Рис.5. Схема реверсивного регистра.

Универсальный регистр (параллельно-последовательный). Универсальные регистры используются, в частности, для преобразования параллельной формы кода в последовательную и наоборот. Для решения первой задачи регистр, выполненный по схеме рис.3, должен иметь триггеры с не тактируемыми входами S и R для записи слова в параллельной форме. С подачей импульсов сдвига этот код разряд за разрядом будет появляться на выходе триггера младшего разряда. При решении второй задачи число вводится в регистр последовательно разряд за разрядом, а снимается одновременно с выходов всех триггеров.

Если выходы последнего триггера (см. рис.3) соединить с входами первого, то получится кольцевой регистр сдвига. Записанная в его разряды информация под воздействием сдвигающих импульсов будет циркулировать по замкнутому кольцу. Кольцевой регистр иначе называют кольцевым счетчиком. Его коэффициент пересчета равен числу разрядов n: единица, записанная в один из разрядов, периодически появляется в нем после того, как пройдут n сдвигающих импульсов.

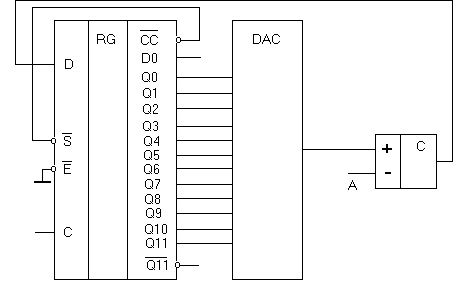

Регистр последовательных приближений. На рис.6. приведена схема работы ИС ИР17 в аналогово-цифровом преобразователе DAC по методу поразрядного взвешивания.

Рис.6. Аналогово-цифровой преобразователь на основе ИС типа ИР17.

В каждом такте преобразования регистр вырабатывает испытательный цифровой код, начиная с кода 011 … 11, который в АЦП преобразуется в аналоговый сигнал и сравнивается затем в компараторе (С) с преобразуемым аналоговым сигналом (А). Если испытательный сигнал, поступающий с цифро-аналогового преобразователя, меньше преобразуемого аналогового сигнала, компаратор вырабатывает 1, в противном случае 0. Сигнал с выхода компаратора, поступая на вход D регистра, устанавливают старший разряд регистра в состояние, соответствующее аналоговому сигналу при положительном импульсе синхронизации. Одновременно следующий, более младший разряд регистра, устанавливается в 0. Таким образом, после двух тактовых импульсов на выходе регистра устанавливается код Q11, 011 …, где Q11 – значение в старшем разряде регистра, соответствующее уровню преобразуемого аналогового сигнала.

Для

работы с ЦАП с меньшей разрешающей

способностью может быть применен

усеченный регистр. В Q регистре, кроме

прямого, предусмотрен инверсный выход

старшего разряда

![]() , который используется при представлении

биполярного аналогового сигнала в

дополнительном или обратном цифровом

коде. Для контроля поступающей в регистр

информации имеется прямой выход данных

D0. В ИС ИР17 предусмотрен асинхронный

вход

, который используется при представлении

биполярного аналогового сигнала в

дополнительном или обратном цифровом

коде. Для контроля поступающей в регистр

информации имеется прямой выход данных

D0. В ИС ИР17 предусмотрен асинхронный

вход

![]() ,

позволяющий каскадировать регистры

для получения любого числа разрядов.

,

позволяющий каскадировать регистры

для получения любого числа разрядов.

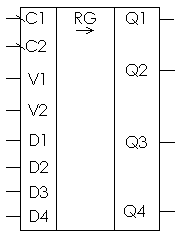

Интегральные микросхемы регистров. Отечественная промышленность выпускает многие типы регистров в интегральном исполнении. На рис.7 приведено условное изображение четырехразрядного параллельно-последовательного регистра со сдвигом вправо (микросхема серии К155).

Рис.7. Условное изображение сдвигового регистра.

Выбор режима (последовательный или параллельный ввод числа) определяется сигналом на входе V2: при логическом 0 регистр работает как сдвигающий, а при логической 1 – как параллельный.

Через вход V1 в первый разряд регистра последовательно вводятся разряды двоичного числа. Синхроимпульсы, поступающие на вход С1, обеспечивают их сдвиг.

По входам D1 – D4 в регистр может быть занесено двоичное число в параллельной форме всеми разрядами одновременно. Его запись происходит с поступлением синхроимпульса на вход С2.

В условных обозначениях регистров со сдвигом влево стрелка обращена в сторону, противоположную изображенной на рис.7, а в реверсивных сдвигающих регистрах она изображается двунаправленной.

На рис.8 показано наращивание разрядов регистра сдвига. По каждому импульсу на входе С разряды вводимого слова с входа D вдвигаются в регистр. С выхода последнего разряда (Q4) предыдущего регистра разряд слова поступает на вход D последующего, составляющих как бы непрерывную цепочку последовательно включенных триггеров.

Рис.8. Наращивание разрядности регистра.

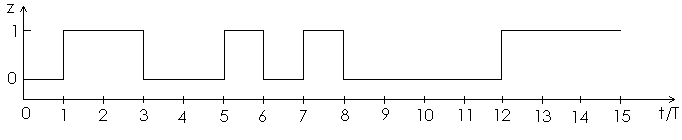

Получение псевдослучайных последовательностей. Для анализа аналоговых и цифровых систем часто необходимы случайные последовательности сигналов. Их можно генерировать, подключив, например, естественный источник шумового напряжения к входу триггера Шмидта. При этом получаются двоичные выходные сигналы со статистическим распределением. Такая последовательность представлена на рис.9.

Рис.9. Двоичная случайная последовательность.

Видно, что распределение временных интервалов логических единиц и нулей произвольное, т.е. в их последовательности не наблюдается никакой закономерности. Если такая последовательность повторяется через определенный интервал времени, то она называется псевдослучайной. Система не может отличить псевдослучайную последовательность от истинно случайной, если число периодов в последовательности превышает емкость ее памяти. Это условие в большинстве случаев выполняется легко.

Большое преимущество псевдослучайных последовательностей заключается в том, что получаются воспроизводимые результаты и возможно снятие осциллограмм. Кроме того, псевдослучайные последовательности для низкочастотного диапазона (1 МГц) получить значительно легче, чем при использовании большинства естественных источников шума.

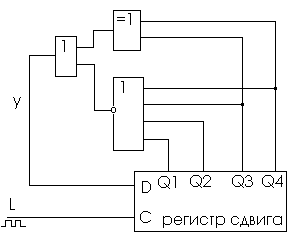

Для генерации псевдослучайных последовательностей применяют регистр сдвига, в который определенным образом вводится обратная связь. Обратная связь создается на основе элементов «исключающее ИЛИ».

Апериодические кодовые последовательности, которые может генерировать n- разрядный регистр сдвига, имеют разрядность N = 2n – 1 бит. С помощью четырех- разрядного регистра сдвига можно, следовательно, получить псевдослучайную последовательность с максимальной длиной 15 бит (15 различных состояний). Подобная схема представлена на рис.10.

Рис.10. Генератор псевдослучайных последовательностей с n = 4 бит.

Для

объяснения принципа действия генератора

предположим, что регистр сдвига находится

в состоянии Х1 =1 и Х2 =Х3 =Х4 =0. При поступлении

первого тактового импульса информация

сдвигается на разряд вправо. Так после

окончания тактового импульса y =Х3

![]() Х4 =0, то первый каскад устанавливается

в нуль. После первого тактового импульса

получаем состояние Х2 =1 и Х1 =Х3 =Х4 =0.

Поскольку у в этом случае еще остается

равным нулю, то после второго тактового

импульса в регистр сдвига опять будет

введен нуль. После второго тактового

импульса получим состояние Х3 =1 и Х1 =Х2

=Х4 =0. Но теперь у =1. В результате в

следующем такте будет вводится единица,

т.е. Х1 =Х4 =1 и Х2 =Х3 =0. Продолжение цикла

становится ясным из таблицы № 2. Понятно,

что 15-й тактовый импульс опять устанавливает

исходное состояние. Естественно, что

цикл может начаться с любого другого

кода, в том числе и с запрещенного

состояния 000, которое блокирует схему.

Необходимо, следовательно, воспрепятствовать

появлению этого кода при включении или

сбое. Для этого можно применить логическое

устройство, показанное на рис.11.

Х4 =0, то первый каскад устанавливается

в нуль. После первого тактового импульса

получаем состояние Х2 =1 и Х1 =Х3 =Х4 =0.

Поскольку у в этом случае еще остается

равным нулю, то после второго тактового

импульса в регистр сдвига опять будет

введен нуль. После второго тактового

импульса получим состояние Х3 =1 и Х1 =Х2

=Х4 =0. Но теперь у =1. В результате в

следующем такте будет вводится единица,

т.е. Х1 =Х4 =1 и Х2 =Х3 =0. Продолжение цикла

становится ясным из таблицы № 2. Понятно,

что 15-й тактовый импульс опять устанавливает

исходное состояние. Естественно, что

цикл может начаться с любого другого

кода, в том числе и с запрещенного

состояния 000, которое блокирует схему.

Необходимо, следовательно, воспрепятствовать

появлению этого кода при включении или

сбое. Для этого можно применить логическое

устройство, показанное на рис.11.

Табл.№ 2. Таблица состояний 4- разрядного генератора псевдослучайных последовательностей.

|

L |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

|

Х1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

|

Х2 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

Х3 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

Х4 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

|

у |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

Рис.11. Логическая схема защиты для генератора

псевдослучайных последовательностей.

При появлении состояния 0000 на выходе элемента ИЛИ-НЕ устанавливается «1». Эта единица подается на вход регистра сдвига через элемент ИЛИ. Так как в нормальном режиме состояние 0000 не возникает, введенные дополнительные логические элементы не нарушают процесса функционирования.

Совершенно безразлично, с какого выхода снимается псевдостатическая последовательность, поскольку та же самая последовательность поступает с временным сдвигом с каждого выхода.

Для получения последовательности большей длины нужно использовать регистр сдвига соответствующей разрядности. Для 10- разрядного регистра длина периода составляет 1023 тактовых импульса, для 20- разрядного – 1048575. чтобы действительно достичь максимальной длины периода N = 22 –1, необходимо подключить логические схемы цепей обратной связи к строго определенным выходам, во всяком случае к выходу последнего разряда. Какие еще выходы должны быть использованы в линиях обратной связи, зависит от разрядности регистра сдвига. Для построения цепей обратной связи применяются логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, которые соединяются так, как показано на рис.12. При этом используют столько элементов, сколько необходимо для получения требуемого числа входов.

Рис.12. Схема ИСКЛЮЧАЮЩЕЕ ИЛИ

на четыре входа

Количество таких входов и то, к каким разрядам они должны быть подключены для регистра сдвига с числом разрядов от 3 до 20, можно определить из таблицы 3. Для простоты рассмотрим только один случай. Для каждого заданного решения с точкой подсоединения Хi существует симметричное ему решение с точкой подключения Хn-i. Последняя точка подключения Хn получается при этом естественно. Вместо точек 3, 5, 7, 8 можно, следовательно, использовать также 1, 3, 5, 8. Часто также имеются и другие комбинации, которые дают максимальный период (см. табл.№ 2).

Табл. № 3. Таблица исключения обратной связи.

|

n |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

|

|

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

17 |

18 |

19 |

20 |

|

|

2 |

3 |

3 |

5 |

4 |

7 |

5 |

7 |

9 |

11 |

10 |

13 |

14 |

14 |

14 |

11 |

18 |

17 |

|

|

|

|

|

|

|

5 |

|

|

|

8 |

6 |

8 |

|

13 |

|

|

17 |

|

|

|

|

|

|

|

|

3 |

|

|

|

6 |

4 |

4 |

|

11 |

|

|

14 |

|

Так как для всех схем состояние 0000… исключается, а все другие комбинации встречаются, то на выход в течении 0,5 * 2n тактов поступает единица, а в течении 0,5 * 2n- 1 тактов – нуль. Таким образом, вероятность получить в каком-либо такте единицу тем ближе к 50%, чем больше разрядность регистра.

На выходе состояние может не изменяться на 1, 2, 3,…, n тактах. Каждый такой участок последовательности встречается по крайней мере один раз, однако частота их появления убывает с ростом длительности.