Лабораторная работа № 21.

Синхронные счетчики.

Цель: Изучение синхронных счетчиков.

Оборудование: система моделирования Multisim.

Введение

Счётчик предназначен для счёта поступающих на его вход импульсов, в интервале между которыми он должен хранить информацию об их количестве. Поэтому счётчик состоит из запоминающих ячеек – триггеров.

Между собой ячейки счетчика соединяются таким образом, чтобы каждому числу импульсов соответствовали единичные состояния определённых ячеек. При этом совокупность единиц и нулей на выходах n ячеек счётчика представляет собой n-разрядное двоичное число, которое однозначно определяет количество прошедших на входе импульсов. Поэтому ячейки счётчика называют его разрядами.

Каждый разряд счетчика может находиться в двух состояниях. Число устойчивых состояний, которое может принимать данный счётчик, называют его ёмкостью, модулем счёта или коэффициентом пересчёта.

Разряд

А

Разряд

В Разряд

С

т

актовые

имп. Ррр

актовые

имп. Ррр

а) асинхронный счетчик

Комбинаторная схема

тактовые

и

Разряд

А Разряд

В Разряд

С

мпульсы

мпульсы

б) синхронный счётчик

Рис.1.Общий вид счётчиков.

Счётчики подразделяют на синхронные, у которых разряды делителей синхронизируются поступающим извне тактовыми импульсами, и на асинхронные, у которых каждый данный разряд синхронизирует следующий разряд деления. На рис.1 схематически изображено строение синхронного и асинхронного счётчиков. В асинхронных двоичных счётчиках между фронтом тактового импульса и моментом переключения разряда делителя в цепочке существует определённый временной интервал (задержка), т.е. фонт тактового импульса не совпадает с моментом переключения разряда делителя.

Отличительная особенность синхронного счётчика состоит в том, что фронты импульсов когерентны, т.е. фонты импульсов делителя всегда синхронны с фронтами тактовых импульсов.

Синхронные счётчики.

Ко всем разрядам такого счётчика информация о состоянии предыдущих разрядов поступает параллельно, также одновременно поступают к ним счётные импульсы. При этом переключающиеся разряды переходят в новые состояния одновременно. Переключение их в нужной последовательности обеспечивается логическими цепями, которые при поступлении входного импульса одни триггеры удерживают от переключения, а другим разрешают переключиться. Триггеры такого счётчика, кроме счётного, должны иметь информационные входы, на которые поступают разрешения или запреты с логических цепей.

Суммирующий счётчик с параллельным переносом. Очередной разряд суммирующего счётчика должен переключаться входным импульсом в 1, когда все предыдущие разряды уже находятся в этом состоянии. Такое условие выполняется, если на информационный вход каждого триггера подать конъюнкцию сигналов с прямых выходов предыдущих триггеров. Действительно, с конъюнктора на информационный вход триггера поступит разрешающая переключение «1», и по сигналу на счётном входе он переключится.

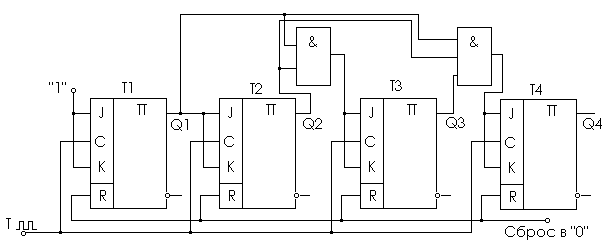

На рис.2 представлена функциональная схема четырехразрядного счётчика с параллельным переносом на JK- триггерах. На тактовые входы С всех триггеров счётные импульсы поступают одновременно со входа Т. Информационные входы J и K каждого триггера объединены. Триггер Т1 переключается каждым счётным импульсом, так как на его входы J и K постоянно подается «1». Остальные триггеры переключаются счётными импульсами при следующих условиях: Т2 – при Q1 = 1; Т3 – при Q1 = 1, Q2 =1; Т4 – при Q1 = 1, Q2 = 1, Q3 = 1.

Рис.2. Схема счётчика на JK- триггерах.

Недостатком описанного счётчика является необходимость иметь конъюнкторы с большим количеством входов, число которых должно возрастать с увеличением числа разрядов.

Количество входов конъюнктора ограничено. Поэтому в многоразрядных счётчиках используют конъюнкторы с небольшим числом входов, которыми составляют многовходовые. На рис.3 изображена функциональная схема уже рассмотренного счётчика, содержащая двухвходовые конъюнкторы. Элементы И1 и И2 составляют трёхвходовой конъюнктор, а элементы И1, И2, И3 – четырёхвходовой. За счёт последовательного включения конъюнкторов увеличивается время распространения логической единицы – сигнала, разрешающего переключение, т.е. уменьшается быстродействие счётчика. Однако время задержки сигнала логическим элементом в несколько раз меньше, чем триггером, поэтому выигрыш в быстродействии по сравнению со счётчиком с последовательным переносом всё равно будет существенным.

Рис.3. Схема счётчика на JK- триггерах.

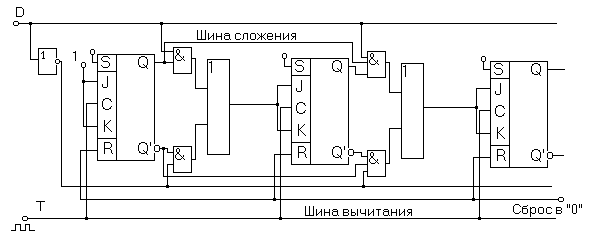

Реверсивный счётчик с параллельным переносом. Такой счётчик должен работать как на сложение, так и на вычитание. В суммирующем счётчике каждый последующий триггер получает информацию с прямого выхода предыдущего, а в вычитающем – с инверсного выхода, т.е. для перехода от сложения к вычитанию и обратно надо изменять подключение счетного входа последующего триггера к выходам предыдущего.

Такая программа реализуется в схеме реверсивного счетчика (рис.4). До некоторой степени эта схема аналогична схеме суммирующего счетчика (см. рис.3): на объединённые входы J и K каждого триггера подаётся конъюнкция сигналов с выходов предыдущих триггеров. Разница состоит в том, что входы J и K каждого триггера через дизъюнктор могут присоединяться к основному выходу предыдущего триггера (через конъюнктор верхнего ряда) или к инверсному выходу (через конъюнктор нижнего ряда).

Рис.4 Синхронный реверсивный счётчик на JK- триггерах.

Чтобы осуществить сложение, на шину сложения с входа D подается 1, которой вводятся в действие конъюнкторы верхнего ряда. При этом на шине вычитания присутствует 0, за счёт чего конъюнкторы нижнего ряда выключены. Вычитание осуществляется при D = 0, т.е. с подачей 1 на шину вычитания и 0 на шину сложения. Счётные импульсы поступают на вход Т.

Каждый триггер переключается по тактовому входу С при J =K =1, что имеет место, когда на выходах всех предыдущих триггеров (на прямых - при сложении, на инверсных – при вычитании) будут единицы. Как следует из изложенного ранее, это является условием правильной работы счётчиков в натуральном двоичном коде.

Пусть, к примеру, в счётчик, установленный на сложение, записано число 1002 =410 (Q3 =1, Q2 =Q1 =0). Так как при этом предыдущими разрядами обеспечивается J3 =K3 =0, J2 =K2 =0 и постоянно J1 =K1 = 1, то первый счётный импульс может переключить только первый разряд. Вслед за этим с выхода Q1 на входы J2, K2 поступит 1, поэтому второй счётный импульс установит в 1 второй разряд и сбросит в 0 первый. Далее процесс счёта протекает аналогично и с приходом на вход каждого счётного импульса регистрируемое в счётчике число возрастает на единицу.

Пусть при тех же условиях (Q3 =1, Q2 =Q1 =0) счётчик устанавливается в режим вычитания. Теперь входы J и K каждого триггера получают информацию с инверсного выхода предыдущего, т.е. сейчас J3 =K3 =1, J2 =K2 =1, J1 =K1 =1. Поэтому первый счётный импульс переключит все рассматриваемые разряды, установив Q3 =0, Q2 =Q1=1, т.е. уменьшив предварительно записанное в счетчик число на единицу. Аналогично действует каждый входной импульс.

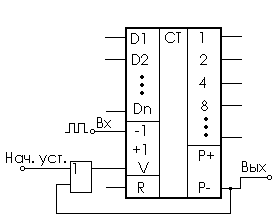

На рис.5 а) приведено условное изображение одного из типов реверсивных счётчиков. На входы +1, -1 подают счетные импульсы соответственно в режимах сложения и вычитания. Через входы предварительной записи D0 – D3 в счётчик может быть записано число. Такая запись осуществляется с поступлением импульса на вход разрешения L. Выводы 1, 2, 4, 8 – выходы разрядов счетчика, цифры указывают на вес каждого из них.

Рис.5 Условное изображение реверсивного счётчика.

На вход прямого переноса (Р+) проходит импульс с входа +1, осуществивший обнуление счетчика. Он может быть записан в другой счетчик с тем, чтобы не потерять информацию о числе импульсов, прошедших на вход обнулившегося счетчика. Так, например, девять импульсов на входе предварительно обнуленного десятичного счетчика (с емкостью, равной десяти) устанавливают в 1 все его разряды. Десятый импульс вновь обнуляет счетчик, и с выхода Р+ единица переносится во второй десятичный счетчик, в котором вес ее равен десяти.

Импульс, поступающий на вход –1 после обнуления счетчика в режиме вычитания, устанавливает в 1 все его разряды и проходит на выход обратного перехода (займа) Р-, с которого можно вычесть единицу с другого счетчика и тем самым не исказить результат. Пусть, к примеру, в первый десятичный счетчик было исходно занесено число 9, а во второй, последовательно соединенный с ним, - 2, т.е. полное число составляло 29. Девятым импульсом на входе -1 первый счетчик обнулится, десятый импульс вновь запишет в него 9, а с выхода Р- из второго счетчика спишется единица – в двух счетчиках останется число 19, что соответствует разности 29-10.

В условных обозначениях конкретных типов счетчиков выходы переносов маркируют знаками , и стоящими рядом числами. Так, у десятичного счетчика символы Р+ и Р- заменяются соответственно на 9 и 0 (рис.5, б), а двоичного счетчика с Ксч = 16 на 15 и 0 (рис.5, в).

Счетчик с входами прямого и обратного счета. Некоторые реверсивные счетчики имеют один счетный вход, на который поступают импульсы как при сложении, так и при вычитании. При этом выбор режима осуществляется соответствующим потенциалом на специальном входе. По такому принципу построена схема на рис.4.

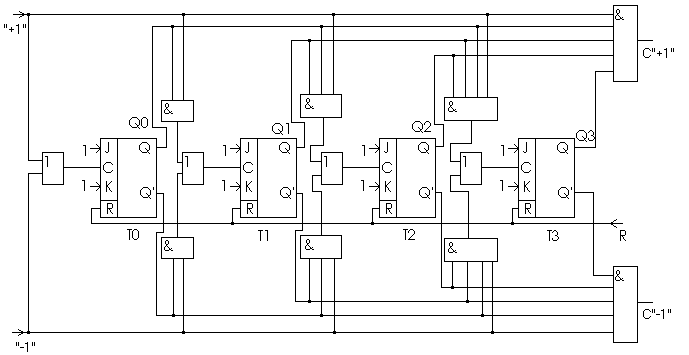

Но часто требуется счетчик, имеющий два входа. Импульс, поступающий на вход «+1», должен увеличивать результат счета; импульс, поступающий на вход «-1», должен его уменьшать. Схема, выполняющая эти функции, показана на рис.6.

Рассмотрим сначала импульс, поступающий на вход «+1». Очевидно, что благодаря наличию предшествующих логических элементов И тактовый импульс поступает только на те триггеры, для которых все предыдущие разряды находятся в состоянии 1. это является условием функционирования для суммирующего счетчика.

Рис.6. Реверсивный двоичный счетчик.

Теперь рассмотрим, что происходит в случае, когда импульсы поступают на вход «-1». Код на выходах Q’ определяет те вентили И, которые пропускают импульсы счета. Таким образом, импульсы поступают на тактовые входы только тех триггеров, которые находятся в состоянии 0. Это и есть условие обратного счета.

На триггеры, которые должны переключаться, тактовые импульсы поступают практически одновременно. Триггеры в старших разрядах переключаются одновременно с триггерами в младших разрядах. Следовательно, схема работает как синхронный счетчик. Логические элементы И на выходе определяют перенос в прямом и обратном направлениях. Можно присоединить идентичный счетчик, который является синхронным, но по сравнению с первым работает с задержкой, т.е. асинхронно. Этот способ организации называют полусинхронным (параллельно-последовательным).

Недвоичные счетчики. Счетчики, структура которых была рассмотрена ранее, являются двоичными. После поступления на вход двоичного счетчика 2n импульсов он обнуляется, т.е. емкость такого счетчика Ксч = 2n (где n – число разрядов).

Недвоичный счетчик имеет емкость, меньшую 2n, т.е. он обнуляется серией импульсов, число которых меньше 2n. Недвоичные счетчики применяются обычно как делители частоты с коэффициентом деления Ксч не равным 2n.

При проектировании недвоичного счетчика вначале определяют количество его разрядов n так, чтобы 2n было большим ближайшим к Ксч числом. Затем тем или иным методом исключают избыточные состояния счетчика, число которых равно 2n – Ксч. Так, для построения делителя частоты с Ксч = 5 нужно взять три триггера: 22 < 5 > 23. При этом количество избыточных состояний 8 – 5 = 3.

Счетчик с удержанием разрядов от переключения. Этот принцип исключения избыточный состояний состоит в том, что в зависимости от требуемого значения Ксч некоторые разряды счетчика удерживаются от переключения. На рис.7 приведена функциональная схема делителя частоты с Ксч =3, соответствующая этому принципу и полученная при использовании специальной процедуры, разработанной для синтеза недвоичных счетчиков.

Рис.7. Функциональная схема делителя частоты с Ксч =3.

В исходном состоянии триггеры Т1, Т2 обнулены: Q1 =Q2 =0 (Q1’ =Q2’ =1). Первый входной импульс на входе Т переключает триггер Т1, так как на его входах присутствует единицы: на входе К1 – постоянно, а на входе J1 – с выхода Q2’. Триггер Т2 первым входным импульсом не переключается, так как в это время на его входе J2 присутствует 0. Данное состояние счетчика соответствует второй строке переключательной табл.1, в которой каждое состояние разрядов (Q1, Q2, Q1’, Q2’) показано после окончания на входе Т n-го импульса.

Табл. № 1. Переключательная таблица к рис.7.

-

n

Q1(J2)

Q2

Q2’(J1)

0

0

0

1

1

1

0

1

2

0

1

0

3

0

0

1

Второй входной импульс переключает оба триггера, так как перед его поступлением на входах каждого присутствуют единицы: J1 =Q2’ =1; J2 =Q1 =1. После этого Q1 =0, Q2 =1. Третий входной импульс не может изменить состояния триггера Т1, так как он удерживается от переключения нулем, поступающим с выхода Q2’ на вход J1, но переключает в 0 триггер Т2, чему соответствуют потенциалы на его входах: J2 =Q1 =0, K2 =1. Таким образом, третьим входным импульсом делитель возвращается в исходное состояние (Q1 =0, Q2 =0), а на его выходе (Q2) появляется перепад 1/0, свидетельствующий о том, что на выходе прошло три импульса (три таких перепада).

Счетчик с устанавливаемым коэффициентом деления. У такого делителя можно менять коэффициент пересчета, не нарушая установленных связей между триггерами разрядов. Выполняется он на счетчике, имеющем входы предварительной записи (рис.8).

Н а

выход переноса Р+ походит входной

импульс, осуществляющий обнуление

(переполнение) счетчика, а на выход заема

Р- -входной импульс, поступающий вслед

за осуществившем обнуление.

а

выход переноса Р+ походит входной

импульс, осуществляющий обнуление

(переполнение) счетчика, а на выход заема

Р- -входной импульс, поступающий вслед

за осуществившем обнуление.

Так как в данном случае задействован выход заема, то с учетом предыдущего замечания коэффициент деления N =K +1, а K =N –1 – число, которое должно быть

предварительно занесено в счетчик по входам D1 –Dn.

С приходом на вход разрешения предварительной записи (V) импульса «Начальная установка» двоичный код числа K записывается в счетчик.

Входные импульсы на вычитающем входе уменьшают содержимое счетчика. Когда на вход поступят K =N –1 импульсов, счетчик обнулится. Следующий N –й входной импульс пройдет на выход Р- (на выход делителя), а также на вход V, вновь разрешая занесение в счетчик числа N –1. таким образом, N импульсам на входе будет соответствовать один импульс на выходе.

Изменяя предварительно заносимое в счетчик число K, можно менять коэффициент деления N.

Аналогично можно организовать делитель с коэффициентом N, подавая входные импульсы на вход суммирования и связывая с входом V выход переноса Р+. При этом по входам D1 –Dn должно быть занесено число K =C –N, где С – емкость счетчика (количество входных импульсов, поданных на обнуленный счетчик, которым он вновь обнуляется).

Десятичные счетчики. Особое место среди недвоичных счетчиков занимают десятичные (декадные) счетчики, имеющие коэффициент пересчета Ксч = 10. Десятичный счетчик позволяет индицировать число поступающих импульсов в привычном десятичном коде. Для получения указанного значения Ксч такой счетчик содержит четыре триггера, избыточные состояния которого исключаются тем или иным способом.

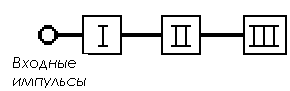

На рис.9 изображена структурная схема счетчика, состоящего из трех последовательно соединенных десятичных счетчиков (декад) I, II, III.

Рис.9 Структурная схема счетчика.

Информация о каждом из девяти импульсов накапливается в декаде; десятым импульсом она обнуляется, и I переписывается в следующую декаду. Следовательно, декада I обнуляется каждым десятым входным импульсом, II – каждым сотым, III – каждым тысячным. Если на вход Т счетчика прошло, к примеру, 283 импульса, то декада I обнуляется 28 раз, после чего в нее еще записывается число 3; в декаду II переносится 28 единиц, которыми она обнуляется два раза, после чего в нее еще окажется записанным число 8; в декаду III из декады II переносятся две единицы.

Таким образом, в каждую декаду в двоичном коде записано число, соответствующее цифре в разряде десятичного числа. Такая система представления чисел называется двоично-десятичной. В этой системе число 283 записывается как 0010 1000 0011, где сохранены позиции десятичных разрядов.

К выходам триггеров каждой декады можно присоединить дешифратор и индикатор, с помощью которых двоичное число индицируется в десятичном коде.

В приведенном примере занесения в счетчик числа 283 предполагалось, что каждая декада работает в натуральном двоичном коде, т.е. с весами двоичных разрядов (начиная со старшего), соответственно равными 8, 4, 2, 1. В этом случае говорят, что декада работает в коде 8-4-2-1. Десятичные счетчики могут выполняться и с другими весами разрядов (могут работать в других кодах).

Наращивание разрядности счетчика. Для получения такого эффекта, повышающего емкость счетчика (коэффициент пересчета делителя), счетчики соединяют последовательно. Рис.9 иллюстрирует такое соединение.

При наращивании разрядности конкретных счетчиков схема соединений, изображенная на рис.9, может усложняться дополнительными элементами и связями.

Рис.9. Наращивание разрядности счетчика.