ЛАБОРАТОРНАЯ РАБОТА №0.

ДЕШИФРАТОР

Цель работы

Изучение схемотехники цифровых дешифраторов

Оборудование

Multisim 2001

Введение

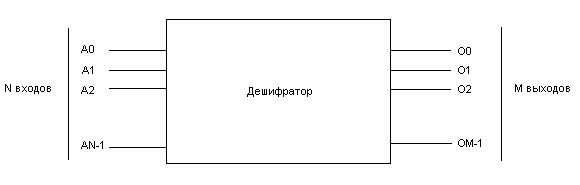

Дешифратором или декодером (decoder)

называется логическая схема, на входы

которой поступает исходных данных в

виде двоичного кода, возбуждающего

(активизирующего) только один выход,

соответствующий двоичному числу на

входе. Проще говоря, дешифратор следит

за комбинацией битов на входе, определяет,

какое двоичное число они составляют, и

затем возбуждает сигнал на том выходе,

который соответствует входной комбинации

битов; все остальные выходы в это время

не работают, На упрощенной блок-схеме

дешифратора (рис. 1.1) показаны N входов

и М выходи. Каждый из N входов

может находиться в нулевом или единичном

состоянии, но всего существует 2N

доступных входных комбинаций или кодов.

Для каждой из комбинаций будет

активизирован только один из М выходов,

т.е. с него будет сниматься сигнал с

высоким уровнем напряжения, на

остальных же выходах будет наблюдаться

низкий уровень сигнала. Многие

дешифраторы спроектированы таким

образом, что имеют выходы, для которых

активным будет сигнал с низким уровнем

напряжения, в то время как на остальных

выходах будут сигналы с высоким. Такой

дешифратор можно отличить по маленьким

кружкам на выходах, обозначающим

инверсию.

Рис. 1.1. Общая блок-схема дешифратора

Некоторые дешифраторы имеют один или несколько разрешающих входов Е (от английского слова ENABLE – разрешать), которые используются для управления работой дешифратора. Нормальная работа происходит при разрешении от всех входов. Если разрешения нет, то все выходы переводятся в неактивное состояние независимо от поступающего кода. Дешифраторы, имеющие вход разрешения часто называют декодером – демультиплексором.

Существуют и несколько иные устройства также называемые дешифраторами. Примером может служить преобразователь двоичного кода в код управления семисегментным индикатором. В этом случае активный уровень присутствует не на одном выходе, а одновременно на нескольких.

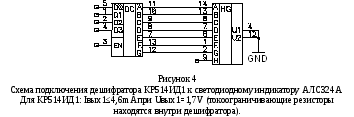

Примеры условных обозначений дешифраторов и способы включения семисегментных индикаторов показаны на рисунках:

Рисунок 3

Схема подключения дешифратора КР514ИД2

к светодиодному индикатору АЛС324Б. Для

КР514ИД2: Iвых0≤20mA

при Uвых0=0,4V

Наращивание размерности дешифратора

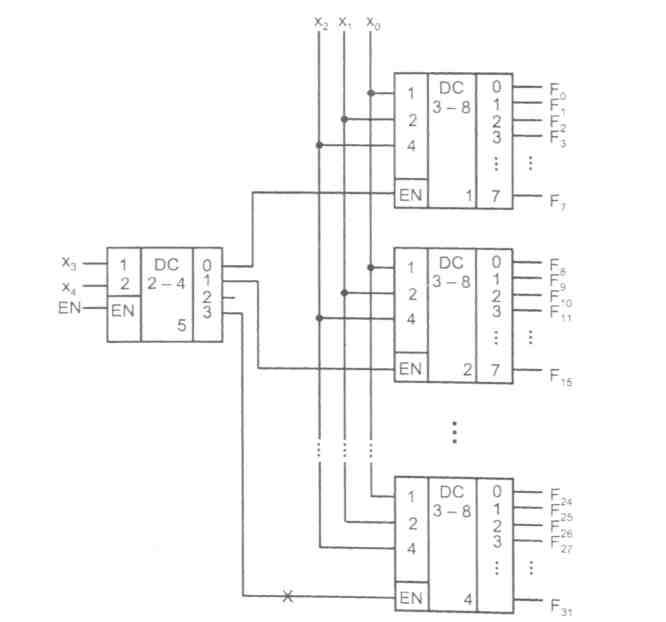

Малоразрядность стандартных дешифраторов ставит вопрос о наращивании их разрядности. Из малоразрядных дешифраторов можно построить схему, эквивалентную дешифратору большей разрядности. Для этого входное слово делится на поля. Разрядность поля младших разрядов соответствует числу входов имеющихся дешифраторов. Оставшееся поле старших разрядов служит для получения сигналов разрешения работы одного из дешифраторов, декодирующих поле младших разрядов.

В качестве примера на рис. 1.2 приведена схема дешифрации пятиразрядного двоичного кода с помощью дешифраторов "3-8" и "2-4". Для получения нужных 32 выходов составляется столбец из четырех дешифраторов "3-8". Дешифратор "2-4" принимает два старших разряда входного кода. Возбужденный единичный выход этого дешифратора отпирает один из дешифраторов столбца по его входу разрешения. Выбранный дешифратор столбца расшифровывает три младших разряда входного слова.

Каждому входному слову соответствует

возбуждение только одного выхода.

Например, при

дешифрации слова

![]() =

=

![]() =

=

![]() на входе дешифратора первого

яруса имеется код 11, возбуждающий его

выход номер три (показано крестиком),

что разрешает работу DC4.

На входе DC4 действует код

001, поэтому единица появится на его

первом выходе, т. е. на 25 выходе схемы в

целом, что и требуется.

на входе дешифратора первого

яруса имеется код 11, возбуждающий его

выход номер три (показано крестиком),

что разрешает работу DC4.

На входе DC4 действует код

001, поэтому единица появится на его

первом выходе, т. е. на 25 выходе схемы в

целом, что и требуется.

Общее разрешение или запрещение работы схемы осуществляется по входу EN дешифратора первого яруса.

Рис. Схема наращивания размерности двоичного дешифратора

Практическое задание

1. Разработайте и реализуйте в Multisim 2001 схему дешифратора в соответствии с одной из приведенных таблиц истинности, используя предложенный набор логических элементов.

-

Активный уровень на выходе - 1

|

Входы |

Выходы |

|||||||||

|

I2 |

I1 |

I0 |

Q7 |

Q6 |

Q5 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

-

Активный уровень на выходе - 0

|

Входы |

Выходы |

|||||||||

|

I2 |

I1 |

I0 |

Q7 |

Q6 |

Q5 |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

2. Разработайте и реализуйте в Multisim 2001 схему наращивания размерности дешифратора 3:8 до 4:16, используя микросхемы 74LS138N(D), 74HC137N(D), 74HC138N(D).

3. Воспользовавшись приведенным теоретическим материалом, аналогично реализуйте Multisim 2001 схему дешифрации пятиразрядного двоичного кода с использованием дешифраторов 3:8 и 2:4, используя микросхемы 74LS138N(D), 74HC137N(D), 74HC138N(D) и 74LS139D(N), 74HC139DW(N) соответственно.

Контрольные задания

-

Разработайте схему динамической индикации на дешифраторах К155ИД4 (1шт.) и К514ИД2 (1шт.) для восьми семисегментных индикаторов. Схема должна содержать две группы входов – D3 - D0 и A2 – A0. Двоичный код на шине D[3..0] должен определять зажигаемую цифру, а код на шине A[2..0] должен определять один из восьми индикаторов, на котором эта цифра будет отображаться. В каждый момент времени должен работать только один индикатор, все остальные должны быть погашены. Такая схема, при подключении к какому либо микропроцессорному устройству (например, к принтерному порту персонального компьютера), позволит выводить восьмиразрядное десятичное число. Для этого останется только написать программу будет в требуемой последовательности быстро менять информацию на шинах A[2..0] и D[3..0]. Глаз не будет успевать замечать мигания цифр и человек увидит нормальное восьмиразрядное число.

-

Упростите булево выражение и составьте схему:

![]()

-

Упростите булево выражение и составьте схему:

![]()

-

Из Рис.4. определите номинал внутренних токоограничивающих резисторов в микросхеме КР514ИД1.

Контрольные вопросы

-

Что такое семисегментный индикатор? Чем отличается семисегментный светодиодный индикатор с общим анодом от аналогичного с общим катодом? Приведите схемы включения.

-

Определите по обозначению тип индикатора АЛС324Б (Рис.2).

-

Как соединить два дешифратора К531ИД7 для получения дешифратора большей разрядности?

-

Можно ли мультиплексоры КМОП-серий использовать в качестве дешифраторов?

Приложение

Набор логических элементов:

|

2И-НЕ |

4 шт. |

|

3И-НЕ |

6 шт. |

|

4И-НЕ |

4 шт. |

|

2И |

4 шт. |

|

2ИЛИ |

4 шт. |

|

3ИЛИ-НЕ |

3 шт. |

|

ИСКЛЮЧАЮЩЕЕ ИЛИ |

4 шт. |

|

Элементы И-ИЛИ-НЕ |

2 шт. |

|

Расширитель |

2 шт. |

Литература

-

Токхейм Р. Основы цифровой электроники. М.:Мир, 1988, 392с.

-

Потемкин И.С. Функциональные узлы цифровой автоматики. М.:Энергоатомиздат, 1988, 320с.

-

Хоровиц П., Хилл У. Искусство схемотехники. М.:Мир, 1998.

-

Янсен Й. Курс цифровой электроники. Т.1, Т.2, М.:Мир, 1987.

-

Тули М. Справочное руководство по цифровой электронике. М.:Энергоатомиздат, 1990, 176с.

-

Мальцева Л.А., Фромберг Э.М., Ямпольский В.С. Основы цифровой техники. М.:Радио и связь, 1987, 128с.

-

Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л.:Энергоатомиздат, 1986, 280с.

-

Шило В.Л. Популярные цифровые микросхемы. Справочник. М.: Металлургия, 1988, 352с.

-

Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. М.:Высшая школа, 1991, 526с.

-

Угрюмов Е. Цифровая схемотехника. СПб.:БХВ-Петербург, 2001, 528с.

-

Новиков Ю.В. Основы цифровой схемотехники. М.:Мир, 2001, 379с.

-

Партала О.Н. Цифровая электроника. СПб.:Наука и техника, 2001, 224с.