Министерство Общего и Профессионального Образования РФ.

Новосибирский Государственный Технический Университет.

Кафедра ВТ.

Курсовая работа

По дисциплине

Организация ЭВМ.

Факультет: АВТ.

Группа: АМ – 109

Студент: Мазко Г. Н.

Преподаватель: Гребенников В. Ф.

Новосибирск 2004.

Содержание.

-

Цели работы.

-

Исходные данные.

-

Общие исходные данные.

-

Индивидуальные исходные данные.

-

-

Разработка и описание структурной схемы ЭВМ.

-

Структурная схема ЭВМ.

-

Описание структурной схемы ЭВМ.

-

Система прерываний.

-

Блок синхронизации и таймер.

-

Адресный кэш (TLB).

-

Клавиатура и монитор.

-

Память.

-

Ввод/вывод

-

-

Разработка укрупненной структурной схемы процессора и алгоритма его инициализации.

Выводы.

Список литературы.

-

Цели работы.

Целями курсового проектирования являются углубление и закрепление теоретических знаний студентов, приобретение навыков разработки узлов ЭВМ на структурном, функциональном и алгоритмическом уровнях.

-

Исходные данные.

-

Общие исходные данные.

В состав разрабатываемой ЭВМ входят следующие блоки:

-

центральное процессорное устройство (ЦПУ);

-

микропрограммное устройство управления (МУУ);

-

оперативная память (ОП);

-

блок синхронизации (БС);

-

система прерывания программ (СПП);

-

таймер;

-

система ввода-вывода (СВВ);

-

монитор и клавиатура.

Основные параметры ЭВМ:

-

адресность ЭВМ - двухадресная;

-

длина команды - переменная.

-

разрядность - не менее 16;

-

ёмкость ОП - не менее 16 Мбайт.

-

Индивидуальные исходные данные:

-

структура – двухшинная;

-

система прерываний – цепочечная микро;

-

память – страничная;

-

кэш – адресный (TLB);

-

ввод/вывод - по прерываниям;

-

разрабатываемый блок – центральный процессор;

-

Разработка и описание структурной схемы ЭВМ.

-

Структурная схема ЭВМ.

-

Описание структурной схемы ЭВМ.

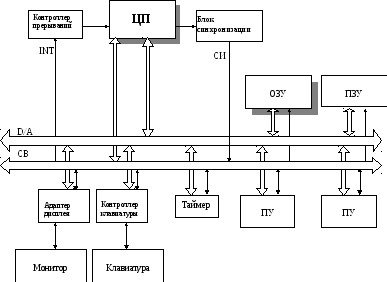

Структура ЭВМ – шинная (магистральная). Состав шин: мультиплексированная шина адреса и данных (AD) и шина управления (CB). Двухшинная организация предполагает передачу адреса и данных по одним и тем же физическим проводникам в разные моменты времени. Например, адрес передается по фронту синхросигнала, данные по спаду или же специальный сигнал определяет, что в данном такте находится шине. Возможны комбинированные варианты: информация “готова” и на фронте и на спаде, а качество (данные/адрес) определяется селектирующим сигналом. Разрядность шины адреса/данных – 32 бита.

Шина управления предназначена для управления работой ЭВМ и содержит такие сигналы, как: запрос памяти MEMRQ, запрос регистров ввода-вывода IORQ, сигналы вывода-ввода информации RD/WR, запрос прерывания INTR, подтверждение прерывания INTA, синхросигнал, сигнал сброса RST, сигнал, определяющий информацию на шине AD как адрес, или как данные и т.д.

Основным узлом ЭВМ является

центральный процессор, который управляет

всеми устройствами, входящими в ЭВМ.

Системная шина

Также сюда входят контроллеры различных устройств, блок синхронизации, контроллер прерываний, таймер, ОЗУ, ПЗУ и т.д.

-

Система прерываний.

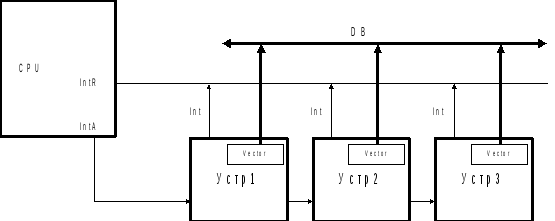

Система прерываний цепочечная на микро уровне.

Цепочечная структура прерываний характеризуется наличием единой линией запроса на прерывание, и линией подтверждения (INTA), проходящей через все источники прерываний и определяющей приоритеты прерываний в соответствии с порядком подключения устройств. Получив запрос, процессор переводит свой выходной буфер данных в третье состояние и выдает подтверждение по линии INTA, который проходит от одного устройства к другому, пока не достигнет инициатора прерывания, тем самым, разрешая этому устройству выставить на шине данных свой идентификационный номер (косвенный адрес обработчика прерывания). Данная структура характерна более низкими затратами как аппаратных, так и программных средств на реализацию, но недостаток состоит в том, что приоритет устройства фиксирован и определяется порядком подключения, а также сигнал Interrupt Acknowledge (INTA) распространяется с некоторой временной задержкой.

Прерывания на микропрограммном уровне отличаются коротким временем ответа, так как запрос на прерывание подается на вход секвенсора INTR, что означает возможность получения ответа по окончанию текущего микроцикла, если прерывания разрешены (сигнал INTEN = H), то INTA#L. Далее адрес возврата из прерывания сохраняется в стеке (возможна вложенность прерываний) и происходит переход к подпрограмме обработки прерывания по вектору.

Микропрограмма обработки прерывания должна сохранить все необходимые для дальнейшей работы регистры, PSW (слово состояния процессора). После завершения обработки прерывания адрес, на котором была остановлена прерванная микропрограмма, выталкивается из стека.