Ткаченко_Ф_А_Техническая_электроника_2000

.pdf

181

При достижении током коллектора тока насыщения возрастание коллекторного тока прекращается.

На переходные процессы в транзисторе сильное влияние оказывают емкости р–n переходов. Напряжение Uбэ не может измениться скачком (рис. 9.3) из-за влияния барьерных емкостей эмиттерного и коллекторного переходов. Когда напряжение Uбэ достигнет порогового значения (момент времени t3), резко возрастают инжекция носителей из эмиттера в базу и диффузионная емкость Cдиф э, рост Uбэ замедляется, в коллекторной цепи появляется ток, создающий падение напряжения на резисторе Rк.

Интервал времени с момента подачи входного сигнала до момента, когда ток коллектора достигает 0,1Iк нас, называют временем задержки, и его можно рассчитать по формуле

tзд = |

Cэ‡€ р + Cђ‡€ р |

(Uбэ пор + Uвх2 ), |

(9.12) |

|

|||

|

I‡ |

|

|

где Iб ≈ Uвх1 > Iбгр ;

Rб

Cэ бар, Cк бар - усредненные барьерные емкости эмиттерного и коллек-

торного переходов.

Коллекторный ток возрастает по экспоненте, стремясь к величине Iб1h21э

|

|

− |

t |

|

|

|

|

τβ ) . |

(9.13) |

||

iк(t) = h21 |

Iб |

(1−e |

|||

э |

1 |

|

|

|

|

Интервал времени с момента нарастания фронта выходного импульса тока от 0,1Iк нас до 0,9Iк нас называют временем нарастания, и оно равно

|

|

Iб |

|

|

|

|

tнр = τβ ln |

|

1 |

|

. |

(9.14) |

|

Iб1 |

− |

Iкнас |

|

|||

|

h21э |

|

|

|

||

|

|

|

|

|

|

|

Суммарное время tзд+tнр=tвкл называется временем включения. За это время накапливаемый заряд в базе достигает значения Q, характерного для активного режима. С увеличением времени воздействия входного сигнала транзистор переходит в режим насыщения, заряд в базе достигает значения Qб нас.

С приложением запирающего напряжения в момент времени tз в цепи базы появляется отрицательный ток Iб обр ≈ Uвх2  Rб . Скачкообразно понижает-

Rб . Скачкообразно понижает-

ся напряжение на базе, связанное с изменением напряжения на сопротивлении базы rб: ∆Uбэ = (Iб + Iб обр)rб. На эмиттерном и коллекторном переходах оста-

ются прямые напряжения до тех пор, пока концентрация избыточных носителей у границ переходов в базе не уменьшится до нуля. При этом ток коллектора остается постоянным, равным Iк нас, а выходное напряжение низким. Время с момента подачи на базу запирающего импульса до момента, когда ток коллектора уменьшается до 0,9Iк нас называется временем рассасывания tрас

182

tрас = τ′β ln |

|

Iб + Iб обр |

, |

(9.15) |

|

|

Iк нас |

+ Iб обр |

|||

|

|

h21э |

|

|

|

|

|

|

|

|

|

где τ'β ≈ τβ/2 - эквивалентная постоянная времени, равная времени жизни неосновных носителей заряда в базе в режиме насыщения.

После выхода транзистора из режима насыщения при t>t4 ток коллектора уменьшается до нуля, а напряжение на выходе возрастает до Uип. Время с момента уменьшения тока коллектора от 0,9Iк нас до 0,1Iк нас называют временем спада (среза) tсп

|

|

|

|

|

Iк нас |

|

|

t |

|

= τ |

ln 1 |

+ |

. |

(9.16) |

|

|

|

||||||

|

сп |

β |

|

Iб обрh21э |

|

|

|

|

|

|

|

|

|

|

|

Суммарное время tвык=tрас+tсп называется временем выключения. Время включения и время выключения характеризуют быстродействие ключа. Для повышения быстродействия необходимо использовать транзисторы с большими предельными частотами.

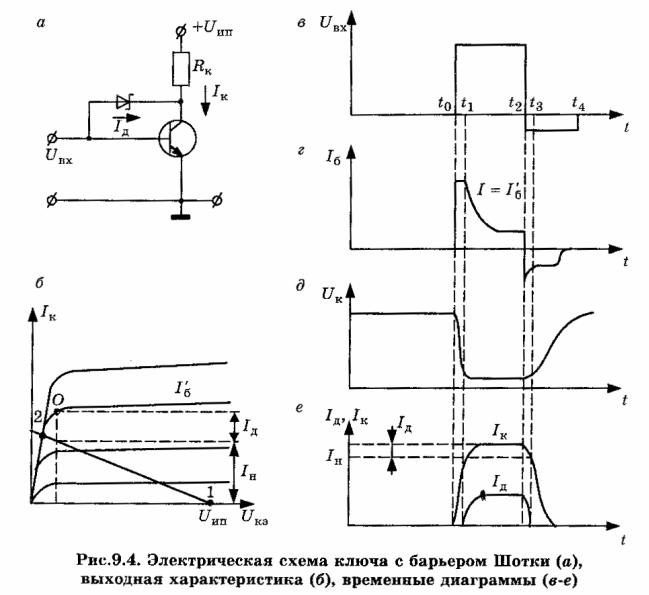

9.3. Ключ с барьером Шотки

Для повышения быстродействия ключа необходимо уменьшить время рассасывания избыточных зарядов, т.е. транзистор должен работать на границе активного режима и режима насыщения. Для предотвращения насыщения транзистора в ключе используют нелинейную обратную связь, предложенную Б.Н. Кононовым в 1955 году. При микроэлектронном исполнении нелинейная обратная связь наиболее эффективна, если между коллектором и базой включается диод Шотки (рис. 9.4,а).

При отсутствии сигнала на входе схемы транзистор закрыт, закрыт и диод Шотки, выходное напряжение велико (точка 1 на рис. 9.4,6). При подаче на вход положительного сигнала транзистор открывается, и рабочая точка по нагрузочной прямой начинает перемещается в точку 2. Ток коллектора растет, а потенциал коллектора уменьшается, и в момент времени t1 открывается диод Шотки. После этого входной ток перераспределяется между базой транзистора

идиодной цепью так, что рабочая точка перемещается в точку О, в которой

Iк = Iд+Iн (рис. 9.4,в). Точка О располагается в непосредственной близости к границе насыщения в области линейного участка характеристик. При подаче запирающего сигнала на вход схемы начинается спад коллекторного тока. За-

держка начала нарастания коллекторного напряжения (время t3) обусловлена временем, в течение которого ток диода уменьшается от начального значения Iд до нуля, и она составляет менее одной наносекунды. Спад коллекторного тока

инарастание коллекторного напряжения происходит как у обычного транзисторного ключа.

183

Наряду с высоким быстродействием транзисторные ключи с нелинейной обратной связью имеют следующие недостатки:

1.Относительно большее падение напряжения на открытом ключе (около

0,5 В).

2.Меньшая температурная стабильность.

3.Худшая помехоустойчивость, что объясняется более высоким входным сопротивлением в открытом состоянии.

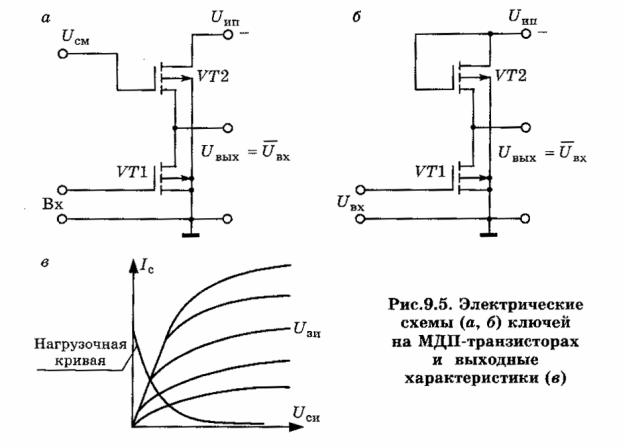

9.4. Ключи на МДП транзисторах

МДП-транзисторы применяют при построении цифровых микросхем. Это обусловлено простотой их конструкции, малыми размерами и низкой потребляемой мощностью. Цифровые МДП микросхемы состоят только из МДПтранзисторов, функции пассивных элементов выполняют сами транзисторы. МДП микросхемы представляют собой схемы с непосредственными связями,

184

поэтому в таких схемах отсутствуют конденсаторы связи. По принципу действия цифровые МДП микросхемы можно подразделить на статические и динамические. Логические микросхемы статического типа выполняются как на МДП-транзисторах с каналами одного типа проводимости, так и на комплементарных парах. Так называют пару транзисторов, имеющих примерно одинаковые значения основных параметров, но с полупроводниковыми структурами противоположного типа. В биполярной технологии – это транзисторы n–p–n и p–n–p, в полевой технологии - транзисторы с n– и p–каналами. Такие МДП микросхемы называют комплементарными.

Базовым элементом логических МДП микросхем является инвентор (ключ). В качестве нагрузочного элемента в ключевой схеме используется линейный резистор или МДП-транзистор в качестве нелинейного резистора. Использование в качестве нагрузки нормально открытых МДП-транзисторов позволяет отказаться от применения высокоомных диффузионных резисторов, занимающих большую площадь на подложке. На рис. 9.5 приведены схемы инверторов на МДП-транзисторах с каналом p–типа.

Транзистор VT1, исток которого соединен с заземленной шиной питания, является ключевым (активным), а транзистор VТ2 - нагрузочным, выполняющим роль резистора. Затвор нагрузочного транзистора подключается к источнику напряжения смещения Uсм (рис. 9.5,а), имеющему более высокий по абсолютному значению уровень напряжения, чем напряжение источника питания Uип, или непосредственно к источнику питания Uип (рис. 9.5,б). В ключе с ис-

185

точником смещения, нагрузочный транзистор VТ2 представляет собой квазилинейную нагрузку. Напряжение источника смещения такое, что он работает только в крутой области ВАХ. В ключе с одним источником питания нагрузочный транзистор используется в качестве нелинейной нагрузки и транзистор работает в пологой области ВАХ, где

|

Uси |

|

≥ |

Uзи − Uзи пор |

. |

(9.17) |

|

|

|||||

Ток, протекающий через нагрузочный транзистор, определяется из выра- |

||||||

жения |

|

|||||

Iн = Sн[(Uип − Uвых)− Uзи пор]2 , |

(9.18) |

|||||

где Sк, Sн – удельная крутизна ключевого и нагрузочного транзисторов.

На рис. 9.5,в приведены ВАХ ключа на МДП-транзисторе с транзистором в цепи нагрузки. Точка пересечения двух любых кривых дает совместное решение системы уравнений, описывающих состояние ключевого и нагрузочного транзисторов. А так как ток, протекающий в последовательно включенной цепи транзисторов одинаков, то работа транзистора в пологой области описыва-

ется следующим выражением |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

Sн[(Uип − Uвых)− Uзи пор]2 = Sк(Uвх − Uзи пор)2 . |

|

|

|

(9.19) |

||||||||||||||||||||

В крутой области характеристик ключевого транзистора это уравнение |

||||||||||||||||||||||||

имеет вид: |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Sн[(Uип − Uвых)− Uзи пор]2 =Sк[2(Uвх − Uзи пор)Uвых − Uвых2 ]. |

(9.20) |

|||||||||||||||||||||||

Если напряжения Uвых и Uвх – Uзи пор пронормировать к разности Uип – |

||||||||||||||||||||||||

Uзи пор, то получим |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

Uвых |

|

|

Sђ |

|

|

Uвх |

− Uзи пор |

|

|

Uвых |

|

|

||||||

1− |

|

|

|

|

|

= |

2 |

|

|

|

− |

|

||||||||||||

U |

|

|

|

|

S |

|

|

− U |

|

|

|

|

|

|||||||||||

|

|

|

|

|

− U |

|

|

|

|

|

U |

|

|

U |

|

− U |

|

|

|

|||||

|

|

|

|

ип |

|

зи пор |

|

|

’ |

|

|

ип |

|

зи пор |

|

ип |

|

зи пор |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

Uвых |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

− |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(9.21) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Uип − Uзи пор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выражение (9.21) позволяет получить выражение для величины остаточ- |

||||||||||||||||||||||||

ного напряжения на транзисторе |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

Uост = |

|

Sк (Uвх − Uзи)−1. |

|

|

|

|

|

|

|

|

|

|

|

(9.22) |

||||||||||

|

|

|

|

|

|

Sн |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Для создания БИС и СБИС используют МДП-транзисторы с n–каналами.

Аключи строят с токостабилизирующей нагрузкой (Д–нагрузкой) (рис. 9.6).

Вкачестве нагрузки применяют МДП-транзистор VT2 со встроенным каналом n–типа, у которого затвор соединен с выходом схемы, а не с источником питания. Нагрузочный транзистор VТ2 всегда открыт, так как Uзи2 = 0.

При Uвх1 ≤ Uзи пор транзистор VТ1 закрыт, и напряжение на выходе практиче-

186

ски равно +Uип. При Uвх1 > Uзи пор оба

транзистора открыты, на выходе имеется минимальное напряжение. Ключи с Д–нагрузкой увеличивают быстродействие и повышают помехоустойчивость по сравнению с МДПключами с нагрузочными индуцированными МДП-транзисторами. Низкая скорость переключения зависит от величины паразитной емкости, которая перезаряжается в течение переходного процесса. Формирование фронтов на выходе ключа определяется временем заряда и разряда эквивалентной

емкости. Емкость заряжается через нагрузочный транзистор, а разряжается через VТ1. Сопротивление нагрузочного транзистора VТ2 почти в 10…20 раз превышает сопротивление открытого ключевого транзистора. Поэтому время включения (определяется сопротивлением VТ1) намного меньше времени выключения, определяемого нагрузочным транзистором (рис. 9.6). В связи с этим быстродействие ключа ограничено большим временем выключения, в течении которого Cн заряжается до выходного напряжения током, протекающим через нагрузочный транзистор. Длительность фронта выключения определяется из решения системы уравненийдлятоковзарядаемкости инагрузочного транзистора

dU |

вых |

|

|

|

Iс = Cн |

|

, |

|

|

|

|

(9.23) |

||

|

dt |

|||

Iн = Sн[(Uип − Uвых)− Uзи пор]2. |

|

|||

Приравняв правые части уравнений и выполнив интегрирование, получим выражения для времени выключения

tвых = |

|

(U |

|

Cн |

|

|

). |

(9.24) |

|

S |

ип |

− U |

зи пор |

− U |

вых |

||||

|

н |

|

|

|

|

|

|||

Для уменьшения tвыкл необходимо увеличивать удельную крутизну нагрузочного транзистора. Быстродействие ключа значительно возрастает при работе нагрузочного транзистора в крутой области ВАХ, так как высокое напряжение на затворе предотвращает закрывание нагрузочного транзистора во время переходного процесса. Ключ реализует логическую функцию инверсии НЕ.

9.5. Ключ на комплементарных транзисторах

Рассмотренные ранее ключи имеют существенный недостаток: в открытом состоянии ключа оба транзистора открыты, выходное напряжение логического нуля имеет не нулевое, а определенное значение, что снижает статиче-

187

скую помехоустойчивость. Ключ в открытом состоянии потребляет энергию. Если бы в открытом состоянии ключевого транзистора нагрузочный транзистор был закрыт, то выходное напряжение стремилось бы к нулю, и ключ не потреблял бы энергии в статических состояниях. Это удается достичь, используя ключи на комплементарных транзисторах (рис. 9.7,а).

Ключ состоит из двух последовательно включенных МДП-транзисторов с каналами n– и p– типа. Транзистор VТ1 является ключевым, его исток соединен с заземленной шиной питания, а сток подсоединяется к стоку нагрузочного транзистора VТ2.

Подложка n–канального транзистора VТ1 заземлена, а p–канального подключена к положительному выводу источника питания Uип. Затворы обоих транзисторов объединены и являются входом ключа. При этом:

1.Входное напряжение управляет не только ключевым, но и нагрузочным транзистором.

2.Управление является противофазным, напряжения на затворах транзисторов равны Uзи1 = Uвх , Uзи2 = Uип − Uвх .

При нулевом потенциале затворов транзистор VТ1 закрыт, а транзистор VТ2 открыт и работает в линейной области, так как напряжение между затвором и истоком равно Uип. При этом ток в общей цепи определяется запертым транзистором VТ1 и составляет величину Iост1 . Напряжение на выходе ключа

практически равно Uип. При подаче на затворы напряжения, близкого к величине Uип, транзистор VТ2 закрывается, а транзистор VТ1 открывается. Ток в общей цепи по-прежнему остается на уровне Iост, хотя состояния транзисторов изменились. На выходе формируется уровень напряжения, близкий к потенциалу земли. Уровни выходных напряжений имеют почти экстремальные значения: близкое к нулю Uвых≈0, близкое к напряжению источника питания Uвых≈Uип, а перепад напряжений близок к Uип.

188

Важнейшей особенностью комплементарных ключей является то, что они практически не потребляют энергии в обоих состояниях. Эти состояния можно назвать "открытым" или "закрытым" только условно – по отношению к одному из транзисторов. Такие схемы расходуют энергию только при переключении из одного логического состояния в другое (рис. 9.7,б).

Микросхемы на КМДП транзисторах имеют высокое быстродействие, поскольку перезаряд емкости нагрузки как при включении, так и при выключении происходит через открытый транзистор, однако их быстродействие меньше достигнутого биполярными микросхемами. Поэтому необходимо уменьшать емкости переходов, использовать новые технологии. Применение V- образной формы затвора, пространственно замыкающей стоковые области, позволяет увеличить быстродействие по сравнению со стандартной технологией КМДП ИС в 4…5 раз.

Применение сапфировой подложки для изготовления КМДП микросхем позволило значительно уменьшить паразитные емкости переходов и увеличить быстродействие в два-три раза.

Ключи на комплементарных МДП транзисторах имеют следующие достоинства:

–малая статическая мощность, потребляемая от источника питания;

–высокая помехоустойчивость, обусловленная большим перепадом выходных напряжений;

–широкий диапазон рабочих напряжений (3…15 В), причем для совре-

менных микросхем КМДП напряжение питания обычно составляет Uип= 5 В, что позволяет совмещать КМДП логику с ТТЛ без промежуточных трансляторов;

–широкий диапазон рабочих температур (–55…+125 °С);

–высокое входное сопротивление ( 1012 Ом);

–простота сопряжения со слаботочными источниками входного напря-

жения.

Это позволяет применять КМДП микросхемы в устройствах с автономным питанием, в различных бортовых устройствах, автономных устройствах сбора и обработки данных, запоминающих устройствах без разрушения информации.

9.6. Алгебра логики и основные её законы

В схемах импульсной техники для обработки и преобразования информации используются цифровые методы. Используемые в схемах сигналы близки по форме к прямоугольным и имеют два фиксированных уровня напряжения, уровню высокого напряжения приписывается символ "1" (истинность), а уровню низкого напряжения – символ "0" (ложь). При анализе импульсных устройств используется двоичная система счисления. Математическим аппара-

189

том анализа и синтеза цифровых систем служит алгебра логики (булева алгебра), оперирующая логическими связями и зависимостями. Основные положения алгебры логики разработал в XIX веке английский математик Джордж Буль. Значения двоичных сигналов 0 и 1 не дают количественной оценки состояния переменных или состояния их функций, поэтому эти символы нельзя рассматривать как арифметические числа. В связи с этим алгебра логики является алгеброй состояний, а не алгеброй чисел.

Функция двоичных переменных, принимающая значения "1" и "0", называется логической функцией (переключательной, функцией алгебры логики).

Элементарными логическими функциями являются: логическое сложение (дизъюнкция), логическое умножение (конъюнкция), логическое отрицание (инверсия).

Аналитические формы записи функций позволяют получить основные законы алгебры логики отдельно для операций логического умножение и сложения (И и ИЛИ).

1. Переместительный закон (закон коммутативности)

X1X2 = X2X1; X1+X2 = X2+X1.

2. Распределительный закон (закон дистрибутивности логического умножения по отношению к сложению)

(X1+X2)X3 = X1X3+X2X3.

3. |

|

|

Сочетательный закон (закон ассоциативности) |

|||||||||||||||||||||||

(X1X2)X3 = X1(X2X3) |

(X1+X2)+X3 = X1+(X2+X3) |

|||||||||||||||||||||||||

4. |

|

|

Законы повторения (тавтологии) |

|||||||||||||||||||||||

XX = X; |

X+X = X. |

|||||||||||||||||||||||||

5. |

|

|

Законы поглощения |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

X1(X1+X2) = X1; |

X1+X1X2=X1. |

|||||||||||||||||||||||||

6. |

|

|

Законы отрицания: |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

а) закон дополнительности |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

= 0; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

XX |

|

|

|

|

|

|

X + X = 1; |

||||||||||||||||||

б) закон дуальности - правило де Моргана (инверсия суммы переменных |

||||||||||||||||||||||||||

есть произведение их инверсий) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

1 |

|

2 = |

|

1 + |

|

2 ; |

|

|

1 + |

|

2 = |

|

1 |

|

2 ; |

|

||||||||

|

X |

X |

X |

X |

X |

X |

X |

X |

||||||||||||||||||

в) закон двойного отрицания |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

= X. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

X |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

7. |

|

|

Законы склеивания |

(X1 + X2 )(X1 + |

|

2 )= X1 . |

||||||||||||||||||||

|

X1X2 + X1 |

|

2 = X1 ; |

|

||||||||||||||||||||||

|

X |

X |

||||||||||||||||||||||||

8. |

|

|

Законы универсального множества |

|||||||||||||||||||||||

X 1 = X; |

X+1 = 1. |

|||||||||||||||||||||||||

9. |

|

|

Законы нулевого множества |

|||||||||||||||||||||||

X 0 = 0; |

X+0 = X. |

|||||||||||||||||||||||||

Логическая функция может быть выражена словесно, в алгебраической форме и переключательной таблицей (таблицей истинности).

190

ЛОГИЧЕСКОЕ СЛОЖЕНИЕ (дизъюнкция, операция ИЛИ) на языке электронной схемы означает наличие напряжения на выходе схемы, при наличии на одном из входов напряжения:

Uвых = Uвх1 Uвх2 или y = x1+x2.

Кроме символа "+", для дизъюнкции употребляется символ " ", т.е.

y = x1 x2

На рис. 9.8 представлены схемы, реализующие операцию ИЛИ. Так, если оба ключа разомкнуты (рис. 9.8,а), то напряжение на выходе равно нулю. Если положительный сигнал поступает хотя бы на вход одного из диодов (рис. 9.8,б), диод открывается, и сигнал поступает на выход схемы.

Если число входных сигналов логического элемента ИЛИ меньше числа входов, то неиспользуемые входы заземляют.

ЛОГИЧЕСКОЕ УМНОЖЕНИЕ (конъюнкция, операция И) означает в электронной схеме наличие напряжения на выходе, при наличии всех входных сигналов.

Uвых = Uвх1 Uвх2 или y = x1·x2.

Для обозначения конъюнкции часто используют символ или &, т.е.

y=x1 x2.

На рис. 9.9 представлены схемы, реализующие операцию И. Элемент И является схемой совпадения: сигнал "1" на выходе схемы появляется при совпадении сигналов "1" на всех его входах.

При нулевом значении сигнала хотя бы на одном из входов (рис. 9.9,б) соответствующий диод открывается. Напряжение на выходе определяется падением напряжения на открытом диоде, которое определяет значение логического нуля. Если на все входы поступает сигнал логической "1", диоды закрываются. Напряжение на выходе будет равно Uип·R2/(R1+R2), определяющее логическую "1".

На практике, если число входных сигналов логического элемента И меньше числа входов, то неиспользуемые входы подсоединяют к положительному выводу источника питания +Uип.