- •1)По месту процессора в вс:

- •22. Основные виды памяти вм.

- •23.Кэш память.

- •25.Технологии оперативной памяти

- •27.Обмен информацией в вм. Способы обмена данными между памятью и периферийными устройствами. Пдп.

- •26.Энергонезависимая память вм.

- •28. Системные интерфейсы и интерфейсы внешних устройств.

- •29. Вычислительные системы. Классификация вс.

- •30. Классификация архитектур вс Флина.

- •32. Классификация вс по способу организации памяти. Архитектура smp, mpp, numa.

- •33. Класстерные системы.

- •34. Телекоммуникационные вычислительные сети. Виды твс.

- •35. Локальные вычислительные сети. Основные понятия.

- •36. Топология лвс.

- •37. Физическая среда передачи в лвс. Виды, характеристики.

- •38. Понятие «открытая система». Модель osi

- •39.Уровни и протоколы модель osi. Физический, канальный и сетевой уровни.

- •40.Уровни и протоколы модель osi. Транспортный, сеансовый, представительский уровень.

- •41.Разновидность сети Ethernet.

- •42. Cети Token Ring.

- •43. Cети fddi.

- •44. Беспроводные cети ieee 802.11.

- •45. Персональные cети. Bluetooth.

- •46. Cети WiMax.

№1. Вычислительные машины, системы и сети. Основные понятия

Вычис-ая машина – сист-а, выпол-ая заданную, четко определенную послед-сть операций(программу) в соответствии с выбр. алгори-ом обработки инф-ии.

|

ВМ | |

|

Аналоговые АВМ |

Цифровые ЦВМ |

|

Работает с аналогами (U(t), I(t)) |

Работает с значениями (0,1) |

В.Сис- совокупность 1-го или более комп-ов или процессоров, программного обеспечения, и периферийного оборуд-я, организ-е для совместного вып-ия информационно выч.проц-в

В.Сеть- система взаимосвязанных между собой ЭВМ, а также технического и программного обеспечения для их взаимодействия.

№2 История развития вычислительных машин. Поколения ЭВМ

В 17в. была изобретена логарифмич-я линейка

1642 – Паскаль изобрел восьмиразрядный суммирующий механизм

1820 – Шарль де Кольмар.Устрой-во кот-е могло умножать, делить

1833 Чарльз Беббидж. Предлож. использовать для ввода-вывода данных – перфокарту.

1888 – Герман Холерит создал первую электро-механич. машина – Табулятор, она могла расчит-ть, сортировать данные. Было использовано в 1890

1896 – IBM

1944 – Mark-1. Весила 35тонн. Основана на элктро-механ. реле, 23 разрядная, 4секунды.

1946 – EniaC(США) 30тонн, 170м2, 18000электр.ламп, 5тыс.опер-ий в сек.

1950 – МЭСМ, БЭСМ – машина 1 поколения

1951 – UNIVAC – маш.2 поколения. На этом этапе получил развитие принцип автоном. Различные устройства могли управлять вычислительными системами. Разработка стандартных программ, создаются специализированные системы. Машины Минск,Мир.

1959 – интегральные схемы -машины 3 поколения-Машины создаются на основе комунникации СМ ЭВМ

Машины 4 поколения – БИС

1970 Эдвард Хофор. сотрудник Intel, создал первую машину 4покол.

1981 – IBM создал. процессор 8086 IBM PC XT в этой машине был заложен принцип архитектуры, что привело к массовому произовдству.

№3 Классификация ВМ

По форме представления информации:

-АВМ(аналоговые), -ЦВМ(цифровые), -ТВМ(терминальные)

По назначению:

-универсальная(ВМ предназначенная для решения широкого круга задач)

-специализированная(для решения узкого круга задач)

- проблемно-ориентированные

По размерам:

-супер ЭВМ

-большие ЭВМ

-малые ЭВМ

-микро ЭВМ

№4 Классическая архитектура ЭВМ и принципы фон Неймана

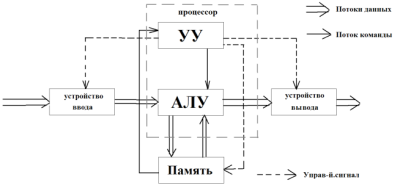

Джон фон Нейман. Считал, что ВМ должно содержать устройство управления, арифмет. логическоеустройство, память, устройства ввода-ввывода, связи между ними(потоки данных, команд и управ-ся истоки). Преобразование данных осуществляется согласно заданной программе:

Процессор – считывает, выполняет команду организует обращение памяти и инициирует работу устройство.

Память служит для хранения данных и программ.

Устройство преобразует данных форму для представления данных.

Устройство вывода для чтения форма понятного для человека

Принцип организации ВМ по Нейману:

-двоичное кодирование информации и представление его в виде слов фиксированной разрядности

-линейно-адресная организация памяти в виде N ячеек фиксированной разрядности, ячейки пронумерованы (0…N-1) Номер ячейки является её адресом.

-представление алгоритма программы, состоящей из команд. Команда содержит код операции, адреса операндов и некот. Служебную инф.

-Хранение команд и данных в одной памяти

-Выч-й процесс. Организация как последовательное выполнение команд в порядке, определенном программой

-жесткость архитектуры (неизменность в процессе работы ВМ, её структуры, списка команд, метода кодирования данных и др.)

№5 Цикл работы ЭВМ. Команды ЭВМ

Цикл работы. При выполнении каждой команды, ЭВМ проделывает след.действия:

-Согласно содержимому счетчику команд считывается очередная команда программ

-Счетчик команд автоматически изменяется так, чтоб он содержал адрес следующей команды

-Считанная команда расшифровывается, из нее извлекаются необходимые данные. И над ними выполняются требуемые действия

-Далее все описанные действия циклически повторяются

Команды ЭВМ:

1)передача данных

2)команды ариф.операций

3)ком-ы логических операций

4)ком-ы сдвига

5)ком-ы ввода и вывода

6)ком-ы

реализующие нелинейные алгоритмы

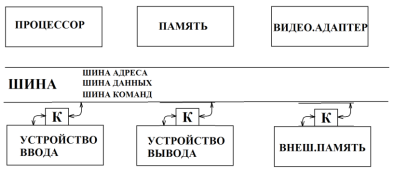

№6 Шинная архитектура ЭВМ

Шина состоит из 3-х частей:

шина адреса - определяет куда передается информация

шина данных – по которой передается информация

шина команд – которая регулирует процесс обмена информацией

№7 Принцип открытой архитектуры. IBM PC совместимые ПК

Конец 70-ч годов.

IBM PC i-8080, 280 Mototola – процессоры I-ых ПК

1976 компьютеры Apple – массовое пр-во ПК

IBM 1981 – комп. массового применения

Фирмой IBM были предлож.принцип откр.архитек-ы, комп. рассматривается как гибкая, легко расширяемая модульная система, в которой допускалась возможность использование программ и аппаратных средств сторонних производителей.

Принцип откр.архитек:

-породил конкуренцию

-цена упала в разы

-стали разрабатывать различные стандарты

-появилась материнская плата

№8 Структурная организация ПК. Основные блоки ПК

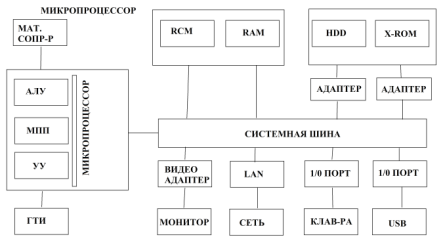

Микропроцессор – цент-й блок ПК, предназ-й для управ. работы всех блоков и выполнения арифмет, логич операций над информ-й:

УУ(устр.упр.)-формирует и подает во все блоки ВМ в нужный момент времени опр-й сигнал формируется адреса ячейки используемых управления операции.

АЛУ(ариф.логич.устр)- уст. предназначена для выполнения арифметических и логических операци. МПП(Микропроцессорная память)- обозначен для кратковременных хранения, записи и выдача инф. непосредственно ближайший такты работы ВМ.

ГТИ(генератор тактов импульса)-устр, которое генерирует последовательность тактических импульсов, частота этих импульсов определяет тактовую частоту машин

Системная шина-основная интерфейсная система компа, обеспеч-ая сопряж-е и связь между собой всех его устройств, включает в себя:

ШД(шина данных)-для параллельной передачи данных

ША-для параллельной передачи данных двоичного кода адреса

ШУ-для передачи управ-го сигнала во все блоки ВМ

Память- предназначена для хранения и оперативного обмена инфо-ей со всеми блоками ПК.

Интерфейсная система микропроц - предназначена для связи микропроцессора с др.устр. ПК.

№9 Процессоры. Классификация

Процессор – устройство, осуществляющее процесс автоматической обработки данных и программное управление этим процессом. Процессоры можно классифицировать:

1)По месту процессора в вс:

-центральный п-р

-сопроцессор п-р

-переферийный п-р

-процессорный элемент многопроцессорной системы

2)по способу обработки инфо-и:

-с II обработкой разряда

-с послед-й обработкой разряда

-со смежной

3)по степени интеграции

4)по тактовой частоте

5)по разрядности

6)по полноте команд

-CISC

-RISC

7)по назначению:

-универсальное

-специализированные

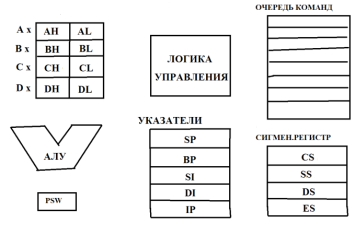

№10 Архитектура микропроцессора i8086

Регистр.общего

назначе РОН (АхВхСхDx)

Предназ.для хранения операндов и результ.операций

Ax(аккумулятор)-основной сумматор(яв-ся осн.регистром)

Вх(Base)- яв-ся базовым рег-м вычисления адреса

Сх(Counter) вступает в роли счетчика

Dx(Data)-в операциях ввода вывода содержит адрес порта ввода/вывода

Указательные группа (регистры смещения)

IP: SP-указ. стека (-структура данных представляющая из себя список элементов организованных по принципу LIFO (последним пришел, первым вышел))

BP- ук.базы.

Индексные регистры: SI-инд. источника

DI –инд. Приемника

Сегментные регистры

CS,SS,DS,ES используется для определения сегментов в памяти

№11 Адресация процессора i8086. Прерывания. Порты ввода/вывода

Имеется 8 регистров (АХ, СХ, DX, ВХ, SP, BP, SI, DI), которые можно использовать для хранения 16-разрядных данных; 8 регистров (AL, CL, DL, BL, АН, СН, DH, ВН), используемые для хранения 8-разрядных данных; 2 регистра \ВХ, BP), используемые в качестве базовых, и 2 регистра (SI, Р1) используемые в качестве индексных.

Таким образом, все регистры являются регистрами специального назначения, для адресации которых используются следующие восемь способов (универсальные для всех команд):регистровая непосредственная; непосредственная;абсолютная (указывается смещение);регистровая косвенная; относительная по базе; индексная по базе;индексная; относительная и индексная с использованием программного счетчика (ПС). Структура команды сложения для этих регистров дана ниже: Режим и значение определяют исполнительные адреса. Приводятся адреса, соответствующие их значениям. Даже в случае индексной адресации 16-разрядное смещение в этом процессоре меньше, чем в процессоре MC68000. При смещении длиной 8 и 16 бит добавляют соответственно однобайтное и двухбайтное расширенное командное слово. В качестве абсолютного адреса используется двухбайтное расширенное командное слово длиной 16 бит. Отметим, что непосредственная адресация используется с различными кодами команд.

Порты ввода/вывода 8086 связь с другими компонентами ПК осуществляет с помощью портов ввода/вывода. Каждый порт идентифицируется 16-битным номером порта, значение которого лежит в диапазоне 0000h-FFFFh(65535)

Прерывание. 8086 поддерживает 256 различных прерываний с номером от 00h-FFh. Сегментные адреса 256 обработчиков прерываний, хранятся в таблице вектора прерываний, кот. хранятся по адресу 0000:0000h.

№12 Процессор 80286. Защищенный режим адресации 80286

80286- IBM PC AT

1982 – I компьютер с многозадачностью. Появился защищенный режим работы, кроме реального.

Процессор 80286, выпущенный в 1982 году, представляет второе поколение 16-разрядных процессоров. Он имеет специальные средства для работы в многопользовательских и многозадачных системах. Процессор имеет расширенную систему команд, которая кроме команд управления защитой включает все команды 8086 н и несколько новых команд общего назначения. Процессор может работать в двух режимах: 8086 Real Address Mode - режим реальной адресации (или просто реальный режим - Real Mode), полностью совместимый с 8086. В этом режиме возможна адресация до 1 Мбайт физической памяти (на самом деле, за счет УудачнойФ ошибки, почти на 64 Кб больше). Protect Virtual Address Mode - защищенный режим виртуальной адресации (или просто защищенный режим - Protect Mode).

Защищенный режим-адресация происходит не через ….а неизменяемые ячейки защищает. 16661hреальная, 016661h защищенная.

№13 Процессор 80386. Страничная адресация

17 окт.1985

*Реализация многозадачности - под процессор написали Windows3.0

*32-разрядный проц

*32-разрядная щина памяти 2^32=4Гб

*275000 транзисторов

*тактовая частота 16,20,25,33МГц

*AX->EAX

Суть страничной адресации состоит в том, что формируемый процессором (с использованием сегментной адресации) линейный адрес, "привязывается" к другому физическому адресу. Страничная адресация включается установкой тридцать первого бита (бит PG) управляющего регистра CR0. Попытка установить этот бит в реальном режиме приводит к общей ошибке защиты. Перед установкой бита необходимо заполнить каталог страниц, и поместить его адрес в регистр CR3 (он же PDBR).

Страничная адресация имеет недостаток - она замедляет обращения к памяти, поскольку для нахождения физического адреса процессор вынужден запросить таблицу страниц. Процессор кэширует наиболее часто используемые страницы, чтобы их нахождение занимало как можно меньше времени

№14 Процессор 80486. Кэш, конвейер, встроенный сопроцессор, коэффициент умножения

10апр1989 Нашли решение увеличения производ-т

КЭШ-пямять, расп.мужду процессор и ОП…памятью

Конвейер-скалярная архетектура неск. процессоров – суперскалярностью

Встроенный сопроцессор-не нежно было тратить время на обращение к сис-ой шине.

Коэф.умнож-486DX 2-66 (2-коэф,66-max частота)

№15 Процессоры Pentium. Суперскалярность.

Первый суперскалярный процессор.

Процессор запоминает статистику после 256 переходов.

Шина данных -64бит Частота-до133МГц

Pentium MMX. Технология ММХ ориентирована на решение задач мультимед. Появление 8 виртуальных резистора (физически в сопроцессоре) и 57 новых команд для мультимедиа. 1. КЭШ удвоен.2. увеличена длина конвейера до 6 ступеней. 3. Улучшен механизм параллельной работы конвейров.

Pentium pro.14 ступней при конвейерной работе. 3 конвейера. Встроенная кэш-память L2.

Pentium II.Сочетает архитектуру Pentium pro с технологией ММХ распологается в картриже на плате с кэш L2. Двойная шина. Увеличение тактовой частоты.

Суперскалярность -архитектура вычислительного ядра, использующая несколько декодеров команд, которые могут загружать работой множество исполнительных блоков. Планирование исполнения потока команд является динамическим и осуществляется самим вычислительным ядром.

№17 64 разрядные архитектуры (IA-64)

IA-64 (Intel Architecture-64) — 64-битная аппаратная платформа: микропроцессорная архитектура и соответствующая архитектура набора команд, разработанная совместно компаниямиIntel и Hewlett Packard. Реализована в микропроцессорах Itanium и Itanium 2. Несовместима с архитектурой x86

№18 Многоядерные процессоры

Многоядерный процеессор — центральный процессор, содержащий два и более вычислительных ядра на одном процессорном кристалле или в одномкорпусе. Многоядерные процессоры можно классифицировать по наличию поддержки когерентностикеш-памятимежду ядрами. Бывают процессоры с такой поддержкой и без нее.

Способ связи между ядрами: разделяемая шина сеть (Mesh) на каналах точка-точка сеть с коммутатором общая кеш-память

Кеш-память: Во всех существующих на сегодняшний день многоядерных процессорах кеш-памятью1-го уровня обладает каждое ядро в отдельности, а кеш-память 2-го уровня существует в нескольких вариантах:

разделяемая — расположена на одном кристалле с ядрами и доступна каждому из них в полном объёме. Используется в процессорах семейств Intel Core.

индивидуальная — отдельные кеши равного объёма, интегрированные в каждое из ядер. Обмен данными из кешей 2-го уровня между ядрами осуществляется через контроллер памяти — интегрированный (Athlon 64 X2,Turion X2,Phenom) или внешний (использовался вPentium D, в дальнейшемIntelотказалась от такого подхода).

№19 RISC-процессоры. Процессоры семейства Alpha, Power

RISC (англ. Restricted (reduced) instruction set computer — компьютер с упрощённым набором команд) — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения команд, чтобы их декодирование было проще, а время выполнения — короче. Первые RISC-процессоры даже не имели команд умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание команд между несколькими исполнительными блоками).

Прямым предком архитектуры Alpha является проект раннего RISC-процессора PRISM (англ.), который сам по себе является результатом нескольких более ранних проектов. DEC Alpha (также известный как Alpha AXP) — 64-разрядный RISC микропроцессор, первоначально разработанный и произведённый компанией DEC, которая использовала его в собственной линейке рабочих станций и серверов. Микропроцессор был создан для компьютеров, которые планировались на смену серии VAX и изначально поддерживался операционными системами VMS и DEC OSF/1 AXP (в 1995переименована в Digital UNIX, после покупки DEC компанией Compaq переименована в Tru64 UNIX)

PowerPC (или сокращённо PPC) — микропроцессорная RISC-архитектура, созданная в 1991 году альянсом компаний Apple, IBM и Motorola, известным как AIM.

История PowerPC начинается с прототипа микросхемы 801, созданного в IBM в конце 1970-х на основе идей Джона Кока о RISC-архитектуре. Далее она была продолжена 16-регистровым дизайном IBM/RT в 1980-х годах, который в дальнейшем развился в архитектуру POWER, представленную RISC System/6000 в начале 1990-х.

PowerPC спроектирован в соответствии с принципами RISC, в рамках концепции возможна суперскалярная реализация. Существуют версии дизайна как для 32-х, так и для 64-разрядных вариантов. В процессорах PowerPC внутренняя шина выведена на поверхность чипа, и соединена с мостом, который транслирует команды на другие шины, соединяющиеся с оперативной памятью, шиной PCI и так далее.

№20 Направления развития архитектуры процессоров ВМ

Многопотоковый процессорДанные процессоры по архитектуре напоминают трассирующие: весь чип делится на процессорные элементы, напоминающие суперскалярный микропроцессор. В отличие от трассирующего процессора, здесь каждый элемент обрабатывает инструкции различных потоков в течение одного такта, чем достигается параллелизм на уровне потоков. Разумеется, каждый поток иметт свой программный счетчик и набор регистров.

Многоядерная архитктура

Эта архитектура подразумевает интегрирование нескольких простых микропроцессорных ядер на одном чипе. Каждое ядро выполняет свой поток инструкций. Каждое микропроцессорное ядро значительно проще, чем ядро многопотокового процессора, что упрощает проектирование и тестирование чипа. Но между тем усугубляется проблема доступа к памяти, необходима замена компиляторов.

"Плиточная" архитектура

Сторонники считают, что ПО должно компилироваться прямо в "железе", так как это даст максимальный параллелизм. Такой подход требует достаточно сложных компиляторов, которые пока еще не созданы.

Многоетажная архитектура Здесь речь идет не о логической, а о физической структуре. Идея состоит в том, что чипы должны содержать вертикальные "штабеля" микроцепей, изготовленных по технологии тонкопленочных транзисторов, заимствованной из производства TFT-дисплеев. При этом относительно длинные горизонтальные межсоединения превращаются в короткие вертикальные, что снижает задержку сигнала и увеличивает производительность процессора. Идея "трехмерных" чипов уже реализована в виде работающих образцов восьмиэтажных микросхем памяти. Вполе возможно, что она приемлима и для микропроцессоров, и в недалеком будущем все микрочипы будут наращиваться не только горизонтально, но и вертикально.

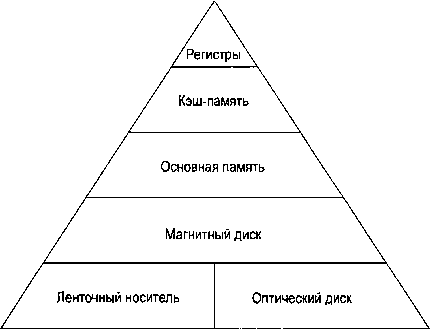

№21 Память ВМ. Иерархическая организация памяти

Память

ВМ Иерархическая

структура памяти является традиционным

решением проблемы хранения больших

объемов данных. На самом верху иерархии

находятся регистры процессора. Доступ

к регистрам осуществляется быстрее

всего. Дальше идет кэш-память, объем

которой сейчас составляет от 32 Кбайт

до нескольких мегабайтов. Затем следует

основная память, которая в настоящее

время может вмещать от 16 Мбайт до десятков

гигабайтов. Затем идут магнитные диски

и, наконец, накопители на магнитной

ленте и оптические диски, которые

используются для хранения архивов.

Пятиуровневая организация памяти