- •Минобрнауки россии

- •1. Задание на проектирование

- •Общие сведения

- •Техническое задание на проектирование

- •Варианты заданий

- •Формирование управляющего воздействия у1

- •Формирование управляющего воздействияY2

- •Формирование управляющего воздействияY3

- •Светодиодная индикация

- •Организация подсистемы прерываний

- •Выбор элементной базы

- •Реализуемый алгоритм

- •Требования к оформлению

- •Основные этапы разработки

- •Разработка микропроцессорного модуля

- •Описание элементной базы мпм

- •Микропроцессор i82386sx

- •Реализация системного контроллера

- •Шинные формирователи шин адреса и данных

- •Генератор тактовых импульсов и схема сброса

- •Реализация подсистемы прерываний

- •Разработка модуля ввода-вывода

- •Параллельно-программируемый адаптер кр580вв55

- •Разработка модуля таймера

- •Работа пит в режиме 0 (программируемый таймер)

- •Работа пит в режиме 3

- •Разработка памяти мпс

- •Распределение адресного пространства памяти

- •Разработка модулей пзу и озу

- •Распределение адресного пространства ввода/вывода

- •Разработка управляющей программы

- •Литература

Разработка микропроцессорного модуля

Микропроцессорный модуль (МПМ) является основной частью МПС и управляет всеми остальными ее блоками. Обобщенная структура МПМ приведена на рисунке 4. МПМ содержит:

микропроцессор;

системный контроллер;

генератор синхроимпульсов;

шинные формирователь шин адреса и данных.

|

|

|

Рисунок 4 - Обобщенная структура микропроцессорного модуля МПС |

Описание элементной базы мпм

Микропроцессор i82386sx

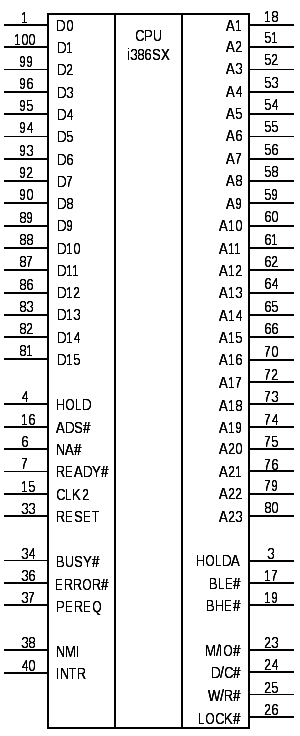

Основой МПС является микропроцессор I82386SX. УГО МП приведена на рисунке 5, а в таблице 3 приведено назначение сигналов МП.

Рисунок 5 - УГО микропроцессора I82386SX

Таблица 3 - Назначение сигналов микропроцессора 386

|

Сигнал |

I/O |

Назначение |

|

CLK2 |

I |

Clock – внешний сигнал синхронизации процессора |

|

D[15:0] |

I/O |

Data – сигналы шины данных |

|

А[23:1] |

О |

Address – сигналы шины адреса |

|

BLE#, BHE# |

О |

Byte Low Enable, Byte High Enable |

|

W/R# |

О |

Write/Read – сигнал, определяющий тип шинного цикла (запись/чтение) |

|

M/IO# |

О |

Memory/ IO# Select – высокий уровень указывает на обращение к памяти (или останов), низкий – на обращение к портам ввода-вывода или подтверждение прерывания |

|

D/C# |

О |

Data/Control# – сигнал, определяющий тип шинного цикла (высокий уровень при передачи данных памяти или ввода-вывода, низкий – при выборке кода, в цикле подтверждения прерывания или при останове) |

|

ADS# |

O |

Address Status – сигнал идентификации адресного цикла, во время которого действительны сигналы W/R#, D/C#, M/IO#, ВЕ[0:3] и А[31:2] |

|

NA# |

I |

Next Address – запрос следующего адреса при конвейерной адресации |

|

READY |

I |

Bus Ready – сигнал завершения шинного цикла. Шинный цикл расширяется на неограниченное время до появления сигнала готовности (низкий уровень) |

|

LOCK |

О |

Bus Lock – сигнал монополизации управления шиной, вырабатывается на время выполнения инструкции по префиксу LOCK и автоматически при выполнении инструкций XCHG с памятью, подтверждения прерывания и доступа к таблицам дескрипторов |

|

INTR |

I |

Interrupt Request – сигнал запроса (высоким уровнем) маскируемого прерывания |

|

Сигнал |

I/O |

Назначение |

|

NMI |

I |

Non Mascable Interrupt – сигнал, высокий уровень которого вызывает немаскируемое прерывание NMI |

|

RESET |

I |

Сигнал аппаратного сброса (высоким уровнем) |

|

HOLD HLDA |

I О |

Bus Hold Request и Hold Acknowledge – запрос управления локальной шиной от другого контроллера и подтверждение предоставления |

|

PEREQ |

I |

Processor Extension Operand Request – запрос на передачу операнда сопроцессором |

|

BUSY# ERROR# |

I I |

Processor Extension Busy и Error – сигналы состояния сопроцессора. Активность сигнала BUSY# останавливает процессор, а сигнала ERROR вызывает исключения при исполнении инструкций WAIT и некоторых инструкций ESCAPE |

У микропроцессора 386SX разрядность шины данных 16 бит - имеются только сигналы D[15:0], разрядность шины адреса 24 бит - А[23:1]. Синхронизация процессора осуществляется внешним сигналом CLK2, частота которого делится пополам внутренним делителем для получения сигнала внутренней синхронизации. Каждому периоду CLK2 соответствует одна из двух фаз внутренней синхронизации (фаза 1 или фаза 2). Максимальная пропускная способность локальной шины процессора – одно двойное слово за каждые два цикла внутренней частоты PCLK.

Шина адреса позволяет адресовать 16 Мб физической памяти (000000-FFFFFFh) в защищенном режиме и 1 Мб из области младших адресов в реальном режиме. Из этого правила для реального режима есть два исключения:

линии А[20:23] после сигнала RESET во время выборки кода находятся в единичном состоянии до первой инструкции межсегментного перехода;

линия А20 может принимать единичное значение, когда сочетание значения сегментного регистра и эффективного адреса приводят к переходу через границу 0FFFFFh (максимально возможное значение физического адреса в реальном режиме 01FFEFh). Для обеспечения полной совместимости с 8086 применяют программно управляемый вентиль (GATE A20), принудительно обнуляющий бит А20 системной шины адреса.

При выполнении инструкций ввода-вывода процессор адресуется к области в 64 Кб пространства ввода-вывода (000000-00FFFFh).

Линии А[23:1] идентифицируют адрес с точностью до слова, а в пределах этого слова сигналы ВHЕ#, ВLЕ# непосредственно указывают, какие байты используются в данном цикле. ВLЕ# относится к D[7:0], ВHЕ# – к D[15:8], при этом все байты могут быть только смежными.

Для связи с системной шиной, имеющей возможность подключения 8-битных устройств (шины ISA и EISA) и полную шину адреса, включающую сигналы АО и SBHE#, недостающие сигналы генерируются из сигналов ВHЕ#, ВLЕ# и необходим «косой» буфер данных между линиями D[15:8] процессора и Data[7:0] системной шины.

Тип цикла локальной шины определяется сигналами М/IO#, D/C#, W/R# и LOCK#, комбинация которых действительна во время активности сигнала ADS#.

Сигналы управления шиной ADS#, READY# и NA# задают временные границы циклов и управляют конвейерной адресацией. Сигнал ADS# отмечает начало каждого цикла, во время его действия производится идентификация типа цикла и фиксируется соответствующий ему адрес (линии А[23:1], ВHЕ#, ВLЕ#). Сигнал READY# должен вводиться внешней схемой в каждом цикле, отмечая готовность к завершению текущего цикла. Сигнал NA# используется для запроса следующего адреса при конвейерной адресации, когда внешние схемы уже готовы воспринять новый адрес и сигналы идентификации. Если процессор уже имеет внутренний запрос на следующий шинный цикл, он выдаст адрес и идентификаторы следующего цикла до завершения текущего.

Таблица 4-Декодирование шинных циклов МП 386

|

M/IO# |

D/C# |

W/R# |

Тип цикла |

|

0 |

0 |

0 |

Подтверждение прерывания (INTA#) |

|

0 |

1 |

0 |

Чтение порта (IOR#) |

|

0 |

1 |

1 |

Запись в порт (IOW#) |

|

1 |

0 |

1 |

Если ВЕ2# = 0 - останов (Halt), если ВЕ0# = 0 - отключение (Shutdown); при этом А[23:1]=0, а остальные BEi=l. |

|

1 |

0 |

0 |

Чтение кода программы(MEMR#) |

|

1 |

1 |

0 |

Чтение данных из памяти (MEMRD#) |

|

1 |

1 |

1 |

Запись данных в память (MEMWR#) |

Сигналы арбитража локальной шины предназначены для передачи управления локальной шиной другому устройству по его запросу - переходу в состояние лог. «1» линииHOLD. Когда процессор сочтет возможным передачу управления (в незаблокированных циклах сразу по завершении текущего шинного цикла), он выставит сигнал подтвержденияHLDA.