- •Минобрнауки россии

- •1. Задание на проектирование

- •Общие сведения

- •Техническое задание на проектирование

- •Варианты заданий

- •Формирование управляющего воздействия у1

- •Формирование управляющего воздействияY2

- •Формирование управляющего воздействияY3

- •Светодиодная индикация

- •Организация подсистемы прерываний

- •Выбор элементной базы

- •Реализуемый алгоритм

- •Требования к оформлению

- •Основные этапы разработки

- •Разработка микропроцессорного модуля

- •Описание элементной базы мпм

- •Микропроцессор i82386sx

- •Реализация системного контроллера

- •Шинные формирователи шин адреса и данных

- •Генератор тактовых импульсов и схема сброса

- •Реализация подсистемы прерываний

- •Разработка модуля ввода-вывода

- •Параллельно-программируемый адаптер кр580вв55

- •Разработка модуля таймера

- •Работа пит в режиме 0 (программируемый таймер)

- •Работа пит в режиме 3

- •Разработка памяти мпс

- •Распределение адресного пространства памяти

- •Разработка модулей пзу и озу

- •Распределение адресного пространства ввода/вывода

- •Разработка управляющей программы

- •Литература

Разработка модулей пзу и озу

Разработка памяти МПС должна начинаться с определения емкости, требуемой для размещения программ (ПЗУ) и данных (ОЗУ). Разрядность памяти должна соответствовать разрядности МП и равняться 16 бит. Техническим заданием на курсовой проект задаются конкретные типы ИС ОЗУ и ПЗУ. Если для реализации необходимого объема памяти оказывается недостаточно одной ИС ЗУ то используются несколько микросхем. Необходимое число K микросхем, требуемое для построения модулей ОЗУ и ПЗУ, определяется в соответствии с формулой:

где: N - требуемая разрядность модуля памяти;

![]() -

требуемая емкость модуля памяти;

-

требуемая емкость модуля памяти;

n - разрядность используемой микросхемы памяти;

![]() -

емкость используемой микросхемы памяти.

-

емкость используемой микросхемы памяти.

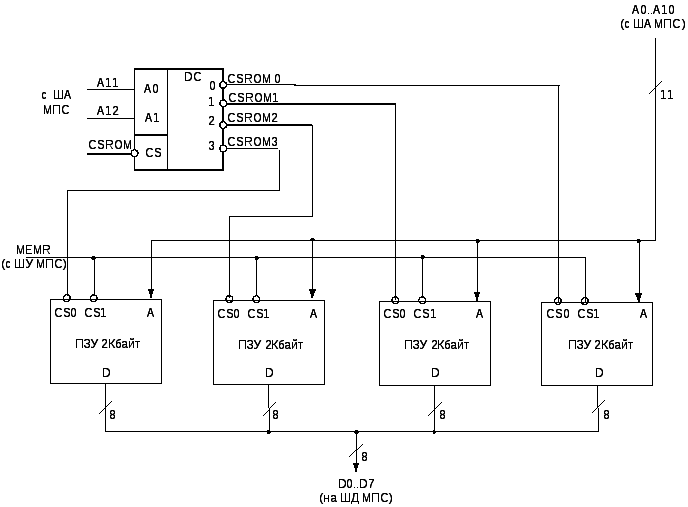

Пример организации модуля ПЗУ объемом 8 кбайт из 4-х микросхем ПЗУ объёмом 2к x 8бит приведен на рисунке 22.

Рисунок

22 - Пример организации модуля ПЗУ объемом

8 Кбайт из 4-х микросхем 2К x 8бит

Рисунок

22 - Пример организации модуля ПЗУ объемом

8 Кбайт из 4-х микросхем 2К x 8бит

Сигнал CSROM- выбор кристалла микросхемы ПЗУ, формируется ДША ОЗУ и ПЗУ. Для считывания информации с каждой из микросхем ПЗУ используется сигнал MEMR, вырабатываемый микросхемой СК. Младшие разряды адреса А0…А10 подаются параллельно на адресные входы всех микросхем ПЗУ. Два старших разряда адреса А11 и А12 используются для выработки сигналов CSROM0…CSROM3. Активизация этих сигналов возможна только при переходе в состояние лог. 0 сигнала CSROM.

Пример организации модуля оперативной памяти объемом 4 Кбайт из 4-х микросхем 1К x 8бит приведен на рисунке 23.

Рисунок 23 - Пример организации модуля ОЗУ 4 Кбайт из 4-х микросхем 1К x 8бит

Организация модуля ОЗУ имеет много общего с организацией модуля ПЗУ. Главным отличием является необходимость формирователя сигнала чтения/ записи R/W микросхем ОЗУ. Главной функцией формирователя является перекодировка сигналов чтения (MEMR) и записи (MEMW) памяти, выдаваемых микросхемой СК по отдельным линиям, в один общий сигнал чтения/ записи R/W (1/0), используемый для управления микросхемами ОЗУ.

Распределение адресного пространства ввода/вывода

В разрабатываемой МПС используется две микросхемы УВВ – ППА и ПИТ, в каждой из которых реализованы по четыре адресуемых устройства. Для микросхемы ППА это, соответственно, порты A, B и C (PA, PB и PC), а также регистр управляющего слова ППА (CWPPA). Для микросхемы ПИТ – это три таймера (T0, T1 и T2) и регистр управляющего слова ПИТ (CWPIT). В микросхеме ПКП адресуются 2 управляющих регистра.

Таким образом, из 65536 адресов адресного пространства ввода/вывода (АПУВВ), доступных МП, используется только 10.

Как и при распределении АПП, распределение адресов АПУВВ целесообразно произвести исходя из простоты реализации дешифратора АПУВВ. В связи с тем, что у процессора отсутствует адресная линия А0, нужно производить дешифрацию линий А4, А3, для адресации УВВ, а линиями А2, А1 адресовать внутренние регистры УВВ (рисунок 24).

Рисунок 24 – Распределение АПУВВ

Необходимо отметить, что при дешифрации только разрядов А0...A4 ША МП, эти адреса будут многократно отображаться на оставшуюся часть АПУВВ и при введении в МПС дополнительных УВВ необходим более сложный дешифратор.