- •Микропроцессор, микропроцессорная система (мпс) и микроконтроллер: определения. Классификационные признаки мпс: архитектура, система команд, назначение, разрядность.

- •Структура команд мп. Понятия командного цикла, машинного цикла и такта. Типы машинных циклов. Способы адресации операндов (на примере Intel 8085 / к1821вм85).

- •Этапы проектирования микропроцессорного контроллера на базе микроконтроллера. Выбор и обоснование структурной схемы. Способы подключения внешних устройств. Разработка управляющей программы.

- •Микроконтроллеры avr. Основные характеристики. Процессорный блок мк avr: состав операционного блока и устройства управления (на примере мк aTtiny2313)

- •Адресные пространства мк avr. Способы адресации памяти данных и памяти программ. Система команд мк avr (на примере мк aTtiny2313)

- •Арифметические и логические инструкции

- •Инструкции передачи данных

- •Современные тенденции в развитии микропроцессоров и микроконтроллеров. Основные производители и особенности современных микроконтроллеров и сигнальных процессоров.

- •Процессорные ядра arm: архитектура, расширения, сферы применения. Структура ядра Cortex-m3.

- •Цифровые сигнальные процессоры (цсп): специальные аппаратные ресурсы (умножители с накоплением, циклические буферы), приемы параллельной обработки данных (simd, vliw). Сферы применения цсп.

- •Программируемые логические интегральные схемы. Типы архитектур плис – fpga и cpld. Основные программируемые узлы плис. Перспективы развития плис.

-

Программируемые логические интегральные схемы. Типы архитектур плис – fpga и cpld. Основные программируемые узлы плис. Перспективы развития плис.

ПЛИС (программируемая логическая интегральная схема) –

интегральная схема высокой степени интеграции, у которой выполняемая логическая функция программируется после изготовления. Программируемыми являются соединения между вентилями, триггерами и другими элементами, расположенными на кристалле ПЛИС, а также большинство контактов микросхемы.

Информация о том, как именно будут соединены ресурсы ПЛИС и как будут использованы ее контакты, называется конфигурационным массивом, или файлом конфигурации. Файл конфигурации может храниться во встроенном ПЗУ ПЛИС или в отдельной микросхеме памяти.

Тактовые частоты, управляющие работой современных ПЛИС,

достигают сотен мегагерц.

Основными архитектурами ПЛИС являются:

-

CPLD (Complex Programmable Logic Device)

-

FPGA (Field Programmable Gates Array).

CPLD

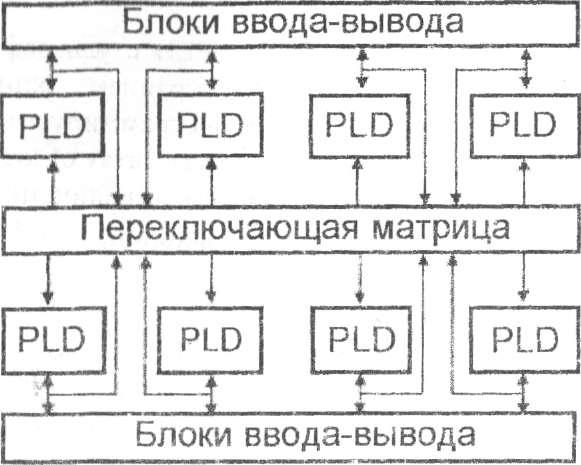

Основными компонентами CPLD являются (рисунок 1.2.3):

-

функциональные блоки (ФБ, они же PLD);

-

блоки ввода-вывода (БВВ, ЮВ)

-

переключающая матрица (ПМ, switch matrix).

Рисунок 1.2.3 - Архитектура CPLD

Каждый ФБ в CPLD ХС9500 имеет 18 макроячеек (МЯ), 36 входов и 18 выходов. К ПМ подводятся 18 выходов каждого ФБ; через ПМ проходят на ФБ входные сигналы, поступающие на блоки ввода-вывода. В зависимости от количества контактов корпуса CPLD от 12 до 18 информационных и управляющих выходов каждого ФБ поступают непосредственно на блоки ввода-вывода (минуя ПМ).

Макроячейка - элемент функционального блока, содержащий комбинационную логику и триггер.

Каждый контакт ПЛИС, обозначенный «I/O», можно использовать в качестве входа, выхода или двунаправленною вывода в соответствии с файлом конфигурации.

Функциональный блок (ФБ)

ФБ позволяет реализовывать устройства с 36 входами и 18 выходами. К ФБ подключены глобальные сигналы - GSR и GCK. 18 информационных выходов ФБ (OUT) подключены к ПМ. Эти 18 сигналов, а также соответствующие им 18 сигналов разрешения выхода (РТОЕ, product term output enable) подключаются также и к блокам ввода-вывода непосредственно.

Каждый из элементов «И» доступен для любой макроячейки, однако, у каждой из них есть «персональные» элементы «И», подключаемые к ним без дополнительных временных задержек.

Подключение выходов элементов «И» к входам макрояче- ск выполняется распределителем термов-произведений.

Архитектура FPGА.

FPGA (field programmable gates array) можно перевести как «массив программируемых вентильных матриц».

Прототипами FPGA являются БМК, которые в англоязычной литературе называют также вентильными матрицами (Gate Arrays),

Структура БМК и ранних FPGA БМК

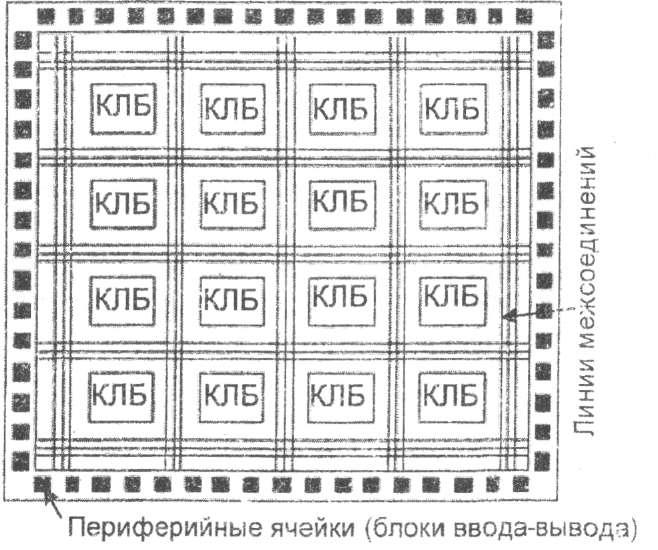

Но внутренней области по строкам и столбцам (в виде матрицы) расположены базовые ячейки - группы коммутированных схемных элементов (транзисторов, резисторов). Между строками и столбцами базовых ячеек или их компактных групп оставляются горизонтальные и вертикальные свободные зоны (каналы) для межсоединений. В периферийной области кристалла размещаются ячейки, выполняющие операции ввода/вывода сигналов через контактные площадки, расположенные по краям кристалла.

Первые FPGA были предложены в 1984 году фирмой Xilinx, Структура FPGA та же, что и у БМК. Только у FPGA функциональные ячейки называются конфигурируемыми логическими блоками (КЛБ), а периферийные ячейки - блоками ввода-вывода (БВВ). Сохранена и возможность размещения на кристалле подматриц для выполнения заранее определенных функций. По этому принципу на более поздних FPGA размещаются блочное ОЗУ, аппаратные умножители и другие специализированные аппаратные узлы, о которых речь пойдет позже. Разница между БМК и FPGA состоит в том, что FPGA, поступающая в распоряжение потребителя, имеет уже запрограммированные, трассировочные ресурсы (межсоединения), не зависящие от конкретного потребителя. Получение конкретного проекта на основе FPGA реализуется воздействием на программируемые межсоединения, в ходе которого обеспечивается замкнутое состояние одних, участков и разомкнутое — других. Обращаться к изготовителю FPGA при этом не требуется.

FPGA, помимо КЛБ, БВВ и линий межсоединений, содержит конфигурационное ОЗУ (CRAM), ячейки которого которая управляет соединениями логических элементов. При конфигурировании FPGA КЛБ настраиваются на выполнение необходимых операций преобразования данных, а система межсоединений — на требуемые связи между КЛБ. В результате во внутренней области FPGA реализуется схема нужной конфигурации. Расположенные по краям кристалла блоки ввода-вывода обеспечивают интерфейс FPGA с внешней средой. Блоки ввода-вывода современных FPGA можно программировать на выполнение требований множества стандартов передачи данных.

Конфигурируемые логические блоки (КЛБ)

В КЛБ можно выделить три вида ресурсов - набор мультиплексоров, запоминающий элемент (триггер) и табличный преобразователь, реализующий логические функции нескольких переменных.

Мультиплексоры служат для расширения возможностей табличного преобразователя, управления подачей управляющих сигналов на триггер и формирования выходов КЛБ. Кроме того, мультиплексоры используются для выбора тактового и управляющего сигналов триггера и формирования одной из переменных для табличного преобразователя.

Запоминающий элемент (триггер) для хранения значения одной из логических функций.

Табличные преобразователи (LUT)

Табличный преобразователь - универсальный элемент, служащий для выработки любых комбинационных функций нескольких переменных.

Реализация комбинационных схем в FPGA принципиально отличается от их реализации в CPLD. В функциональных блоках CPLD программируемая комбинационная схема представляет собой наборы вентилей «И» и «ИЛИ» и позволяет реализовывать функции вида «дизъюнкция конъюнкций», что соответствует дизъюнктивной нормальной форме.

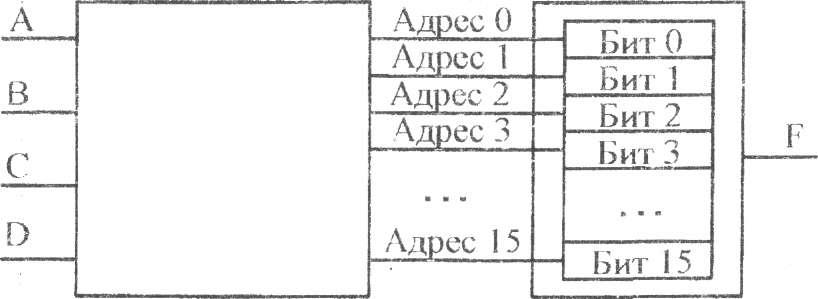

В FPGA табличный преобразователь (рисунок 1.3.2) позиционируется как устройство, позволяющее вычислять любую комбинационную функцию нескольких переменных. Реализация блока значительно облегчается для производителя ПЛИС, если представить его не в виде набора вентилей с программируемыми соединениями, а в виде I-разрядного статического ОЗУ с несколькими адресными вводами, соответствующими входным переменным (рисунок 1.3.3). Подавая на адресные входы памяти четыре входных бита, получаем на выходе значение функции для этой комбинации значений переменных.

Дешифратор \

-разрядное

адреса ОЗУ

Рисунок

1.3.3

- Табличный преобразователь

ОД/Г) Фактически, функция 4-х переменных

представляется в виде таблицы истинности.

Отсюда и название «табличный

преобразователь», или, в исходном

варианте, «Look-up

Table».

LUT.