- •Микропроцессор, микропроцессорная система (мпс) и микроконтроллер: определения. Классификационные признаки мпс: архитектура, система команд, назначение, разрядность.

- •Структура команд мп. Понятия командного цикла, машинного цикла и такта. Типы машинных циклов. Способы адресации операндов (на примере Intel 8085 / к1821вм85).

- •Этапы проектирования микропроцессорного контроллера на базе микроконтроллера. Выбор и обоснование структурной схемы. Способы подключения внешних устройств. Разработка управляющей программы.

- •Микроконтроллеры avr. Основные характеристики. Процессорный блок мк avr: состав операционного блока и устройства управления (на примере мк aTtiny2313)

- •Адресные пространства мк avr. Способы адресации памяти данных и памяти программ. Система команд мк avr (на примере мк aTtiny2313)

- •Арифметические и логические инструкции

- •Инструкции передачи данных

- •Современные тенденции в развитии микропроцессоров и микроконтроллеров. Основные производители и особенности современных микроконтроллеров и сигнальных процессоров.

- •Процессорные ядра arm: архитектура, расширения, сферы применения. Структура ядра Cortex-m3.

- •Цифровые сигнальные процессоры (цсп): специальные аппаратные ресурсы (умножители с накоплением, циклические буферы), приемы параллельной обработки данных (simd, vliw). Сферы применения цсп.

- •Программируемые логические интегральные схемы. Типы архитектур плис – fpga и cpld. Основные программируемые узлы плис. Перспективы развития плис.

ВОПРОСЫ К ГОСЭКЗАМЕНУ

Дисциплина: «Микропроцессорные системы»

(ведущий преподаватель— Сальников И.И.)

-

Микропроцессор, микропроцессорная система (мпс) и микроконтроллер: определения. Классификационные признаки мпс: архитектура, система команд, назначение, разрядность.

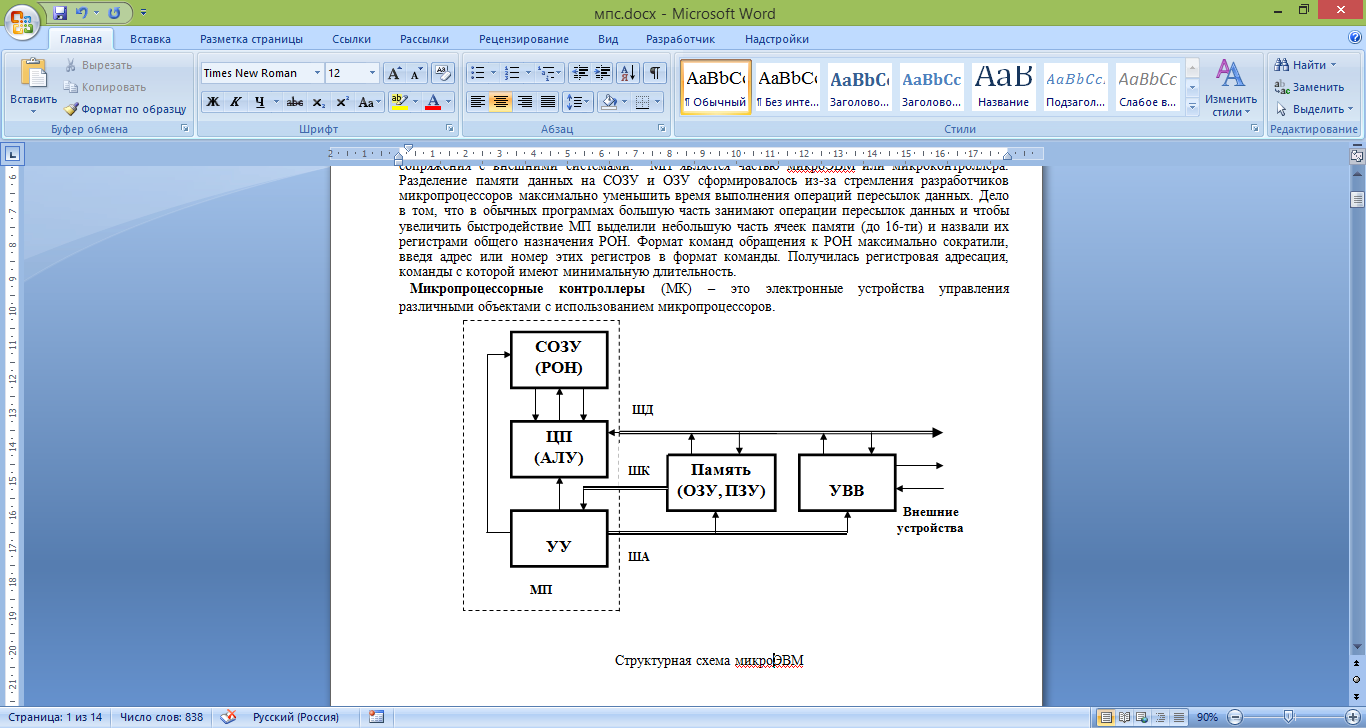

Микропроцессор (МП) – это программно-управляемое устройство в виде большой интегральной схемы (БИС), в которой на одном кристалле размещены – арифметико-логическое устройство (АЛУ), сверхоперативное запоминающее устройство (СОЗУ) и устройство управления (УУ). МП не имеют внутренней памяти программы и устройства ввода/вывода для сопряжения с внешними системами. МП является частью микроЭВМ или микроконтроллера. Разделение памяти данных на СОЗУ и ОЗУ сформировалось из-за стремления разработчиков микропроцессоров максимально уменьшить время выполнения операций пересылок данных. Дело в том, что в обычных программах большую часть занимают операции пересылок данных и чтобы увеличить быстродействие МП выделили небольшую часть ячеек памяти (до 16-ти) и назвали их регистрами общего назначения РОН. Формат команд обращения к РОН максимально сократили, введя адрес или номер этих регистров в формат команды. Получилась регистровая адресация, команды с которой имеют минимальную длительность.

Микропроцессорные контроллеры (МК) – это электронные устройства управления различными объектами с использованием микропроцессоров.

Структурная схема микроЭВМ

Архитектура микроконтроллера – это логическая организация микроконтроллера, определяемая возможностями микропроцессора по аппаратной или программной реализации требуемых функций. Типы архитектур микроконтроллеров:

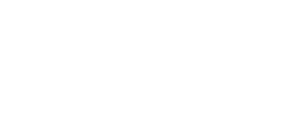

1. Архитектура с Q-шиной. Для этого типа архитектуры МК характерной особенностью является совмещение ШД, ША, ШК. При этом по организации памяти – это архитектура фон-Неймановского типа, а по способу управления – это архитектура с программным управлением, то есть CISC-архитектура.

При совмещение

ШД, ША, ШК в каждом цикле выполнения

команды последовательно по Q-шине

передаются: адрес команды, команда из

ПЗУ, адрес данных, данные в ОЗУ или из

ОЗУ. Необходимым условием работы такой

структуры является наличие интерфейса

(ИФ) в каждом устройстве, подключаемом

к Q-шине.

ИФ дешифрирует адрес и разрешает работу

своего устройства. При этом дополнительно

используются служебные сигналы от МП,

которые передают признак передачи

адреса по Q-шине

и признак режима работы – чтение или

запись данных во внешние устройства.

Совмещение шин позволило уже на начальном этапе развития МП реализовать операции с 16-ти разрядными данными, тогда как другие типы архитектур предполагали использование лишь 4-х и 8-ми разрядных ШД.

Достоинством данного типа архитектуры МК является простота в организации МК и возможность наращивания разрядности данных.

Недостатком - снижение быстродействия из-за последовательного способа передачи по совмещенной шине адресов, команд и данных.

Для данного типа архитектуры МК в нашей стране были разработаны микропроцессорные комплекты (МПК) К581, К588, К1801, К1806, К1811 и т.д., на базе которых отечественной промышленностью в 80-е годы был освоен выпуск первых ПЭВМ - «Электроника-60» и многочисленных ее модификаций. Развитием этого направления был выпуск ПЭВМ типа ДВК-1,2,3,4, а также “Электроника-85”.

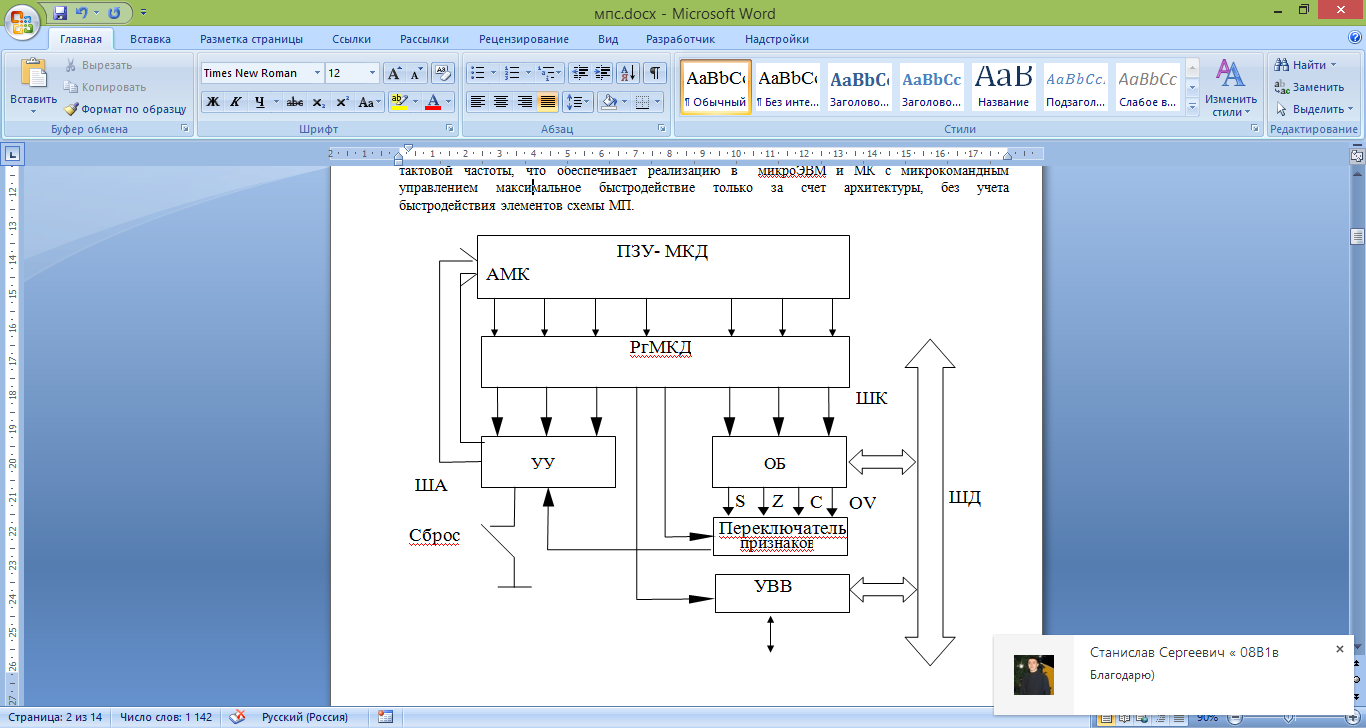

2. Архитектура с микрокомандным управлением. Для данного типа архитектуры МК характерными признаками является раздельное существование ШД, ША, ШК. При этом по организации памяти – это архитектура гарвардского типа, а по способу управления – это архитектура с микропрограммным управлением, то есть RISC-архитектура.

При микрокомандном

управлении каждый разряд микрокоманды

управляет соответствующим устройством

МП. Такой способ управления характеризуется

определенной избыточностью, так как

большое количество устройств в МП

используется крайне редко, а управляющие

разряды для них выделены и должны

присутствовать в микрокоманде. Но

микрокомандное управление позволяет

реализовать чтение команды из памяти

и выполнение ее за один

такт основной

тактовой частоты, что обеспечивает

реализацию в микроЭВМ и МК с микрокомандным

управлением максимальное быстродействие

только за счет архитектуры, без учета

быстродействия элементов схемы МП.

Последовательность работы МК следующая:

-

после включения питания или снятия сигнала “Сброс” УУ формирует на ША начальный адрес программы. Это, как правило, нулевой адрес;

-

в ПЗУ-МКД читается первая микрокоманда, разряды которой управляют различными устройствами МП;

-

на выходе ПЗУ-МКД включен регистр-защелка РгМКД, который выполняет привязку фронтов микрокоманды из ПЗУ к фронту тактовой последовательности Т и исключает ложные срабатывания устройств МП;

-

разряды микрокоманды определяют шину управления ШК;

-

часть разрядов ШК управляют операционным блоком (ОБ). В результате выполнения операции в ОБ формируются признаки: S-знак результата, Z-нулевой результат, C-перенос, OV-переполнение разрядной сетки;

-

если реализуется команда условного перехода, то переключатель признаков по управляющим разрядами ШК выбирает соответствующий признак и подает его на вход УУ;

-

УУ формирует адрес следующей микрокоманды.

Особенностью данной архитектуры является то, что все управляющие разряды ШК читаются параллельно, отсутствует фаза дешифрирования управляющего кода и микрокоманда выполняется за один такт. Таким образом реализуется максимально возможное быстродействие МК.

Недостатком данного типа архитектуры МК является большие аппаратные затраты и избыточность микрокоманды. Но благодаря открытой архитектуре микрокоманда может иметь сокращенный размер, если количество функций контроллера ограничено.

Для данного типа архитектуры МК в нашей стране были разработаны микропроцессорные комплекты К589, К1800, К1802, К1804 (аналог Am2900 фирмы AMD), К1822 и другие, на базе которых отечественной промышленностью в 80-е годы был освоен выпуск ЭВМ – СМ1300, СМ1420, СМ1700 и других.

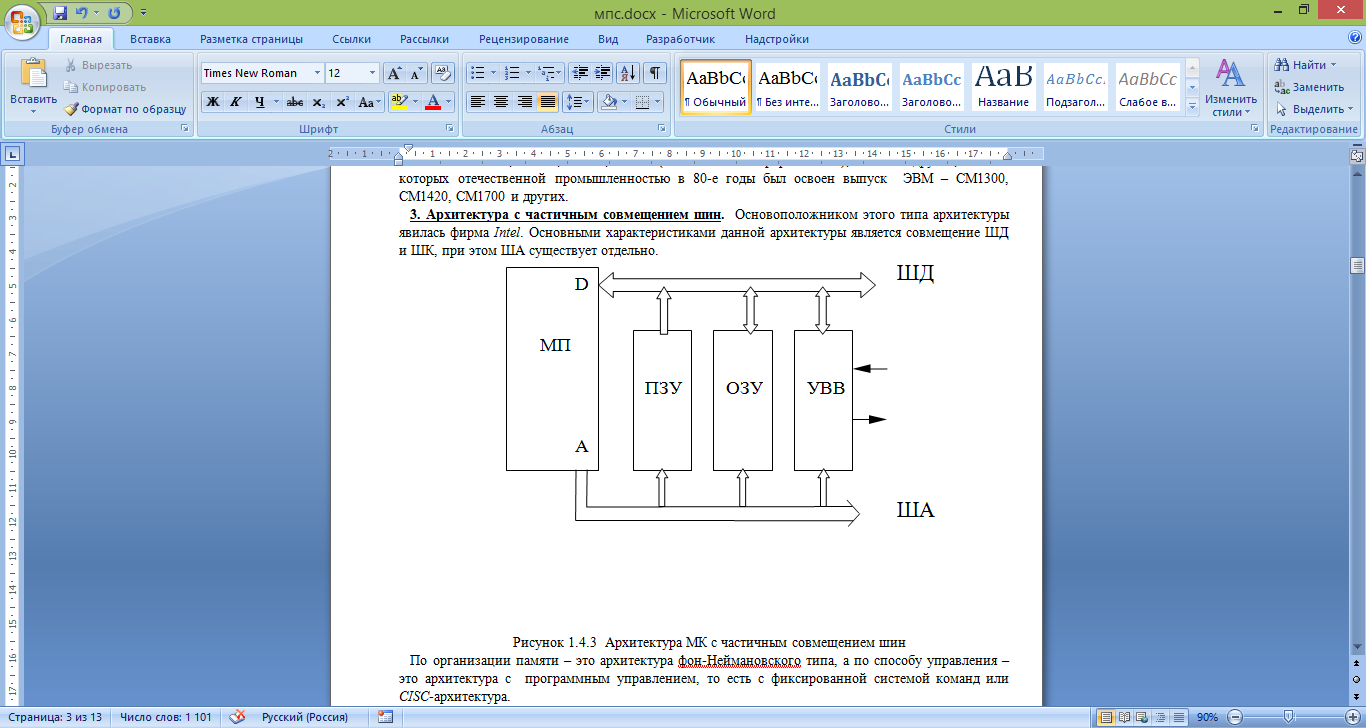

3. Архитектура с частичным совмещением шин. Основоположником этого типа архитектуры явилась фирма Intel. Основными характеристиками данной архитектуры является совмещение ШД и ШК, при этом ША существует отдельно.

По организации

памяти – это архитектура фон-Неймановского

типа, а по способу управления – это

архитектура с программным управлением,

то есть с фиксированной системой команд

или CISC-архитектура.

В каждом цикле выполнения команды по ШД сначала передаются команды, а потом данные. С точки зрения достоинств и недостатков данная архитектура носит промежуточный характер между двумя типами архитектур МК, рассмотренных выше.

Этот тип архитектуры также был успешно освоен отечественной промышленностью. Были разработаны микропроцессорные комплекты К580, К1810, К1821, К1858 (аналог – Z80 фирмы Zilog) и т.д., на базе которых отечественной промышленностью в 70-е и 80-е годы выпускались ПЭВМ – СМ1800, СМ1810, Искра 1030, ЕС1840, Нейрон И6.99.

-

Состав классического микропроцессора: операционный блок, блок регистров, дешифратор команд, схема синхронизации и управления, устройство управления прерываниями, шина данных (на примере Intel 8085 / К1821ВМ85)

Приведем технические характеристики КР1821ВМ85:

- шина данных – 8 разрядов;

- шина адреса - 16 разрядов;

- адресное пространство – 64 кбайта;

- число программно-доступных регистров – 7 (A,B,C,D,E,H,L);

- длина команд – от 1 до 3 байт;

- число уровней прерывания – 5;

- число внешних УВВ – 256;

- тактовая частота – 4 МГц.

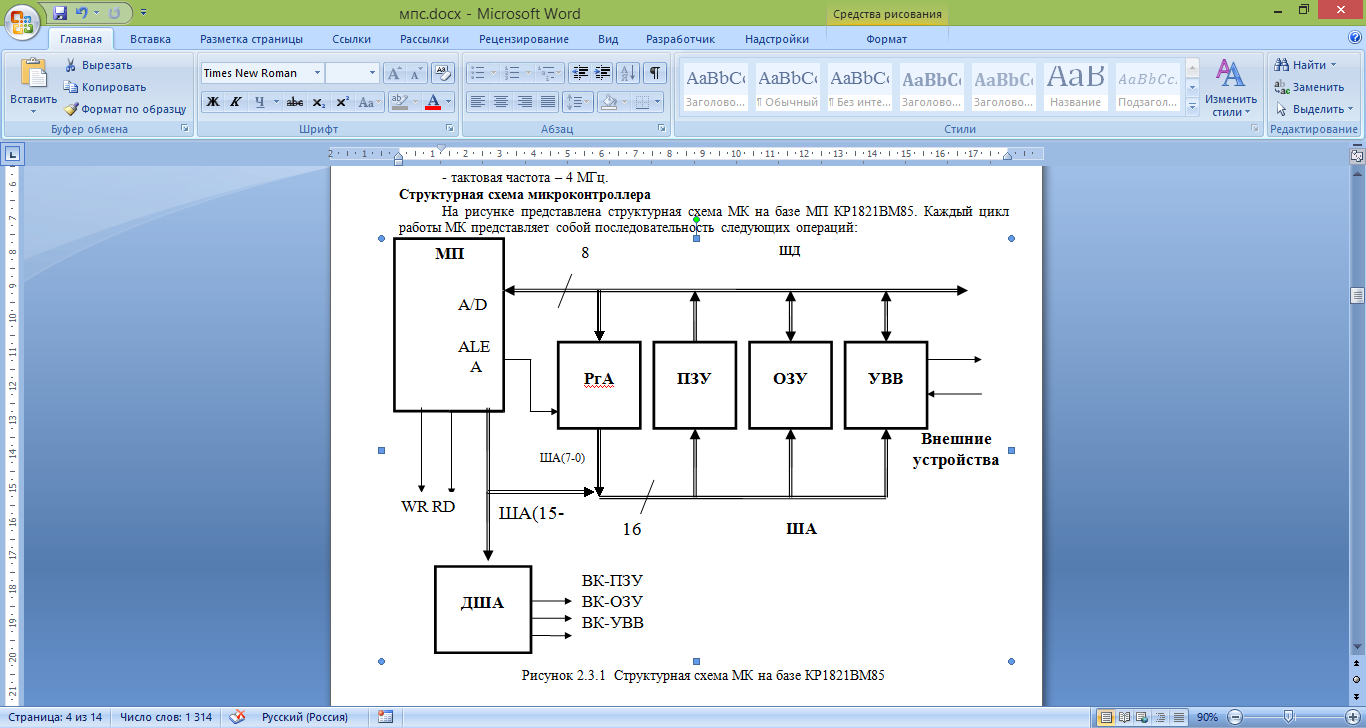

Структурная схема микроконтроллера

На рисунке представлена структурная схема МК на базе МП КР1821ВМ85. Каждый цикл работы МК представляет собой последовательность следующих операций:

- на ША выставляется адрес команды, причем старший байт адреса сразу выставляется на разрядах ША15-ША8, а младший байт – на ШД;

- по заднему фронту сигнала ALE младший байт фиксируется в регистре адреса РгА, после чего на ША формируется 16-ти разрядный адрес;

- дешифратор адреса ДША формирует сигналы выбора устройств (кристалла) ВК, по которому разрешается обращение к соответствующему устройству МК;

- в режиме записи данных во внешние устройства (ОЗУ, УВВ) на ШД микропроцессор выставляет данные и формирует сигнал WR, по которому данные записываются в соответствующее внешнее устройство;

- в режиме чтения по разрешающему сигналу с ДША и соответствующему адресу на ША внешнее устройство выставляет код, который по сигналу RD читается микропроцессором;

- одновременно с выполнением текущей команды в МП формируется адрес следующей команды, который загружается в программный счетчик PC.