- •I. Общие сведения о системеorcad

- •II. Создание иерархических блоков

- •III. Запись иерархического блока в библиотеку и вставка блока из библиотеки в схему

- •IV. Моделирование

- •«Ознакомление с системой orcad»

- •Порядок выполнения работы

- •«Создание и работа с библиотекой элементов»

- •Порядок выполнения работы

- •«Создание штампа основной надписи»

- •Порядок выполнения работы

- •I. Способ первый

- •II. Способ второй

- •«Моделирование работы цифровых устройств»

- •1. Создание проекта pc Board

- •2. Инструменты, используемые при моделировании

- •3. Установка параметров моделирования

- •«Моделирование цифровых устройств на основе логических эЛеМентов»

- •1. Логические элементы

- •2. Кодер

- •3. Декодер

- •Задание на лабораторную работу:

- •«Моделирование цифровых устройств на основе логических эЛеМентов»

- •1. Мультиплексор

- •2. Демультиплексор

- •Задание на лабораторную работу:

- •«Моделирование цифровых устройств на основе логических эЛеМентов»

- •1. Сумматор по модулю 2 (узел неравнозначности).

- •2. Полусумматор

- •Задание на лабораторную работу:

- •«Моделирование цифровых устройств на основе логических эЛеМентов»

- •1. Коммутатор

- •2. Компаратор

- •Задание на лабораторную работу:

- •«Моделирование триггеров на основе логических эЛеМентов»

- •1. Общие понятия

- •2. Классификация триггеров

- •3. Rs–триггер

- •4. Синхронные rs–триггеры

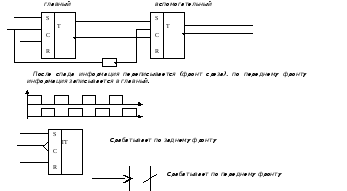

- •5. Двухтактный (двухступенчатый) синхронный rs–триггер:

- •6. Триггер т–типа (триггер с четным запуском)

- •7. D–триггер (триггер задержки)

- •8. Jk–триггер:

- •Задание на лабораторную работу:

- •Приложение 1.

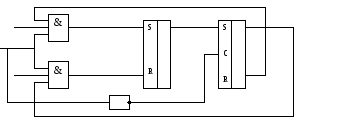

4. Синхронные rs–триггеры

|

tn |

tn+1 | ||

|

Сn |

Rn |

Sn |

Qn+1 |

|

0 |

* |

* |

Qn |

|

1 |

0 |

0 |

Qn |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

X |

где * – любое значение, Х – неопределенное состояние

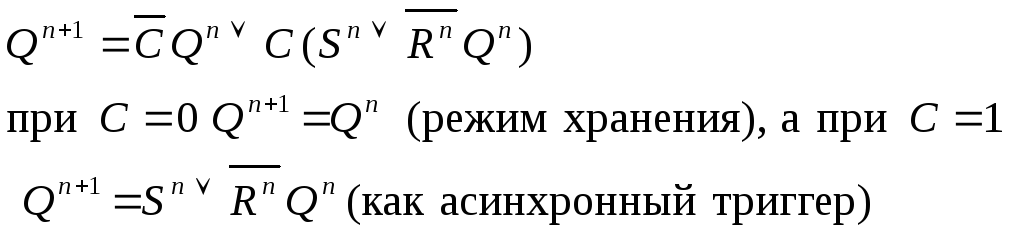

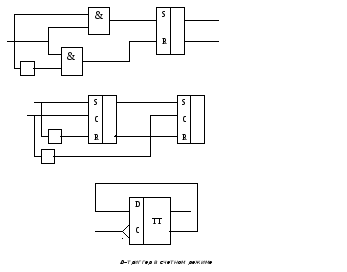

5. Двухтактный (двухступенчатый) синхронный rs–триггер:

Для многих применений необходимо, чтобы триггер изменял свое состояние не во время действия тактовых импульсов, а после его окончания, т.е. необходимо, чтобы информация на выходе появилась после того, как входы триггера окажутся запертыми.

Синхронный триггер обычно имеет дополнительные синхронные входы, по которым он в не зависимости от сигнала на тактовом входе переключается в состояние 1 (вход S) или 0 (вход R). Такие входы называют нетактируемыми (входы предустановки или очистки). Он позволяют установить триггер в нужное начальное положение.

Функциональная схема двухтактовый триггера с асинхронными входами на элементах Шеффера представлена ниже:

6. Триггер т–типа (триггер с четным запуском)

Т–триггер – это логическое устройство с двумя устойчивыми состояниями и одним входом Т. Устройство изменит свое состояние на противоположное всякий раз, когда на вход Т поступает управляющий (счетный) импульс.

Таблица переключений:

|

tn |

tn+1 | |

|

Qn |

Тn |

Qn+1 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

|

Tn |

Qn+1 |

|

0 |

|

|

1 |

|

![]()

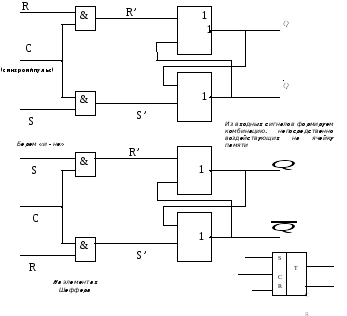

Т–триггер

можно выполнить на базе синхронного

RS–триггера, если перед приходом каждого

тактового импульса иметь на информационных

входах потенциалы, которые после

переключения должны быть на выходах

![]() и

и![]() .

Такими потенциалами до переключения

обладают соответственно выходы

.

Такими потенциалами до переключения

обладают соответственно выходы![]() и

и![]() ,

т.к в результате переключения выходы

любого триггера по существу обмениваются

потенциалами. Т–триггер можно реализовать

на основе синхронного RS–триггера.

,

т.к в результате переключения выходы

любого триггера по существу обмениваются

потенциалами. Т–триггер можно реализовать

на основе синхронного RS–триггера.

7. D–триггер (триггер задержки)

D–триггер – это логическое устройство с двумя устойчивыми состояниями и одним входом D.

-

Dn

Qn+1

0

0

1

1

Данная таблица показывает, что состояние триггера в момент времени tn+1 совпадает с кодом входного сигнала, действующего в момент времени tn, т.е осуществляется задержка входного сигнала.

Схема DV–триггера (для блокировки триггера используется вход V):

8. Jk–триггер:

JK–триггер – это логическое устройство с двумя устойчивыми состояниями и двумя входами J и K, которое при условии, если J = K= 1, осуществляет инверсию своего предыдущего состояния:

![]() ,

,

а в остальных случаях функционирует как обычный RS–триггер, причем эквивалентными являются входы J и S, K и R соответственно.

Таблица функционирования JK-триггера:

|

tn |

tn+1 | ||

|

Qn |

Jn |

Kn |

Qn+1 |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

|

tn |

tn+1 | |

|

Jn |

Kn |

|

|

0 |

0 |

|

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

|

![]()

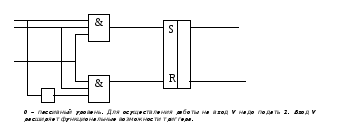

Функциональная схема на основе RS–триггера: