- •I. Общие сведения о системеorcad

- •II. Создание иерархических блоков

- •III. Запись иерархического блока в библиотеку и вставка блока из библиотеки в схему

- •IV. Моделирование

- •«Ознакомление с системой orcad»

- •Порядок выполнения работы

- •«Создание и работа с библиотекой элементов»

- •Порядок выполнения работы

- •«Создание штампа основной надписи»

- •Порядок выполнения работы

- •I. Способ первый

- •II. Способ второй

- •«Моделирование работы цифровых устройств»

- •1. Создание проекта pc Board

- •2. Инструменты, используемые при моделировании

- •3. Установка параметров моделирования

- •«Моделирование цифровых устройств на основе логических эЛеМентов»

- •1. Логические элементы

- •2. Кодер

- •3. Декодер

- •Задание на лабораторную работу:

- •«Моделирование цифровых устройств на основе логических эЛеМентов»

- •1. Мультиплексор

- •2. Демультиплексор

- •Задание на лабораторную работу:

- •«Моделирование цифровых устройств на основе логических эЛеМентов»

- •1. Сумматор по модулю 2 (узел неравнозначности).

- •2. Полусумматор

- •Задание на лабораторную работу:

- •«Моделирование цифровых устройств на основе логических эЛеМентов»

- •1. Коммутатор

- •2. Компаратор

- •Задание на лабораторную работу:

- •«Моделирование триггеров на основе логических эЛеМентов»

- •1. Общие понятия

- •2. Классификация триггеров

- •3. Rs–триггер

- •4. Синхронные rs–триггеры

- •5. Двухтактный (двухступенчатый) синхронный rs–триггер:

- •6. Триггер т–типа (триггер с четным запуском)

- •7. D–триггер (триггер задержки)

- •8. Jk–триггер:

- •Задание на лабораторную работу:

- •Приложение 1.

2. Классификация триггеров

В соответствии с функциональной классификацией различают триггеры:

- RS (с раздельными управляющими сигналами);

- Т (счетный);

- D (задержки);

- DV;

- JK (универсальный).

Классификация по способу записи информации характеризует временную диаграмму работы триггера, т.е. определяет ход процесса записи информации в триггер. По этой классификации триггеры разделяются на 2 группы:

- Асинхронные;

- Синхронные.

Запись информации в асинхронный триггер осуществляется непосредственно с поступлением информационного сигнала на вход триггера. В асинхронных триггерных устройствах синхронные (тактовые) входы отсутствуют. Запись информации в синхронные триггеры, имеющие информационные и тактовые входы, осуществляется только при подаче разрешающего тактирующего импульса.

Триггеры снабжаются различными типами входов:

- S (SET) – установка; раздельный вход установки состояния в 1;

- R (RESET) – сброс; раздельный вход установки состояния в 0;

- K – установка универсального триггера в состояние 0;

- J – установка универсального триггера в состояние 1;

- T – счетный вход;

- D (DELAY) – задержка; информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

- С – исполнительный управляющий (синхронизированный) вход;

- V – разрешающий (управляющий вход).

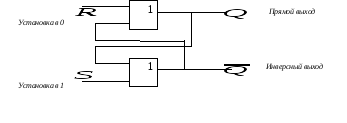

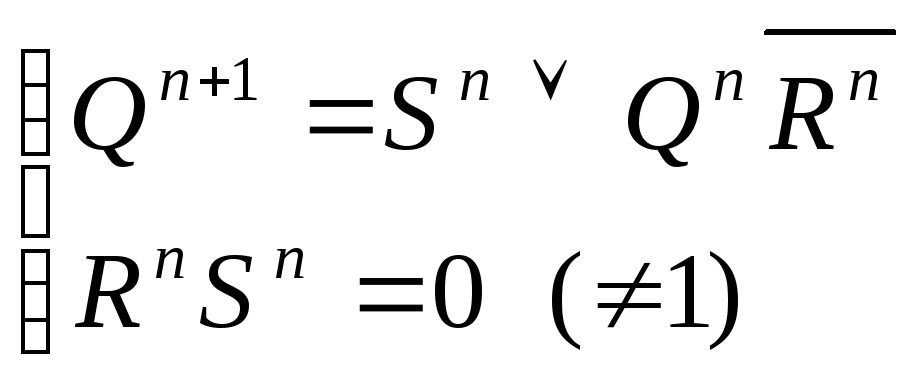

3. Rs–триггер

Два информационных входа: R и S. Если S = 1, R = 0, то триггер в состояние 1. Если S = 0, R = 1, то триггер в состояние 0.

Асинхронный RS–триггер представлен на рисунке ниже:

|

R |

S |

Qn+1 |

|

0 |

0 |

Qn |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

x |

|

tn |

tn+1 | ||

|

Qn |

Rn |

Sn |

Qn+1 |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

X |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

X |

![]()

|

x |

x |

1 |

1 |

|

0 |

0 |

1 |

0 |

t переключения = 2 t задержки

|

tn |

tn+1 | ||

|

Sn |

Rn |

Qn+1 | |

|

0 |

0 |

Х | |

|

0 |

1 |

1 | |

|

1 |

0 |

0 | |

|

1 |

1 |

Qn | |

На входы логического элемента или устройства сигналы не всегда поступают одновременно, т.к. перед этим они могут проходить через разное число узлов, не обладающих к тому же одинаковой задержкой. Это явление – состязание (гонка). В результате его в течение некоторого времени на входах создается неопределенная ситуация: новые значения одних сигналов сочетаются с предыдущими значениями других сигналов, что может привести к ложному срабатыванию элемента или устройства. Последствия гонки можно устранить временным стробированием, когда на входы триггера кроме информационных подаются тактирующие (синхронные) импульсы, к моменту которых информационные сигналы заведомо успевают восстановиться на входах.