- •Вычислительные машины (конспект лекций) однопроцессорные эвм

- •Часть 2

- •4.1. Структура памяти эвм 7

- •4.1. Структура памяти эвм

- •4.2. Способы организации памяти

- •4.2.1. Адресная память

- •4.2.2. Ассоциативная память

- •4.2.3. Стековая память (магазинная)

- •4.3. Структуры адресных зу

- •4.3.1. Зу типа 2d

- •4.3.2. Зу типа 3d

- •4.3.3. Зу типа 2d-м

- •4.4. Элементы зу с произвольным обращением

- •4.4.1. Зэ на ферритовых кольцах

- •4.4.2. Зэ на полупроводниковых элементах

- •4.5. Постоянные зу (пзу, ппзу)

- •4.6. Флэш-память

- •Вопросы для самопроверки

- •Контрольные задания

- •5. Структура и форматы машинных команд, способы адресации

- •5.1. Общие замечания

- •5.2. Возможные структуры машинных команд

- •5.3. Способы адресации

- •5.4. Команды передачи управления

- •5.4.1. Команды безусловного перехода (бп)

- •5.4.2. Команды условного перехода (уп)

- •5.4.3. Команды перехода на подпрограмму

- •5.5. Индексация

- •Вопросы для самопроверки

- •Контрольные задания

- •6. Принципы организации систем прерывания программ

- •6.1. Характеристики систем прерывания

- •6.2. Возможные структуры систем прерывания

- •6.3. Организация перехода к прерывающей программе

- •6.3.1. Реализация фиксированных приоритетов

- •6.3.2. Реализация программно-управляемых приоритетов

- •Вопросы для самопроверки

- •Контрольные задания

- •7. Простейшая микроэвм

- •7.1. Системный интерфейс микроэвм. Цикл шины

- •7.2. Промежуточный интерфейс

- •7.3. Мп с фиксированной системой команд

- •7.3.1. Регистры данных

- •7.3.2. Арифметико-логическое устройство

- •7.3.3. Регистр признаков

- •7.3.4. Блок управления

- •7.3.5. Буферы

- •7.3.6. Мп с точки зрения программиста

- •7.4. Мп-устройство на основе мп кр580вм80а

- •7.5. Форматы данных мп кр580

- •7.6.Форматы команд мп 580вм80

- •7.7. Способы адресации

- •7.8. Система команд мп 580

- •7.8.1. Пересылки однобайтовые

- •7.8.2. Пересылки двухбайтовые

- •7.8.3. Операции в аккумуляторе

- •7.8.4. Операции в рон и памяти

- •7.8.5. Команды управления

- •Вопросы для самопроверки

- •Контрольные задания

5.4. Команды передачи управления

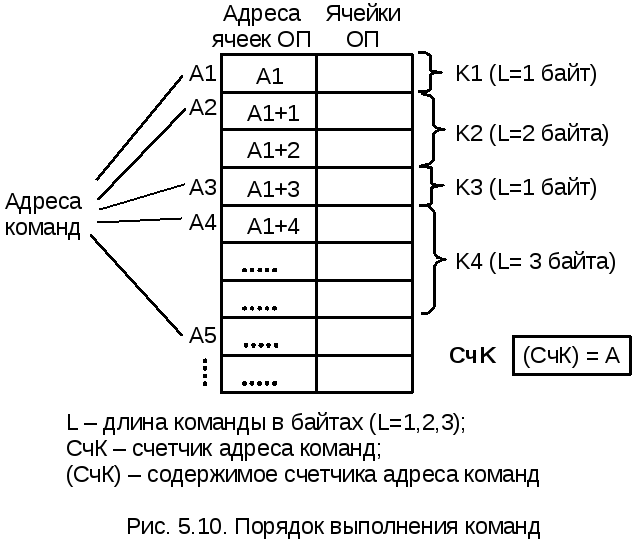

Ранее уже отмечалось, что порядок выполнения команд может быть естественным и принудительным. При естественном порядке после выполнения очередной команды выбирается команда, расположенная в следующей по порядку ячейке памяти. Обычно адрес команды хранится в специальном регистре, называемом счетчиком адреса команд или простосчетчиком команд(СчК), содержимое которого после выполнения каждой команды увеличивается на 1. Если же память имеет побайтную адресацию, то на столько байт, сколько их содержит текущая команда. Цикл выборки/выполнения команд можно пояснить схемой, приведенной на рис. 5.10. Пусть L – длина команды в байтах, а память имеет побайтную адресацию. Порядок выполнения команд на рис. 5.10 следующий:

Выборка команды по адресу А=А1 (К1).

Дешифровка команды, в том числе определение ее длины L (L=1).

Вычисление адреса следующей команды (СчК) = (СчК) + 1 (К2).

Выполнение команды (К1).

Выборка команды по адресу А2 (К2).

Дешифровка команды, в том числе определение ее длины L (L=2).

Вычисление адреса следующей команды (СчК) = (СчК) + 2.

Выполнение команды (К2).

Далее циклы выборки/выполнения команд К3, К4, … повторяются.

Естественный порядок выполнения команд может быть нарушен командами передачи управления(командами перехода). Следует иметь в виду, что нарушение порядка выполнения команд возможно и в ряде других случаев, важнейший из которых – обработка запросов прерывания – будет рассмотрен в дальнейшем (см. п. 6).

И звестны

многочисленные варианты команд перехода,

однако общий принцип состоит в том, что

адресная часть команды перехода

непосредственно или после суммирования

с содержимым базового регистра загружается

в СчК. В результате после выполнения

такой команды может быть выполнена

команда из любой ячейки памяти,

определяемой адресной частью команды

перехода. Для упрощения рассмотрим

команды перехода без относительной

адресации. Кроме того, предполагается,

что память имеет побайтную адресацию.

звестны

многочисленные варианты команд перехода,

однако общий принцип состоит в том, что

адресная часть команды перехода

непосредственно или после суммирования

с содержимым базового регистра загружается

в СчК. В результате после выполнения

такой команды может быть выполнена

команда из любой ячейки памяти,

определяемой адресной частью команды

перехода. Для упрощения рассмотрим

команды перехода без относительной

адресации. Кроме того, предполагается,

что память имеет побайтную адресацию.

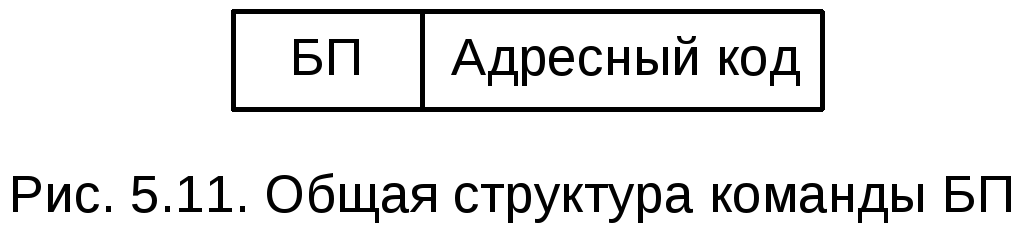

5.4.1. Команды безусловного перехода (бп)

Общая структура команды безусловного перехода изображена на рис. 5.11. При исполнении этой команды переход осуществляется всегда независимо от каких-либо условий.

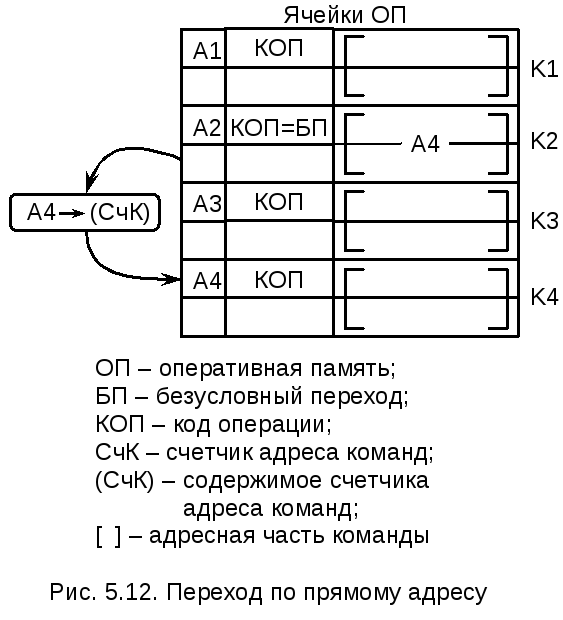

Рассмотрим два возможных варианта реализации команд БП – переход по прямому и косвенному адресам.

Переход по прямому адресу

В данном примере и далее рассматриваются команды длиной 2 байта (L = 2). При выполнении команды К2 в счетчик команд загружается адрес А4, т.е. (СчК) = А4. После этого процессор начинает выполнять команды с адреса А4. Таким образом, последовательность выполнения команд следующая: K1 K2K4 и далее по порядку.

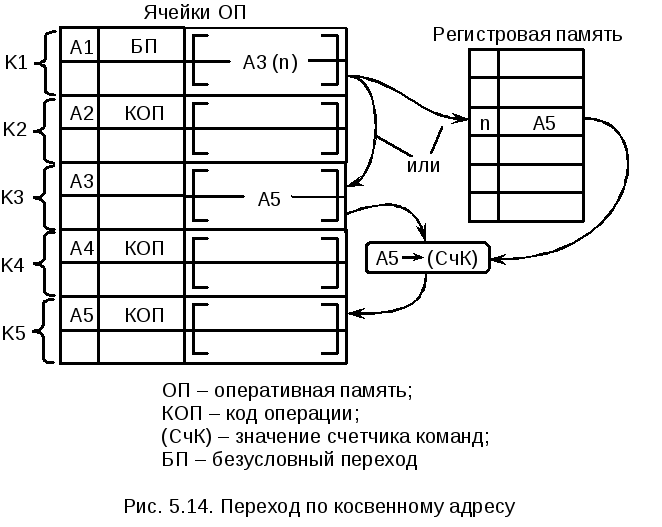

Переход по косвенному адресу

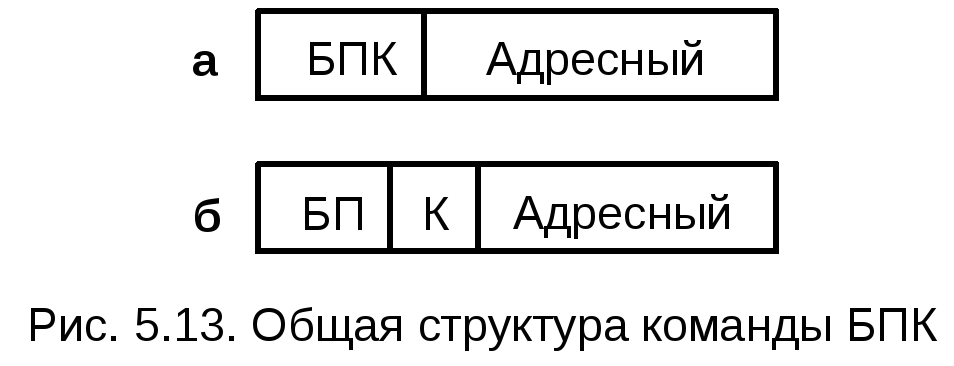

Общая структура команды изображена на рис. 5.13. На косвенную адресацию указывает код операции команды БПК (рис. 5.13, а) или специальное поле К в структуре команды (рис. 5.13, б), определяющее тип адресации.

Управление передается команде с исполнительным адресом, хранящимся в ячейке (регистре) памяти, на адрес которой (которого) указывает адресное поле команды БПК (рис. 5.14). Преимущества косвенной регистровой адресации были описаны ранее. Следует иметь в виду, что К3 в ОП не является собственно командой по адресу А3 (рис. 5.14). По адресу А3 может не быть никакого КОП, поскольку здесь хранится только исполнительный адрес (АИ).

Как уже отмечалось, в современных ЭВМ широко используется относительная адресация при выполнении команд переходов всех типов, т.е. АИ формируется с учетом содержимого базового регистра.