- •Оглавление.

- •Введение

- •Специальный раздел. Устройство и принцип работы изделия.

- •1.1 Основы теории работы индуктосина.

- •1.2 Обоснование метода преобразования.

- •1.3 Работа 2-х координатного планшета по структурной схеме.

- •1.4 Обоснование выбора элементной базы.

- •1.5 Работа 2-х координатного планшета по принципиальной схеме.

- •1.6 Реализация сдвига фазы.

- •Сдвиг фаз сигналов для модуляторов на 4-х фазной обмотке.

- •Сдвиг фаз сигналов для модуляторов на 3-х фазной обмотке.

- •Рис1.6 Схема реализации сдвига фаз сигналов

- •1.7 Работа схемы защиты от «дребезга».

- •1.8 Самосинфазируемый фильтр.

- •1.9 Формирование кода грубого отсчета.

- •1.10 Исследование возможности использования ппзу для согласования точного и грубого отсчетов и коррекции кода грубого отсчета.

- •Xо - измеряемая величина;

- •1.11 Алгоритм согласования и коррекции кода грубого отсчета.

- •1.12 Варианты реализации согласования отчетов на комбинационной логике.

- •1.13 Алгоритм формирования пзу, реализующего схему согласования и коррекции отсчетов в двухотсчетном преобразователе.

- •1.14 Расчет платы на вибропрочность.

- •1.15 Расчет надежности прибора.

- •1.16Микроконтроллеры семейства pic16c84.

- •1.16.1 Свойства. Высокопроизводительное risc - подобное цпу:

- •Периферия и Ввод/Вывод.

- •Структурная схема сmos технология

- •1.16.2 Общее описание

- •Защелка для бита данных

- •1.16.3 Типы генераторов.

- •Кварцевый генератор.

- •Выбор конденсаторов для керамического резонатора.

- •Выбор конденсатора для кварцевого генератора

- •Rc генератор.

- •1.16.4 Условия сброса

- •Выход из режима sleep.

- •Максимальные значения электрических параметров

- •1.17 Последовательный интерфейс rs-232

- •Однопроводной передатчик.

- •1.18 Конструкция платы.

1.6 Реализация сдвига фазы.

В данном случае на ФЧВ подаются сигналы :

![]() ;

;

![]() ;

;

![]() ;

;

![]() .

.

со

сдвигом фазы на 45![]() ,

90

,

90![]() ,

135

,

135![]() - для 4-х фазного индуктосина,

- для 4-х фазного индуктосина,

![]() ;

;

![]() ;

;

![]() .

.

со

сдвигом фазы на 60![]() и

120

и

120![]() - для 3-х фазного индуктосина соответственно,

и сигналы вида:

- для 3-х фазного индуктосина соответственно,

и сигналы вида:

![]() ,

где

,

где

![]() =2

=2![]() кГц.

кГц.

i = 1..4- для 4-х

- фазной

обмотки,

n = 4,

= 1..4- для 4-х

- фазной

обмотки,

n = 4,

i = 1..3 - для 3-х - фазной обмотки, n =3 соответственно.

Далее

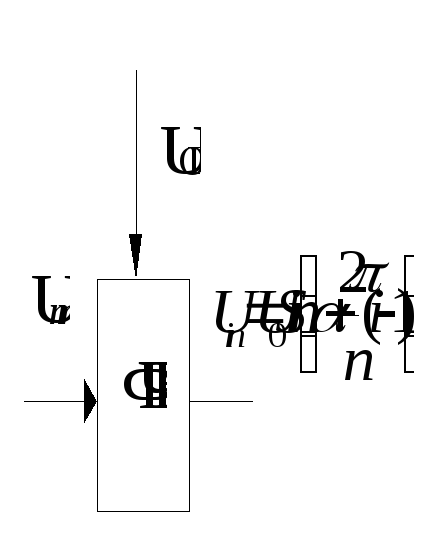

полученные сигналы вида

![]() ,

подаются на модулятор, на модулятор

также подается сигнал вида

,

подаются на модулятор, на модулятор

также подается сигнал вида

![]() .

.

Проблема

заключается в сдвиге

фазы

сигнала![]() ,

для каждого модулятора.

,

для каждого модулятора.

Эту проблему мы решаем схемотехнически.

Сдвиг фаз сигналов для модуляторов на 4-х фазной обмотке.

Сдвиг

на 90![]() осуществляется по средствам операции

сложения по модулю 2 1-го и 2-го разрядов

(1

осуществляется по средствам операции

сложения по модулю 2 1-го и 2-го разрядов

(1![]() 2).

2).

Сдвиг

на 45![]() осуществляется при помощиD

– триггера,

подавая на его вход Clk

3-ий разряд

и сигнал сдвинутый на 90

осуществляется при помощиD

– триггера,

подавая на его вход Clk

3-ий разряд

и сигнал сдвинутый на 90![]() входData.

входData.

Сдвиг

на 135![]() осуществляется при помощиD

– триггера,

подавая на вход Data

1-ый и на вход

Clk 3-ий разряды.

осуществляется при помощиD

– триггера,

подавая на вход Data

1-ый и на вход

Clk 3-ий разряды.

Сдвиг фаз сигналов для модуляторов на 3-х фазной обмотке.

Проведем

следующий расчет:

Проведем

следующий расчет:

На половине периода 1024 необходимо сдешифрировать точки А и В, то есть :

А=![]() =341,3...3,

=341,3...3,

В=![]() =682,7...

=682,7...

Раскладываем в двоичный код.

А=341,3 В=682,7

9р 512 0 1

8р 256 1 0

7р 128 0 1

6р 64 1 0

5р 32 0 1

4р 16 1 0

3р 8 0 1

2р 4 1 0

1р 2 0 1

0р 1 1 0

N![]() =

0101010101

=

0101010101

N![]() =

1010101010

=

1010101010

Проведем

дешифрацию N![]() и N

и N![]() совместно.

Делим код на

2 разряда и видим, что нам нужно в 2-х

разрядах опознать 01 или 10.

совместно.

Делим код на

2 разряда и видим, что нам нужно в 2-х

разрядах опознать 01 или 10.

1 1р

– 2048 квантов

1р

– 2048 квантов

10р - 1024 квантов

9р - 512 квантов

Соответственно схема будет выглядеть :

Рис1.6 Схема реализации сдвига фаз сигналов

для модуляторов на 3-х фазной обмотке.

1.7 Работа схемы защиты от «дребезга».

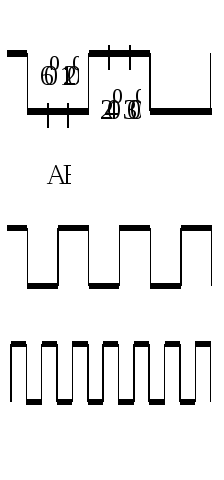

Так как с выхода нульоргана возможно появление сигнала следующего вида:

Н![]() еобходимо

выровнять передний и задний фронт

выходного меандра (защититься от

дребезга), так как «дребезг» на выходе

нульоргана не превышает 1-2-х тактовых

импульсов (ТИ) можно использовать

следующую схему защиты. Которая показана

на рис.

еобходимо

выровнять передний и задний фронт

выходного меандра (защититься от

дребезга), так как «дребезг» на выходе

нульоргана не превышает 1-2-х тактовых

импульсов (ТИ) можно использовать

следующую схему защиты. Которая показана

на рис.

Рис.1.7 Схема защиты от «дребезга».

Так как сигнал НО1 является тактовым сигналом записи кода ТО в регистр ТО, то в случае «дребезга» возможна некорректная работа регистра ТО. В схеме защиты от «дребезга» нам необходимо выделить фронт, по которому будет происходить запись в регистр ТО.

Сигнал с НО1 приходит на сдвиговый регистр, на информационные выходы и на вход RES (активный уровень «0»), когда на информационный вход приходит логическая «1» сдвиговый регистр начинает свою работу. В случае возникновения логического «0» на информационных входах, возникает активный уровень на входе RES и регистр приходит в исходное состояние (все информационные входы «0»). Если логическая «1» держится на информационных входах свыше 8-ми тактовых импульсов, то на выходе схемы защиты возникает импульс длительностью полтакта.

Временные диаграммы работы схемы защиты представлены на рис.