aaaГОСЫ / Лекции Кузнецов часть 2

.pdf34

10 Микроконтроллеры с архитектурой AVR

3 типа: Tiny – не имеют внутренней памяти. Выпускаются в 8-контактных корпусах. Применяются в

игрушках.

Classic – основной тип. Имеет память программ 1-4 кб, ОЗУ до 512 б, EEPROM электрически программируемая память. Содержит сторожевые таймеры.

Мega – имеют самую насыщенную архитектуру

Особенности семейства:

1 RISC – архитектура;

2 121 команда в системе команд 80 % выполняются за 1 машинный цикл; 3 Емкость памяти программ FLASH 128 кб

4 Встроенная память EEPROM 4 кб может перезаписывать 100 000 циклов 5 FLASH-память перезаписывается 1000 циклов

6 Регистровый файл 32-х 8-и разрядных регистров. Выполняет роль аккумулятора (получается 32 аккумулятора)

7 Диапазон измерения напряжений от 4 до 6 В

8 Диапазон тактовых частот от 0 до 6 МГц

9 Производительность 6 MIPS (6 млн операций в секунду при частоте 6 МГц)

10Встроена система реального времени

11Встроенный аналоговый компаратор

128-канальный 8-разрядный АЦП

13Возможность программной установки тактовой частоты

14Блокировка программного обеспечения

Недостаток – 64-контактный корпус планарного типа, что не позволяет его ремонтировать.

3 режима энергоснабжения:

1 Idle – останавливается центральный процессор, продолжает работать ОЗУ, таймеры, счетчики, SPI и КП.

2 Power Down – сохраняет содержимое регистров, останавливается тактовый генератор, делится до сигнала прерывания или системного сброса.

3 Power Slave – режим сна. Работает генератор реального времени.

35

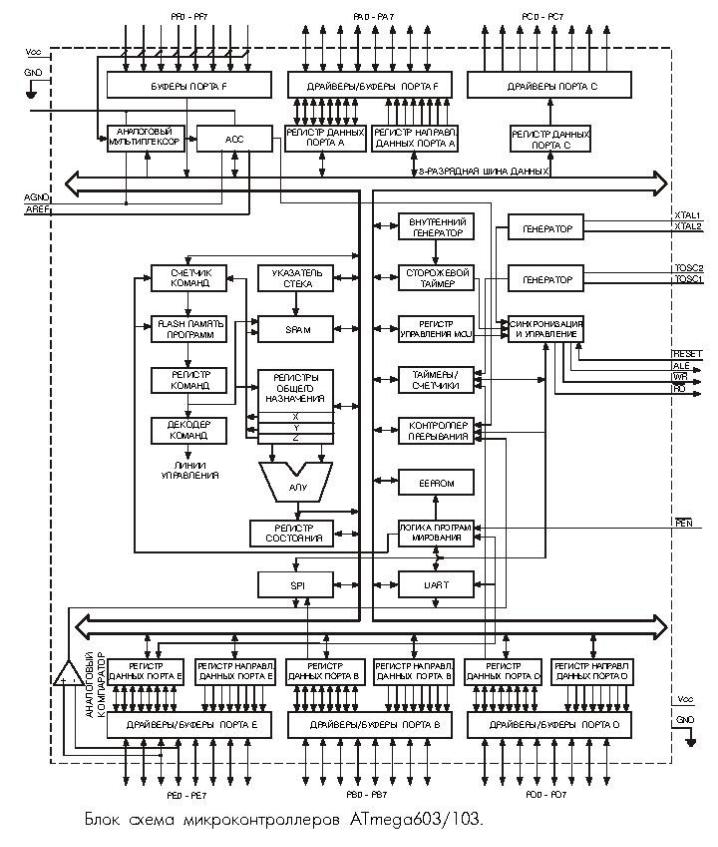

Структурная схема:

Компаратор подключается к III и IV входам порта Е и выход компаратора идет на КП Аналоговый компаратор - Выход используется для управления входом захвата таймера/счетчика. Кроме того, компаратор может формировать свой запрос прерывания. Пользователь может задать формирование запроса на прерывание по нарастающему или падающему фронту или по переключению

36

Порт А – 8-разрядный двунаправленный порт I/O. Функция обеспечения взаимодействия с внешней дополнительной SRAM данных - могут быть сконфигурированы как младшие разряды шины адреса/данных внешней SRAM данных.

Порт В – 8-разрядный двунаправленный порт I/O. Функции сравнения выхода и входа Т/С и организация последовательного интерфейса SPI

Порт С – 8-разрядный порт выхода. Обеспечение взаимодействия с внешней дополнительной SRAM. При использовании внешней SRAM через выводы порта C выводится старший байт адреса внешней памяти SRAM

Порт D – 8-разрядный двунаправленный порт I/O. Функция входа внешнего прерывания Т/С и вход тактового сигнала Т/С1 и 2 (и вход триггера захвата Т/С1)

Порт Е – 8-разрядный двунаправленный порт I/O. вход программ данных для UART, входы аналогового компаратора и вход внешнего прерывания INT.

Порт F– 8-разрядный порт входа. Входы могут использоваться как аналоговые входы MUX. FLASH – внутрисистемная встроенная память программ. 128к

УС 16-разрядный. Указывает на область SRAM данных, в которой размещаются стеки подпрограмм и прерываний.

РОН – 32 регистра, адреса $0000 - $001F. Кроме РОН в состав память данных входит 64 регистра ввода-вывода ($0020-$005F), 4к SRAM – внутренняя память данных, типа ОЗУ ($0060 - $0FFF), 60к внешней памяти ($1000 - $FFFF). 3 регистра X, Y, Z, служащие для регистрово-косвенного СА (16 бит)

АЛУ соединено с 32 РОН. Выполняет арифметические, логические операции и операции с битами.

EEPROM – память данных

Регистр Состояния – SREG – 8 разрядов. I-разрешение глобального прерывания, T-бит сохранения копии, H-дополнительный перенос, S-знак, N-отриц.значение для арифм.и лог.функций, V-дополнение до 2-х, если операция идет в дополнительном коде, Z – 0, C-флаг переноса.

Внутренний генератор служит для работы сторожевого таймера СТ для исключения эффектного зависания МП техники.

Регистр управления MCU – разрешение обращения к внешней памяти SRAM данных, перевод ПА и ПС на работу альтернативных функций, разрешение режима SLEEP и режима ожидания SRAM.

Т/С – 2 8-разрядных и 1 16-разрядный. Т/С 0 в дополнение к обычному режиму может тактироваться асинхронно от внешнего генератора, его используют как часы реального времени. Т/С1 и Т/С2 используются как таймеры счетчики с встроенной временной базой или счетчики, переключаемые по состоянию на внешнем выводе

XTAL1 – вход инвертирующего усилителя тактового генератора, XTAL2 – выход

TOSC1 – вход инвертирующего усилителя генератора таймера-счетчика, TOSC2 – выход RESET – сброс (инверсный). Необходимо удерживать более 2 МЦ низкий уровень напряжения ALE – строб разрешения фиксации адреса, используемый для разрешения внешней памяти

(фиксация младшего байта адреса в защелках адреса в пределах первого цикла обращения, в течение второго цикла обращения при обращении к данным используются выводы AD0 – AD7)

WR – строб записи внешней SRAM, RD – строб чтения

PEN – (инв.) выход разрешения программирования в низковольтном режиме программирования SPI – последовательный синхронный интерфейс. Для передачи по 3-х проводной системе в

синхронном режиме, обеспечивает высокоскоростной синхронный обмен данными между МК и периферийными устройствами или между несколькими МК.

UART - Универсальный асинхронный приемо-передатчик. обеспечивает любую скорость передачи информации в бодах, Высокая скорость передачи при низкой частоте XTAL, 8-разрядный или 9-разрядный форматы данных, Фильтрация шума, Обнаружение ошибок формирования кадров

37

|

Организация памяти МК |

|

|

||

$FFFF |

$ FFFF |

60 к |

SRAM |

Внешняя |

|

|

|

||||

|

$ 1000 |

память |

|||

|

|

|

|||

|

|

|

|

||

|

$ 0FFF |

4 к |

SRAM |

Внутренняя |

|

|

|

||||

FLASH |

$ 0060 |

память |

|||

|

|

||||

64 к x 16 = |

|

|

|

||

$005F |

|

|

Порты |

||

128 кб |

64 регистра |

|

|||

|

|

ввода- |

|||

|

|

I/O |

|

||

|

$0020 |

|

вывода |

||

|

|

|

|||

|

$001F |

РОН |

|

Регистры |

|

|

|

(32 |

|

общего |

|

$ 0000 |

$0000 |

регистра) |

|

назначения |

|

Память программ |

Память данных |

|

|

||

РОН – регистры общего назначения

Х, Y, Z – регистры, служащие для регистрово-косвенного способа адресации.

Каждому регистру соответствует адрес памяти, отображающей их в первых 32 ячейках пользовательского пространства данных. Такая организация памяти обеспечивает гибкое обращение к регистрам.

Работа внешней SRAM разрешается установкой бита SRE в регистре MCUCR.

АЛУ

Высокопроизводительное AVR ALU соединено непосредственно со всеми 32 быстродействующими регистрами общего назначения. За один тактовый цикл ALU выполняет операцию между регистрами этого регистрового файла. Операции ALU подразделяются на три основные категории: арифметические, логические и операции над битами.

38

Параллельные порты ввода-вывода информации

PORT A - 8-разрядный двунаправленный I/O порт.

Реализуется 3-мя регистрами, расположенными в пространстве I/O памяти данных:

PORT A |

$1B Регистр данных Чтение и запись. |

DDR A |

$1A. Регистр направления данных. Для задания направления: записывая байт, |

PIN A |

можно конфигурировать направление передачи информации. Чтение и запись |

$19 Регистр адресов выводов входа. Читается информация о состоянии входного |

|

|

контакта. Только чтение. |

Дополнительная функция включается установкой бита SRE (разрешение внешней SRAM) в регистре управления MCU (MCUCR), при этом установки регистра направления данных игнорируются. Выходные буферы выводов порта A обеспечивают втекающий ток до 40 мА.

PORT B - 8-разрядный двунаправленный I/O порт

Реализуется 3-мя регистрами, расположенными в пространстве I/O памяти данных: PORT B $18 регистр данных. Чтение и запись

DDR B $17 регистр направления данных. Чтение и запись

PIN B $16 регистр адресов выводов входа. Только чтение

Выходные буферы выводов порта B обеспечивают втекающий ток до 40 мА. Есть возможность обеспечивать альтернативные функции (дополнительные):

PB 0 Вход выбора ведомого. Для организации последовательного интерфейса SPI PB 1 Тактовый сигнал последовательной шины SPI, обозначается SCK

PB 2 Установка ведущий / ведомый вход по последовательному интерфейсу SPI-шины MOSI PB 3 Установка ведущий / ведомый выход по последовательному интерфейсу SPI-шины MISO PB 4 Сравнение выхода и входа таймера счетчика нулевого

PB 5 Сравнение выхода и входа таймера счетчика 1-го половина А

PB 6 Сравнение выхода и входа таймера счетчика 1-го половина В PB 7 Сравнение выхода и входа таймера счетчика 2-го

Последовательный интерфейс имеет 2 канала UART и SPI, возможна передача в синхронном режиме информации для SPI и в асинхронном для UART.

PORT C – $15 – 8-разрядный выходной порт.

Дополнительная функция – обеспечение взаимодействия с внешней дополнительной SRAM. При использовании внешней SRAM через выводы порта C выводится старший байт адреса внешней памяти SRAM.

PORT D – 8-разрядным двунаправленным I/O портом и оснащен встроенными нагрузочными резисторами.

Реализуется 3-мя регистрами, расположенными в пространстве I/O памяти данных: PORT D $12 регистр данных. Чтение и запись

DDR D $11 регистр направления данных. Чтение и запись

PIN D $10 регистр адресов выводов входа. Только чтение

Выходные буферы выводов порта D обеспечивают втекающий ток до 40 мА.

Дополнительные функции

PD 0 Вход внешнего прерывания INT 0. Сигнал инверсный. PD 1 Вход внешнего прерывания INT 1

PD 2 Вход внешнего прерывания INT 2

PD 3 Вход внешнего прерывания INT 3

PD 4 Вход триггера захвата таймера счетчика 1 PD 6 Вход тактового сигнала таймера счетчика 1-го PD 7 Вход тактового сигнала таймера счетчика 2-го

39

PORT E – 8-разрядный двунаправленный I/O порт, оснащен встроенными нагрузочными резисторами.

Реализуется 3-мя регистрами, расположенными в пространстве I/O памяти данных: PORT E $03 регистр данных. Чтение и запись

DDR E $02 регистр направления данных. Чтение и запись

PIN E $01 регистр адресов выводов входа. Только чтение.

Выходные буферы выводов порта D обеспечивают втекающий ток до 40 мА

Дополнительные функции:

PE 0 Вход программируемых данных (прием) для канала UART RxD PE 1 Выход программируемых данных или передача для UART TxD PE 2 Положительный вход аналогового компаратора AC+

PE 3 Отрицательный вход аналогового компаратора ACPE 4 Вход внешнего прерывания INT 4

PE 5 Вход внешнего прерывания INT 5

PE 6 Вход внешнего прерывания INT 6

PE 7 Вход внешнего прерывания INT 7

PORT F – 8-разрядный порт . Регистр:

PIN F - $00 – выводы входа порта F. Все входы порта F соединены с аналоговым мультиплексором присоединенным к ADC. Выводы порта F, кроме выполнения функций входов мультиплексора, могут быть использованы и в качестве цифровых входов, что позволяет пользователю в одно и то же время использовать часть выводов порта F в качестве цифровых входов и оставшуюся часть в качестве аналоговых входов. Как такового порта нет.

40

11 Способы адресации и система команд AVR

1 Регистровый |

СА для одиночного 2 Регистровый СА для 2-х регистров – |

регистра |

источника и приемника |

ОР – код операции, d – адрес |

|

INC Rd – инкреметировать [Rd]+1→Rd |

ADD Rr, Rd – сложение [Rr]+[Rd] →Rd |

DEC Rd – декрементировать [Rd]-1→Rd |

MOV Rr, Rd – перемещение [Rd] →Rr |

3 |

4 Непосредственная адресация данных в |

|

пределах памяти |

Величина n определяет адрес регистра |

16– 19 – регистр источника или регистр |

|

источника или регистра назначения |

приемника |

|

SBI P, B – загрузить бит из регистра I/O |

→ |

|

1→I/O (P, B) |

|

SUBI Rd, K – вычесть непоср. [Rd]–[B2] Rd |

|

LDI Rd, K – загрузить [B2] →Rd |

|

CBI P, B |

0 → I/O (P, B) |

|

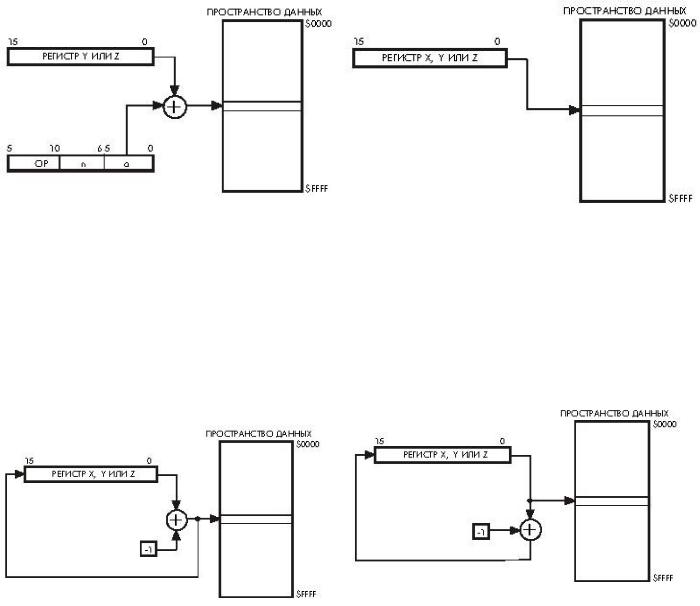

5 Косвенная адресация данных со смещением

LDD Rd, Y+q –загрузить косвенно со смещ. [M([Y]+q)] →Rd

7 Косвенная адресация данных с преддекрементом

Перед выполнением операции регистры X, Y, Z декрементируются (уменьшается на 1). Содержимое этих регистров определяет адрес.

41

6 Косвенная адресация данных

LD Rd, Y – загрузить косвенно [M([Y])] → Rd

8 Косвенная адресация с постинкрементом

Адресом операции является содержимое X, Y, Z, предшествующее инкрементированию (увеличению на 1).

LD Rd, -Y [Y]-1→Y [Y] →Rd |

LD Rd, Y+ [Y] →Rd [Y]+1→Y |

42

9 Адресация с использованием команд |

10 Непосредственная адресация памяти с |

LPM, ELPM |

использованием команд JMP, CALL |

Младший разряд Z0 дает возможность |

Младшие 16 бит задают адрес |

||

обращения |

к старшему |

и младшему |

|

адресным |

пространствам. |

Полный адрес |

|

указан в адресе ячейки Z0 |

|

|

|

Z0 = 0 |

– старший байт |

|

|

Z0 = 1 |

– младший байт |

|

|

Эта команда использует весь регистр. Адрес указывается в пределах $0000 - $7FFF.

ELPM – расширенная загрузка из памяти программ в регистр R0

[M([Z]+RAMPZ)] → R0

LPM – загрузка в R0 по содержимому рег.Z [Z] → R0

11 Косвенная адресация памяти программ с использованием LJMP и ICALL

Содержимое регистра Z загружается в программный счетчик

JMP K - переход [B2] →PC

CALL K – вызов подпрограммы [K] → PC

12 Относительная адресация памяти программ типа PJMP, RCALL

Выполнение программы продолжается с адреса PC + k + 1. Значение относительного адреса может быть от -2048 до 2047.

LIMP – перейти косвенно, используя рег. Z |

RJMP K – перейти относительно |

[Z] →PC |

[PC]+[B2]+1→PC |

ICALL – вызвать подпрограмму |

RCALL K – вызвать подпрограмму косвенно |

относительно регистра Z |

→ |

[Z] →PC |

[PC]+[B2]+1 PC |

|

43

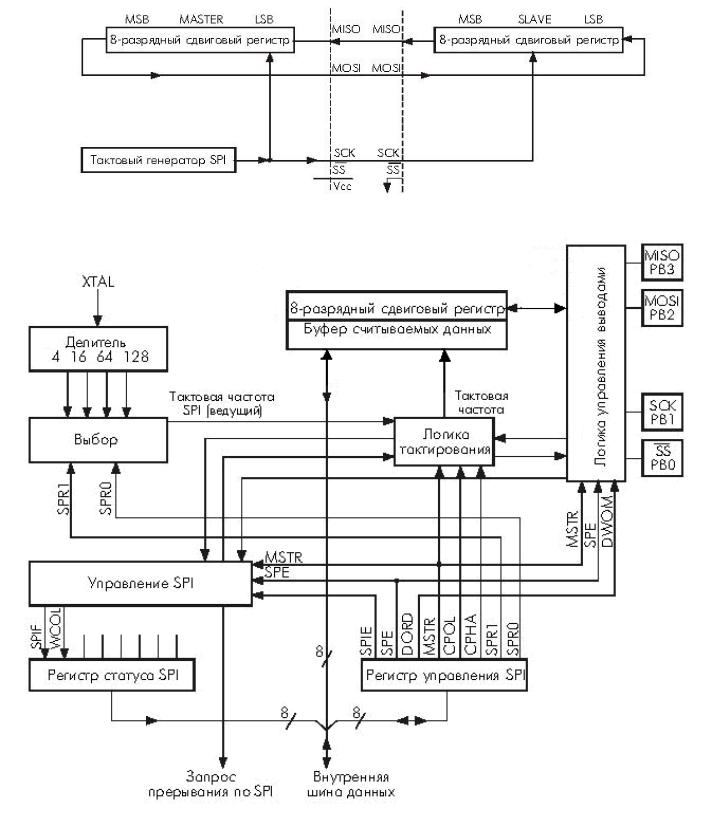

12 Последовательный ввод-вывод информации

SPI – последовательный синхронный интерфейс. Для передачи по 3-х проводной системе в синхронном режиме, обеспечивает высокоскоростной синхронный обмен данными между МК и

периферийными устройствами или между несколькими МК.

Особенности:

1) Полнодуплексный 3-проводный синхронный обмен данными (сначала младшими, затем старшими байтами). 2) Режим работы ведущий или ведомый. 3) Обмен данными с передаваемыми первыми старшим или младшим битами. 4) Четыре программируемые скорости обмена данными. 5) Флаг прерывания по окончании передачи. 6) Активация из Idle режима (только в режиме ведомого)

Структурная схема канала. MISO и MOSI – название соединения (обозначения контактов)

Структурная схема каждой из сторон этого канала