aaaГОСЫ / Схемотехника

.pdf

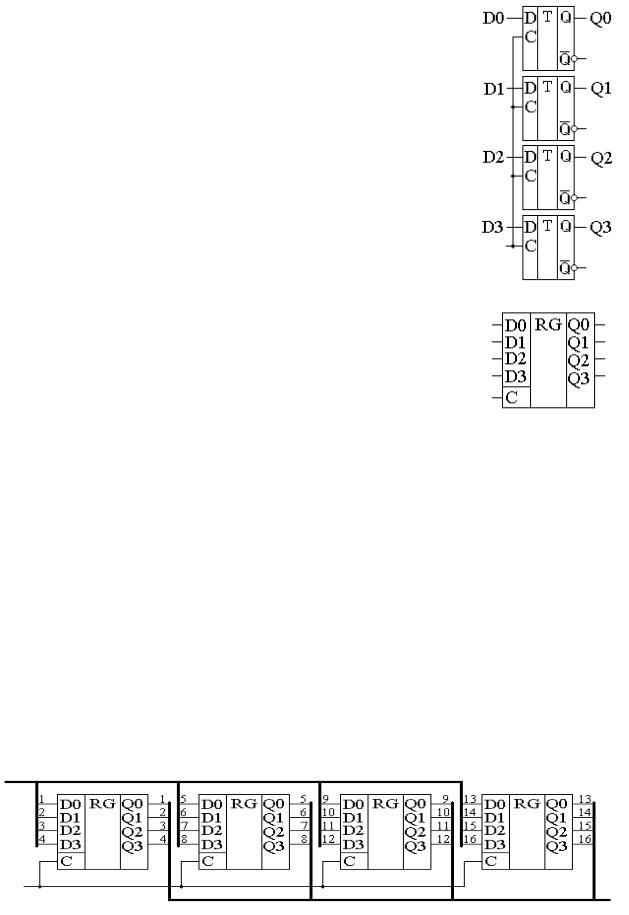

1) Параллельные регистры.

Регистр — последовательное или параллельное логическое устройство, используемое для хранения n- разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, обычно D, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

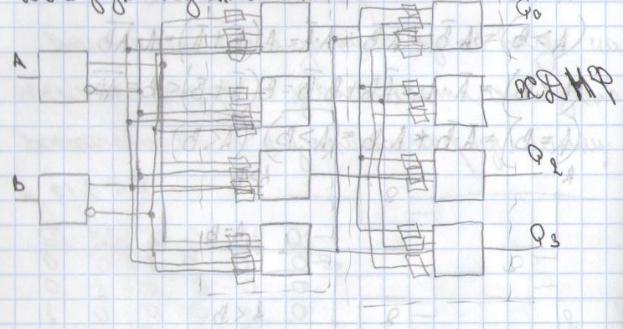

Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. В условнографическом обозначении возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом триггере регистра. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле условно-графического обозначения символами RG.

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто ставится инвертор.

Следует помнить, что назначение разрядов является условным. Если по каким либо причинам (например, с точки зрения разводки печатной платы) удобно изменить нумерацию разрядов, то это можно свободно сделать. При перенумерации входов регистров нужно не забывать, точно таким же образом, изменить номера выходов параллельного регистра.

Промышленностью выпускаются четырёхразрядные и восьмиразрядные микросхемы параллельных регистров. При решении практических задач часто требуется разрядность параллельных регистров большая восьми. В таком случае можно увеличивать разрядность регистров параллельным соединением готовых микросхем.

1

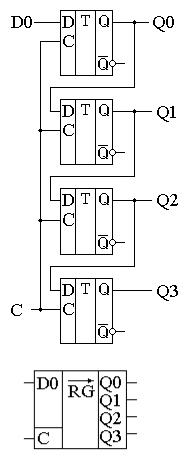

2) Регистры сдвига.

Последовательный регистр (регистр сдвига или сдвиговый регистр) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем). Для реализации последовательного (сдвигового) регистра подходят D триггеры, работающие по фронту!

Внутри сдвигового регистра триггеры соединены последовательно, то есть выход первого соединён с входом второго и т.д. Преобразование последовательного кода в параллельный в последовательном (сдвиговом) регистре производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход сдвигового регистра D0. Каждый бит сопровождается

отдельным тактовым импульсом синхронизации, который поступает на вход синхронизации последовательного регистра C.

После поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере последовательного (сдвигового) регистра и поступает на его выход, а так как он соединён с входом второго триггера, то и на его вход. После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера последовательного (сдвигового) регистра, запоминается в нем и поступает на его выход, а так как он соединён с входом третьего триггера, то и на его вход. Одновременно следующий бит входного последовательного кода запоминается в первом триггере последовательного (сдвигового) регистра.

После поступления четвертого тактового импульса в триггерах последовательного (сдвигового) регистра будут записаны логические уровни бит, которые последовательно присутствовали на его входе D0. Теперь этими битами можно воспользоваться, например, для отображения на индикаторах.

2

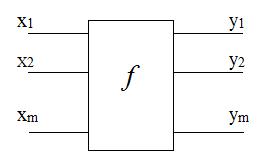

3) Комбинационные устройства.

Функциональные блоки, логическое состояние которых в данный момент времени полностью определяется логическим состоянием входов. (Комбинационными называются логические устройства, выходные функции которых определяются входными логическими функциями в момент их воздействия.) Характерной особенностью комбинационных устройств является отсутствие в схеме элементов памяти.

К комбинационным устройствам относятся шифраторы, дешифраторы, мультиплексоры и демультиплексоры, сумматоры и компараторы.

{Разрабатывать комбинационные устройства целесообразно в следующей последовательности:

1)составляется таблица истинности;

2)с помощью карты Карно находится минимизированное выражение логической функции;

3)составляется логическая схема.

В комбинационных схемах используются логические элементы: конъюнктор (И), дизъюнктор (ИЛИ), инвертор (НЕ), а также производные элементы: И-НЕ, ИЛИ-НЕ и «Равнозначность».}

yi = f(x1, x2… xm); Y=F(X)

3

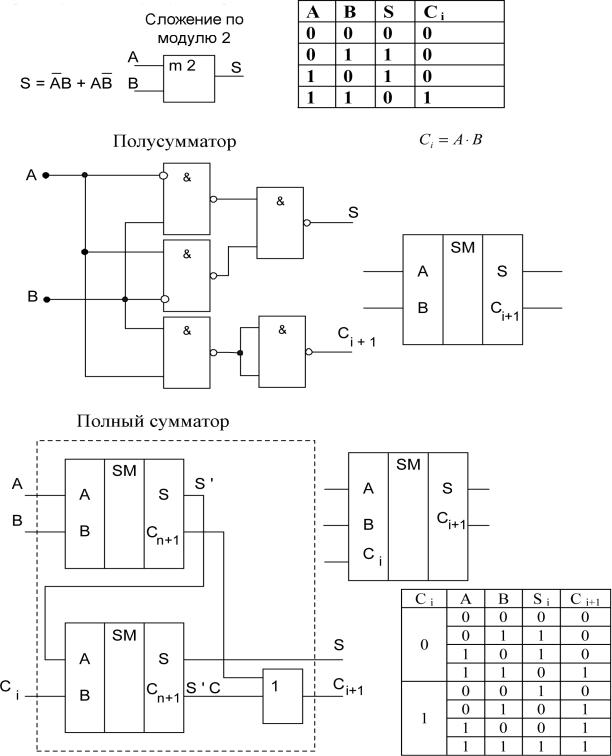

4) Двоичные сумматоры.

Сумматор - арифметическо-логическое устройство, выполняющее функцию арифметического сложения. Простейший сумматор (полусумматор) выполняет сложение по модулю 2. Полусумматор формирует сумму двух чисел (А и В) и единицу переноса, которая подается в более старший разряд С;. Следовательно, полный сумматор содержит вход для получения единицы переноса с младшего разряда, то есть происходит суммирование А и В с учетом Сi. Полный реализуется на двух сумматорах.

4

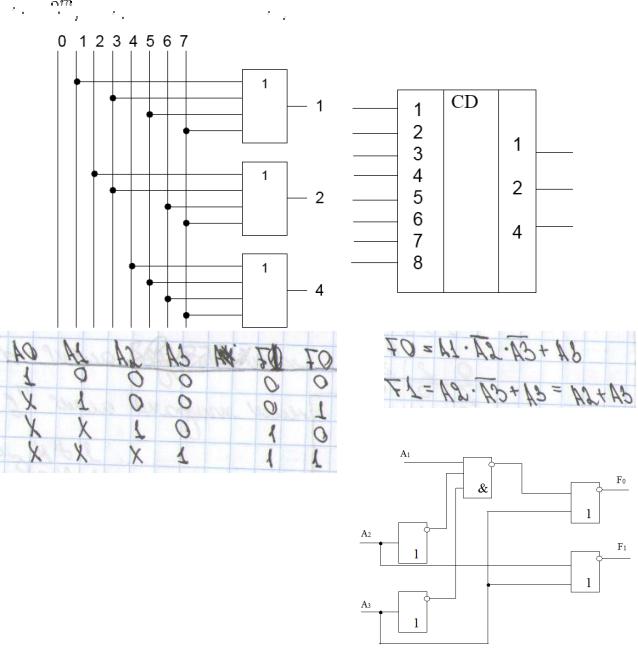

5) Шифратор.

Шифратор (кодер) — логическое устройство, выполняющее логическую операцию преобразования n-разрядного кода в m-разрядный двоичный, (троичный или k-ичный код).

Двоичный шифратор выполняет логическую функцию преобразования унитарного n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением:

где

где

— число входов,

— число входов,

— число выходных двоичных разрядов.

— число выходных двоичных разрядов.

5

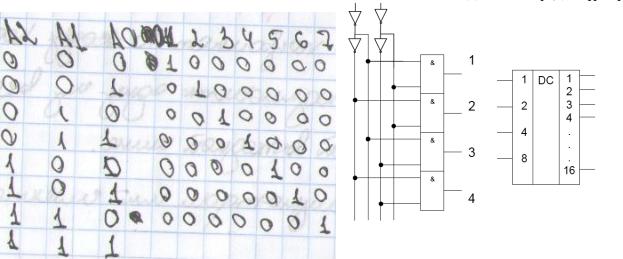

6) Дешифратор.

Дешифратор — это устройство, преобразующее цифровой сигнал, представленный в какой-либо одной из кодировок, в другую, незакодированную форму.

6

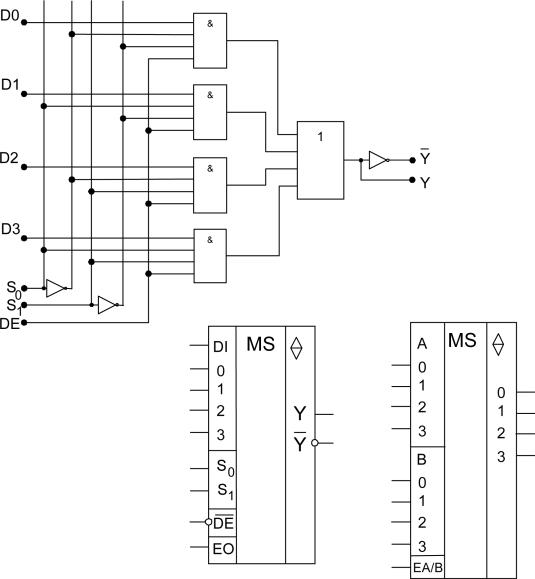

7) Мультиплексор.

Мультиплексоры выполняют коммутацию сигналов (электрических цепей). В этих устройствах осуществляется управление кодом. Мультиплексорами называются устройства, которые позволяют подключать несколько входов к одному выходу.

Каждый из входов DI (Data Input) подключается к выходу. Выбор входа осуществляется комбинацией SoS1. Современные мультиплексоры различают до 32х каналов и могут коммутировать не только одну цепь, но и слово (А и В).

Вход DE (Data Enable - разрешение данных) позволяет отключать входы (бывает нужно, когда требуется отключить мультиплексор от общей шины данных) Вход ЕА/В - позволяет выбирать нужное слово - А или В.

7

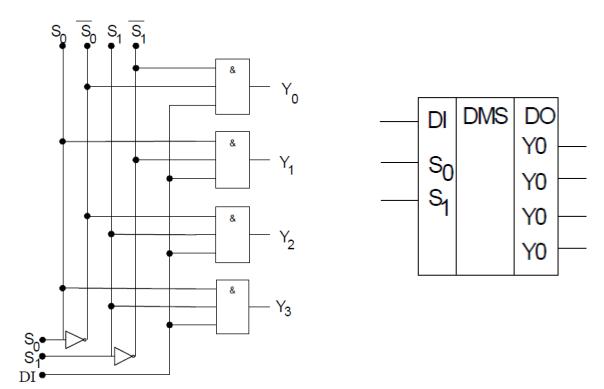

8) Демультиплексор.

Демультиплексорами называются устройства, которые позволяют подключать один вход к нескольким выходам. Демультиплексор можно построить на основе точно таких же схем логического "И", как и при построении мультиплексора. Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем.

8

9) Программируемые логические интегральные схемы.

Большой массив логических элементов, который полностью связан между собой и не выполняет никакой логической функции.

9

10) Электронные генераторы. Классификация, условия возбуждения.

Электронные генераторы служат получения напряжения (тока) заданной формы, частоты, скважности и амплитуды.

Классы:

1.Генераторые гармонических колебаний;

2.Импульсные генераторы.

Электронные генераторы выполняют на базе усилителя с положительной обратной связью

(П.О.С.)

Для самовозбуждения любого генератора необходимо выполнение двух условий:

1. баланс фаз фу+фæ =2π-n, n = 0,1,2...

фу -- поворот фазы сигнала усилителя; фæ – поворот фазы цепью обратнойсвязи.

2. баланс амплитуд |æ • К| > 1 Баланс фаз физически отражает П.О.С.

æ – коэффициент обратной связи, К – коэффициент усиления.

Баланс амплитуд показывает, что сигналы на входе и выходе усилителя соответствуют установившимся значениям.

10