aaaГОСЫ / Лекции Кузнецов часть 2

.pdf

|

|

|

44 |

|

|

Регистр управления SPI - SPCR. Разряды |

|||

|

|

|

|

|

D7 |

|

SPIE |

разрешение прерываний. Установка в 1 и приводит к установке SPIF бита SPSR, и |

|

|

|

|

при разрешении глобального прервывания, к выполнению прерывания SPI |

|

D6 |

SPE |

разрешение передачи SPI (самого канала). Установка в 1 разрешает подключение |

||

|

|

|

соответствующих контактов – разрешение альтернативной функции |

|

D5 |

DOR |

порядок данных (delta order) при установке в 1 передача идет младшими |

||

|

|

D |

разрядами вперед, если 0 – старшими разрядами вперед. |

|

D4 |

MSTR |

выбор режима MS (master-slave) при установке в 1 работает в ведущем режиме |

||

|

|

|

соответствующая сторона, в состоянии 0 – в ведомом режиме. |

|

D3 |

CPOL |

полярность тактового сигнала. При установленном этом разряде сигнал |

||

|

|

|

синхронизации при ожидании передачи в высоком уровне (с 1 на 0), при установке |

|

|

|

|

в 0 сигнал находится в низком уровне |

|

D2 |

CPHA |

фаза тактового сигнала (на временной диаграмме) |

||

SPSL |

SPR0 |

Выбор частоты тактового сигнала |

||

00 - деление входной частоты на 4

01 - на 16

10 - на 64

11 - на 128

|

Регистр статуса SPI - SPSR |

|

D7 |

SPIF |

- флаг прерывания. По завершению обмена последовательными данными установка |

|

|

в 1, если бит SPIE в регистре SPCR установлен в 1 и разрешено глобальное |

|

|

прерывание. Этот бит очищается аппаратно при выполнении программы |

|

|

обслуживания прерывания. |

D6 |

WCOL |

- флаг ошибки при записи. Устанавливается в состояние 1 если в процессе передачи |

|

|

данных выполнялась запись в регистр данных (SPDR). Чтение содержимого регистра |

|

|

данных, как и запись в него, выполненные во время пересылки данных, могут |

|

|

привести к неверному результату Очищается аппаратно при первом считывании |

|

|

регистра статуса SPI. |

Регистр данных SPI - SPDR

Адрес основного регистра $0F

Регистр данных SPI представляет собой регистр с возможностью чтения/записи и предназначен для пересылки данных между регистровым файлом и сдвиговым регистром SPI. Запись в регистр SPDR инициирует передачу данных, считывание регистра приводит к чтению сдвигового регистра приема

|

|

|

45 |

|

|

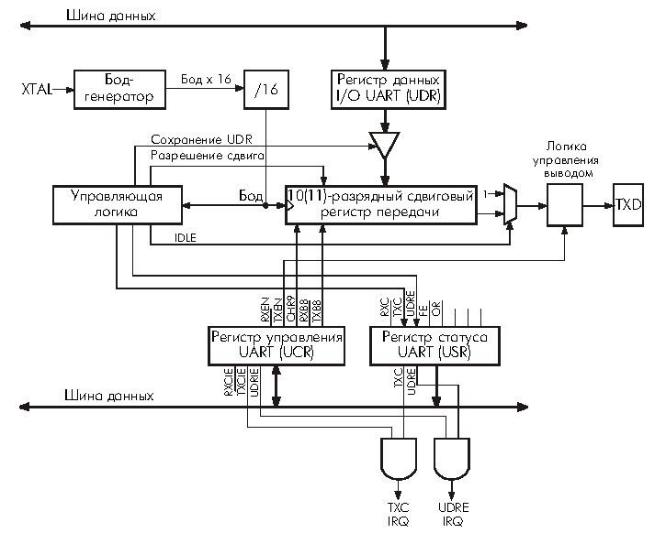

UART |

|

Универсальный асинхронный приемо-передатчик. |

|||

Особенности: 1) |

Обеспечивает любую |

скорость передачи информации в бодах |

|

2) Высокая скорость передачи при низкой частоте XTAL 3) 8-разрядный или 9-разрядный форматы |

|||

данных 4) Фильтрация |

шума |

(многократное |

сканирование каждого бита информации) |

5) Обнаружение переполнения 6) Обнаружение ошибок формирования кадров 7) Детектирование бита ложного старта 8) Три отдельных прерывания: по завершению передачи (TXC), по пустому регистру передаваемых данных (TXDRE) и по завершению приема (RXC).

9-й символ информации может быть как стоповый бит или контроль на четность.

Стартовый бит |

9 кадр |

байт |

Строповы |

|

й |

При обнаружении перехода из 1 в 0 начинается прием или передача. |

бит |

|

Через 10 (11) разрядный сдвиговой регистр может происходить передача.

Прием и передача могут происходить в полном или в половинном дуплексном режиме. Интервал делится на 16: 8, 9 и 10 интервалы синхронизации обеспечивают выборку в середине каждого интервала. 2 импульса имеют одно и то же значение, происходит определение 0 или 1

(если они равны) – происходит выделение разряда.

Имеет 3 прерывания: 1) По завершению передачи 2) По пустому регистру передаваемых данных 3) По завершению приема

Подключение идет через порт Е РЕ0 – приемник.

РЕ1 – включается трансмиттер delta-передатчик

Структурная схема передатчика

46

UCR и USR – 8-и разрядные регистры

Неподключенные связи в UСR относятся к приемнику, подключенные – к передаче

Структурная схема приемника

47

|

USR – регистр статуса |

|

D7 |

RxC |

Прием завершен. Установка в 1 при пересылке соответствующего байта из |

|

|

сдвигового регистра приема в UDR. Дает сигнал прерывания по завершению |

|

|

приема. |

D6 |

TxC |

Передача завершена. Данный бит устанавливается в состояние 1 когда весь |

|

|

символ (включая стоповый бит) выведен из сдвигового регистра передачи и в |

|

|

UDR не записаны новые данные |

D5 |

UDRE |

Регистр данных пуст. Данный бит устанавливается в 1, когда регистр данных |

|

|

пуст. РД готов к получению нового бита для передачи. |

D4 |

FE |

Ошибка кадра. Устанавливается в 1, при обнаружении условий ошибочного |

|

|

приема кадра, т.е. когда стоповый бит входящего символа в состоянии 0. |

D3 |

DOR |

Переполнение данных. Устанавливается в 1 при обнаружении условий |

|

|

переполнения, т.е. когда символ, уже находящийся в регистре UDR, не считан |

|

|

перед пересылкой нового символа из сдвигового регистра приема |

D2-D0 |

|

Зарезервированные биты. Обычно установлены в 0 |

Регистр управления UART – UCR

D7 RxCIE разрешение прерывания по завершению приема. При установленном в состояние 1 бите и установленном разрешении глобального прерывания

48

|

|

установка бита RXC в регистре USR приведет к выполнению прерывания по |

|

|

завершению приема. |

D6 |

TxCIE |

Разрешение прерывания по завершению передачи. При установленном в |

|

|

состояние 1 бите и установленном разрешении глобального прерывания |

|

|

установка бита TXC в регистре USR приведет к выполнению прерывания по |

|

|

завершению передачи. |

D5 |

UDRIE |

разрешение прерывания по пустому регистру данных. При установленном в |

|

|

состояние 1 бите и установленном разрешении глобального прерывания |

|

|

установка бита UDRE в регистре USR приведет к выполнению прерывания по |

|

|

пустому регистру данных UART. |

D4 |

RxEN |

Разрешение приемника. Установленный в состояние 1 бит разрешает приемник |

|

|

UART. Если приемник запрещен, то флаги статуса TXC, DOR и FE установить |

|

|

невозможно. Если эти флаги установлены, то очистка этого бита не приведет к |

|

|

очистке этих флагов |

D3 |

TxEN |

разрешение передатчика Установленный в состояние 1 бит разрешает |

|

|

передатчик UART. При запрещении передатчика во время передачи символа, |

|

|

передатчик не будет заблокирован прежде, чем будут полностью переданы |

|

|

символ в сдвиговом регистре плюс любой находящийся в UDR следующий |

|

|

символ |

D2 |

CHR9 |

режим 9-разрядных символов. Если 1 передаются или принимаются 9- |

|

|

разрядные слова плюс стартовый и стоповый биты. Девятые биты читаются и |

|

|

записываются с использованием битов RXB8 и TXB8 регистра UCR. Девятый |

|

|

бит данных может использоваться как дополнительный стоповый бит или бит |

|

|

контроля четности. |

D1 |

Rx8 |

Прием 8-разрядных данных. При установленном в состояние 1 бите CHR9 этот |

|

|

бит является девятым битом данных принятого символа. |

D0 |

TxB8 |

Передача 8-разрядных данных. При установленном в состояние 1 бите CHR9 |

|

|

этот бит является девятым битом данных передаваемого символа |

Бод-генератор представляет собой делитель, генерирующий импульсы передачи с частотой, определяемой выражением

BAUD = ( fCK ) 16 UBRR + 1

fСК – частота в бодах

16– частота кварцевого генератора

UBRR – содержимое регистра (частота меняется от 0 до 255) Частота в бодах может принимать значения от 2 400 до 115 200 Гц.

49

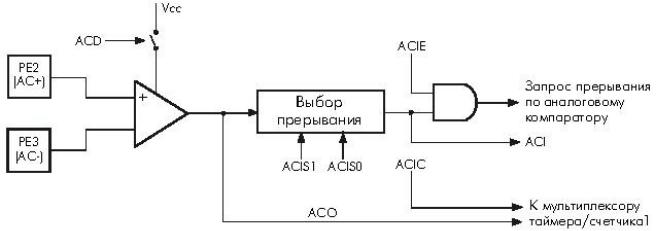

Аналоговый компаратор

Аналоговый компаратор сравнивает уровни на положительном выводе PE2 (AC+) и отрицательном выводе PE3 (AC-). При напряжении на положительном выводе PE2 (AC+) большем, чем напряжение на отрицательном выводе PE3 (AC-), выход аналогового компаратора ACO устанавливается в состояние 1. Выход компаратора может быть использован для управления входом захвата таймера/счетчика. Кроме того, компаратор может формировать свой запрос прерывания. Пользователь может задать формирование запроса на прерывание по нарастающему или падающему фронту или по переключению.

|

ACSR – регистр статуса и управления |

|

D7 |

ADC |

Запрет аналогового компаратора (при установке в 1). Отключение позволяет |

|

|

снизить потребление в активном и Idle режимах |

D6 |

- |

Зарезервированный |

D5 |

ACO |

Выход аналогового компаратора |

D4 |

ACI |

Флаг прерывания аналогового компаратора. Устанавливается в 1 в случае |

|

|

формирования компаратором прерывания, определяемого ACIS1 и ACIS0 |

D3 |

ACIE |

Разрешение прерывания по аналоговому компаратору. Снимается с регистра |

|

|

статуса МК |

D2 |

ACIC |

Разрешение входа захвата аналогового компаратора. Разрешает срабатывание |

|

|

функции захвата входа таймера/счетчика1 по переключению аналогового |

|

|

компаратора. В этом случае выход аналогового компаратора подсоединяется |

|

|

непосредственно ко входной цепи логики захвата входа, что обеспечивает |

|

|

использование функций подавления шума и выбора вида срабатывания |

D1 |

ASIS1 |

прерывания по захвату входа таймера/счетчика1 |

Определяет прерывание аналогового компаратора |

||

D0 |

ASIS0 |

|

D1 D0

00 Прерывание по переключению выхода компаратора

0 1 Зарезервировано

10 Прерывание по падающему фронту на входе компаратора

11 Прерывание по нарастающему фронту на входе компаратора

50

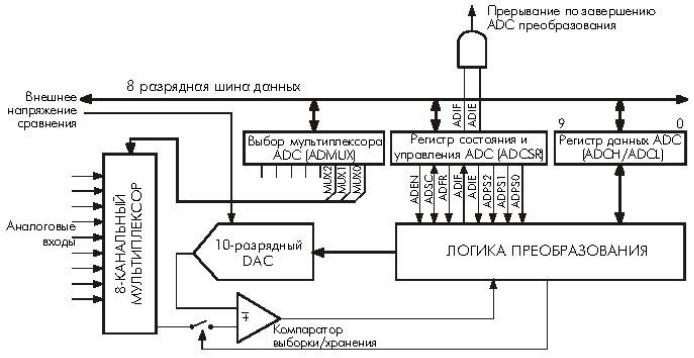

13 Аналогово-цифровой преобразователь

Для преобразования аналоговой величины, поступающей с мультиплексора, в цифровую. Особенности:1) Разрешение 10 разрядов 2) Время преобразования 70...280 мс ~ 50-200 кГц

3) 8 мультиплексируемых каналов входа 4) Режимы циклического и однократного преобразования 5) Прерывание по завершению преобразования 6) Устройство подавления шумов Sleep режима

ADC подсоединен к 8-канальному аналоговому мультиплексору, позволяющему использовать

любой вывод порта F в качестве входа ADC.

Структурная схема

Преобразование идет по методу последовательного счета ADMUX – выбор мультиплексора

ADCSR – выбор управления и статуса ADCH / ADCL – регистр данных

2 режима преобразования: метод однократного и циклического преобразования. В режиме однократного преобразования каждое преобразование инициируется пользователем. В режиме циклического преобразования ADC осуществляет выборку и обновление содержимого регистра данных ADC непрерывно. Выбор режима производится битом ADFR регистра ADCSR.

|

Регистр управления и состояния – ADCSR |

|

D7 |

ADEN |

Разрешение преобразования ADC (0 – запрещение преобразования) |

D6 |

ADSC |

Запуск преобразования. В режиме однократного преобразования – установка в |

|

|

1 для каждого цикла преобразования, в режиме циклического преобразования – |

|

|

достаточно установить 1 раз, при запуске первого цикла преобразования. |

D5 |

ADFR |

Установка циклического режима работы ADC |

D4 |

ADIF |

Флаг прерывания ADC. Устанавливается по завершению преобразования. |

D3 |

ADIE |

Разрешение прерывания. При установленных в состояние 1 бите ADIE и I-бите |

|

|

регистра SREG активируется прерывание по завершению преобразования. |

D2- |

|

Выбор коэффициента предварительного деления – получение тактовой |

D0 |

|

частоты. Описывается тремя разрядами |

ADP2 - ADP0 |

Получение тактовой частоты преобразователя |

|

|

|

000 – без деления, 001 – 2, 010 – 4, 011 – 8, 100 – 16, 101 – 32, 110 – 64, |

|

|

111 – 128 |

51

Таймеры – счетчики

Т/С 0 – 8-разрядный таймер-счетчик. Тактируется асинхронно от внешнего генератора Т/С 1 – 16-разрядный таймер-счетчик

Т/С 2 – 8-разрядный таймер-счетчик

Работают в режиме

∙Таймера

∙Счетчика событий

∙Широтно-импульсного модулятора

Широтно-импульсный модулятор реализуется в пределах 00Н ÷ FFН для Т/С 0 и Т/С 2

Т/С 0 может использоваться как счетчик реального времени, если на его вход повесить кварц с частотой fТ = 32,768 кГц.

Все счетчики имеют предварительные предделители, где делится частота кратно следующим числам:

Т/С 1 и Т/С 2 – системная частота делится на 8, 64, 256, 1024 (эта частота уже используется в контроллере)

Т/С 0 – системная частота делится на 8, 32, 64, 256, 1024, 2048

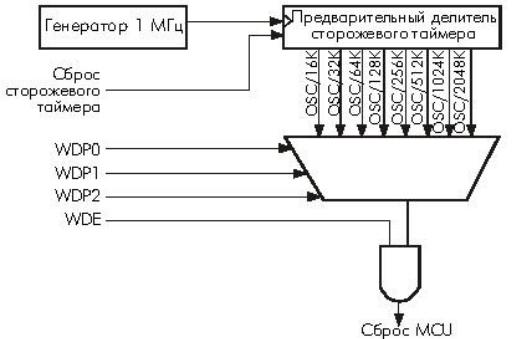

Сторожевой таймер

Сторожевой таймер тактируется отдельным встроенным генератором, работающим с частотой 1 МГц Установкой коэффициента предварительного деления можно изменять длительность интервала до сброса по сторожевому таймеру от 16 тыс. до 2048 тыс. циклов (от 16 до 2048 мс). Команда WDR сбрасывает сторожевой таймер.

С момента сброса сторожевого таймера можно установить восемь периодов длительности тактового сигнала, устанавливая, таким образом длительность периода сброса. Если период сброса завершается (в течение этого периода не поступил сигнал сброса сторожевого таймера), то МК сбрасывается и его работа продолжается по вектору сброса

Частота генератора fГ делится на 16, 32, 64, 2048

СТ предназначен для исключения эффекта зависания МП техники: время, за которое прогоняется программа, должно быть меньше, чем время появления сигнала сброса.

CLS – сигнал начального сброса СТ. Установка счетчика в 0

Необходимо настроить время с помощью выходов счетчика СТ. Максимальное время сброса 2,048 сек. Если программа зависла, сброс СТ выведет команду в 0-е состояние, если команда работает, она успевает пройти до системного сброса СТ.

52

|

|

|

|

|

Регистр управления WDTCR |

|

|||

|

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

|

x |

x |

x |

WDP0E |

WDE |

WDP2 |

WDP1 |

WDP0 |

D4 |

WDP0E |

|

разрешение отключения сторожевого таймера. Данные биты |

||||||

|

|

|

должны быть установлены в состояние 1 при очистке бита WDE. В |

||||||

|

|

|

ином случае сторожевой таймер не будет запрещен. Установленный |

||||||

|

|

|

бит аппаратно очищается после четырех тактовых циклов |

||||||

D3 |

WDE |

|

разрешение строржевого таймера. Если бит WDE установлен в |

||||||

|

|

|

состояние 1 (сторожевой таймер разрешен) и если бит WDE |

||||||

|

|

|

очищен, то функционирование сторожевого таймера запрещено |

||||||

D2 – D0 |

WDP2-WDP0 |

биты установки коэффициента предварительного деления |

|||||||

|

|

|

сторожевого таймера. Определяют коэффициент предварительного |

||||||

|

|

|

деления тактовой частоты разрешенного сторожевого таймера. |

||||||

WDP2 |

WDP1 |

WDP0 |

Длительность цикла сторожевого таймера |

||||||

0 |

0 |

0 |

|

-16 тыс. циклов |

|

|

|

||

0 |

0 |

1 |

|

- 32 |

|

|

|

|

|

.. |

.. |

.. |

|

|

|

|

|

|

|

1 |

1 |

1 |

|

- 2048 |

|

|

|

|

|

Это делается для запрещения сбоя по СТ

Сигнал появления сброса MCU должен быть больше, чем время выполнения программы.