Электроника и схемотехника (Ерёменко В.Т

.).pdf

с таблицами составить характеристические уравнения для каждой переменной кода 2421. Например, для переменной k3 имеем:

k3 e3e2e1e0 e3e2e1e0 e3e2e1e0 e3e2 e1e0 e3e2e1e0 .

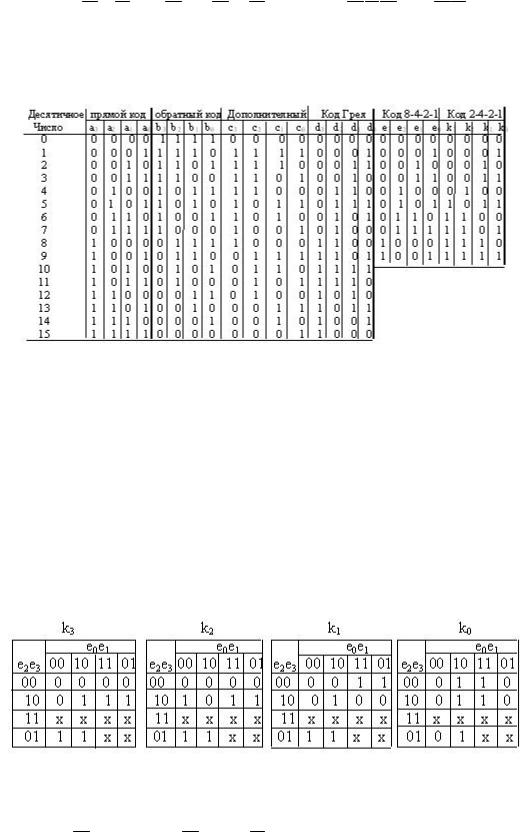

Таблица 12.6

Таблицы истинности некоторых кодов

Составив характеристические уравнения для всех переменных кода 2421, можно упростить их по правилам логических преобразований, затем построить структурную схему преобра-зователя.

Однако более эффективным является метод структурного проектирования с использованием карт Карно. Согласно этому методу составляем карты Карно для переменных k3, k2, k1, k0, причем клетки, не заполненные значениями аргументов е0 – е3, заполняем значениями 1 либо 0, делаем соответствующие объединения и записываем минимизированные выражения для переменных k

(рис. 12.10).

Рис. 12.10. Карты Карно для преобразователя кодов

В результате минимизации получим: k3 = e3 + e2e1 + e2e0;

k2 e3 e2e1 e2e0 ; k1 e3 e2е1 e2e1e0 ; k0 = e0.

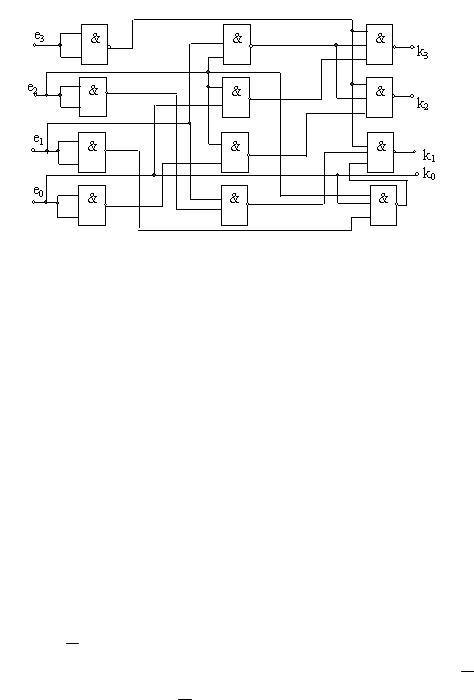

Полученные выражения полностью определяют структуру и состав элементов преобразователя. Однако технологически более

рациональны структуры, выполненные на однотипных логических элементах, например, на элементах И-НЕ. Структурная схема такого преобразователя представлена на рис. 12.11.

Рис. 12.11. Структурная схема преобразователя кода 8421 в код 2421

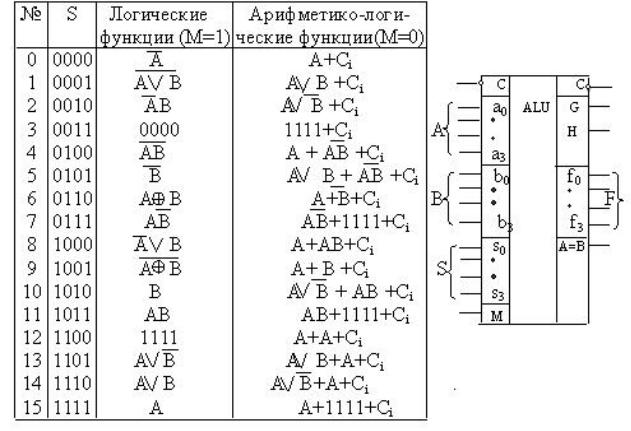

12.6. Арифметико-логическое устройство

Арифметико-логическое устройство (АЛУ) – это функциональный узел, предназначенный для реализации арифметических и логических операций по обработке цифровой информации. Типичное АЛУ (обычно четырёхразрядное) имеет входы операндов А и В, входы выбора операций S, вход переноса Сi и вход М (Mode), сигнал на котором задает тип выполняемых операций: логические (М = 1) или арифметико-логические (М = 0). Перечень выполняемых АЛУ операций приведен на рис. 12.12 [20].

Набор логических операций АЛУ позволяет воспроизводить все функции двух переменных. В арифметико-логических операциях сочетаются логические и арифметические операции одновременно. Вы-

ражение типа А В АВ следует понимать следующим образом:

вначале поразрядно выполняется операция инвертирования (В ), за-

тем логическое сложение ( А В ), умножение (АВ) и последующее арифметическое сложение.

Для выполнения операций над словами большой размерности АЛУ соединяются друг с другом путем последовательных или параллельных переносов. Организацию параллельных переносов осуществляют с помощью специальных схем-блоков ускоренного переноса, для чего в схеме АЛУ (рис. 12.12) предусмотрены два дополни-

тельных выхода (G, H), позволяющих организовать параллельный перенос.

Рис. 12.12. Таблица функций и условное изображение 4-разрядного АЛУ

13. ТРИГГЕРЫ И ЦИФРОВЫЕ АВТОМАТЫ

Триггер – устройство, имеющее два устойчивых состояния, у которого переход из одного состояния в другое происходит при воздействии управляющего сигнала вследствие регенеративного процесса.

Слово триггер означает спусковое устройство − «курок». Отличительной способностью симметричного триггера является свойство запоминания двоичной информации, т.е. триггер обладает памятью, под которой подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего (управляющего) сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер может хранить (помнить) один разряд числа, записанного в двоичном коде, (1 бит).

Регенеративным обычно называют процесс, сопровождающийся самовозбуждением, (самостимулированием). Такой процесс наблюдается в электрической цепи, охваченной положительной обратной связью с петлевым усилением К 1, он характеризуется резким изменением токов и напряжений в цепи.

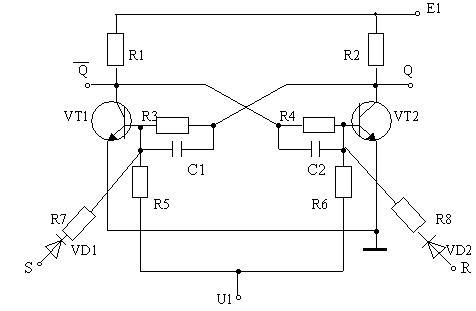

13.1. Триггерная схема на двух усилительных каскадах

Рассмотрим принцип действия триггера, для чего возьмем два простейших усилителя и соединим их так, чтобы они были охвачены ПОС (рис. 13.1).

Рис. 13.1. Триггерная схема на двух транзисторах

В схеме (рис. 13.1) возможны теоретически четыре состояния:

1)оба транзистора открыты;

2)оба транзистора закрыты;

3)открыт VТ1, VТ2 – закрыт;

4)VТ2 открыт, VТ1 – закрыт.

Особенность схемы в том, что первые два состояния являются неустойчивыми.

Предположим, что оба транзистора открыты и находятся в активном режиме. Ввиду симметрии схемы должны быть равны токи коллекторов и токи базы. Неизбежны малейшие флуктуации тока. Например, увеличится чуть-чуть ток коллектора VT1 – это повлечет за собой обязательное уменьшение напряжения на этом коллекторе,

а оно вызовет уменьшение базового тока транзистора VT2, что вызывает увеличение коллекторного напряжения транзистора VT2. В свою очередь это увеличение приведет к увеличению базового тока транзистора VТ1, которое вызовет увеличение степени открытия VT1, т.е. дальнейшее уменьшение коллекторного напряжения и увеличение коллекторного тока транзистора VT1. Процесс носит лавинообразный характер и будет продолжаться до тех пор, пока не прекратится действие положительной обратной связи. Это произойдет, когда транзистор VТ1 войдет в режим насыщения, а транзистор VТ2 – в режим отсечки. Триггерная схема (триггер) окажется в устойчивом состоянии.

Совершенно аналогично будут проходить процессы, если начнет изменяться ток транзистора VТ2. Параметры схемы могут быть подобраны так, что открытый транзистор насыщен, либо находится на границе активной области и не входит в режим насыщения. В первом случае триггер называется насыщенным, во втором – ненасыщенным.

В одном из устойчивых состояний триггер может находиться как угодно долго до момента, пока не поступит сигнал от внешнего источника управляющего напряжения. Управляющее напряжение можно вводить различными способами, например, через входные диоды

VD1, VD2.

Пусть транзистор VТ2 – закрыт, а VТ1 – открыт. Подадим открывающий импульс в цепь базы транзистора VТ2. Как только появится ток коллектора VТ2, транзистор VТ1 выйдет из насыщения, возникнет регенеративный процесс, приводящий к опрокидыванию триггера, т.е. транзистор VТ2 откроется, VТ1 закроется. Конденсаторы, показанные в схеме, не изменяя сути процесса, предназначены для ускорения этого процесса.

Чтобы перевести триггер в другое устойчивое состояние, нужно подать управляющий импульс теперь на базу другого транзистора (VТ1), который находится в состоянии отсечки. Процесс пройдет аналогично. Если бы вместо этого мы подали открывающий импульс вновь на транзистор уже открытый, это не изменило бы состояния триггера.

Если подать открывающие импульсы на оба транзистора, они оба могут открыться, но после снятия импульса возникнет неопределенность, так как любой из транзисторов окажется в запертом состоянии. Следовательно, такая комбинация управляющих импульсов должна быть запрещена.

У рассматриваемого триггера два информационных входа и два выхода. Они имеют специфические названия: один из выходов называют прямым и обозначают буквой Q (quit – покидать, оставлять), другой – инверсным и обозначают Q , т.е. сигнал противоположен первому. Состояние триггера чаще всего отождествляют с сигналом на прямом выходе. Считается, что триггер «установлен», если Q = 1, (Q = 0), т.е. находится в единичном состоянии.

Триггер «сброшен», «погашен», т.е. находится в нулевом состоянии, если Q = 0, (Q = 1). Когда управляющие входы (R и S) не активны (в данном случае R= 0, S = 0), триггер находится в режиме хранения. Различают три состояния триггера: установлен, сброшен, хранение. Вход, по которому триггер устанавливается в единичное состояние, обозначают входом S (set – установка). Вход, по которому триггер устанавливается в нулевое состояние, обозначают R (reset − возврат). В нашем случае, если мы обозначили Q и Q вход S будет на схеме слева, а вход R − справа.

13.2. RS-триггеры на логических элементах

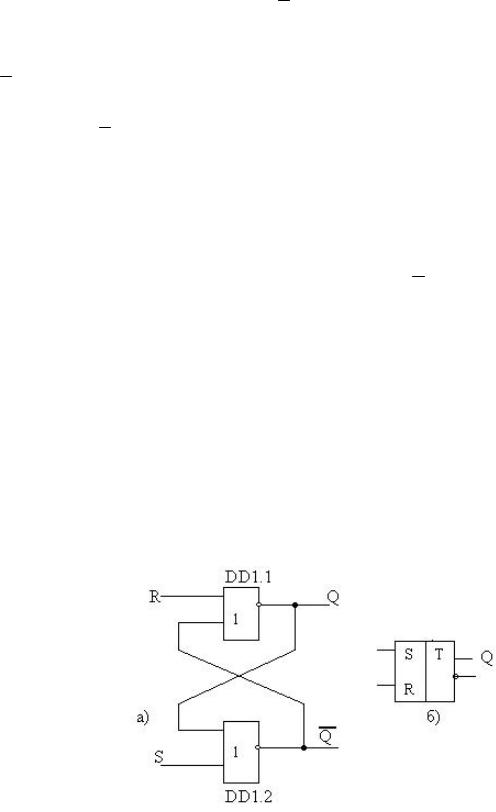

Триггерную схему, рассмотренную выше, называют RSтриггером. Проще всего триггер можно построить на логических элементах, соединяя их по кольцевой схеме так, что вход одного логического элемента является выходом второго, как показано на рис. 13.2.

Рис. 13.2. RS-триггер на элементах ИЛИ-НЕ:

а – структурная схема, б – условное графическое обозначение (УГО)

Предположим, что Q = 1, R = 0, S = 0, тогда на входах DD1.2 есть сигналы Q = 1, S = 0, на выходе будет Q = 0; на входах DD1.1 будут R = 0, Q = 0, на выходе Q = 1, т.е. такое состояние будет устойчивым и поддерживать само себя.

Подадим на вход сигнал R = 1, тогда на выходе микросхемы DD1.1 получим Q = 0, на входе DD1.2 будем иметь Q=0, S=0 − на выходе Q =1, этот сигнал поступит на вход DD1, будем на входе иметь R=1, Q =1, на выходе Q=0, т.е. подтверждаем новое состояние. Если теперь сделать R=0, положение не изменится: на выходе DD1.1 Q=0, на выходе DD1.2 Q =1, т.е. триггер принял состояние «сброшен». Рассуждая аналогично, придем к выводу, что при подаче на вход сигнала S=1 триггер установится в состояние «1». Последовательность изменения состояний на выходах триггера после подачи сигналов управления на его входы можно показать на диаграммах сигналов.

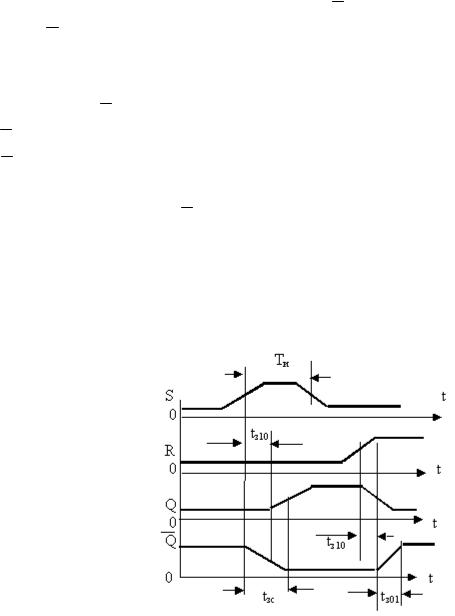

Рис. 13.3. Диаграммы сигналов RS-триггера

На рис. 13.3 обозначено:

tз10 – время задержки переключения логического элемента DD1.2 из «1» в «0» под действием сигнала S, либо переключения логического элемента DD1.1 под действием сигнала R;

tз01 – время задержки переключения логического элемента DD1.1 из «0» в «1» под действием сигнала R;

tзс – среднее время перехода сигнала на выходе триггера из одного состояния в другое.

Условно считается, что действие переключающего сигнала по изменению состояния других сигналов начинается с момента достиже-

ния этим сигналом половины своего уровня. Анализируя при этих условиях диаграммы сигналов, изображенные на рис. 13.3, можно сделать следующие выводы:

1. Для надежного переключения триггера входными сигналами минимальная длительность импульса Tи должна выбираться из условия:

Tи = 2 tзс.

2. Учитывая разброс средних значений времени задержки и появления сигналов на входах, для предотвращения сбоев, т.е. нарушения порядка переключения, следует обеспечивать паузу между фронтами и срезами управляющих сигналов. С этой целью для триггера должно быть определено «разрешающее» время – минимальный интервал времени между моментами посылок входных импульсов:

Tр = 3 tзс.

3. Максимальная частота переключения может быть определена как величина обратная разрешающему времени:

fмах = 1/ Tр = 1/ 3tзс, ( если tзс измерятьв мкс, то fмах – в МГц). Состояние триггера обычно отражают в таблицах состояния. Для

RS-триггера на логических элементах ИЛИ-НЕ эта таблица будет выглядеть так, как показано в табл. 13.1, где t, (t+1) – дискретные моменты времени до и после воздействия входных сигналов; Qn, Qn+1 – состояния до переключения и после него; Х – неопределенное состояние. В табл. 13.1 видно, что при наличии или подаче «0» на входы R и S на выходе будет сохраняться предыдущее значение Qn.

Таблица 13.1

Таблица состояний RS-триггера

t |

|

t+1 |

R |

S |

Qn+1 |

0 |

0 |

Qn |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

Х |

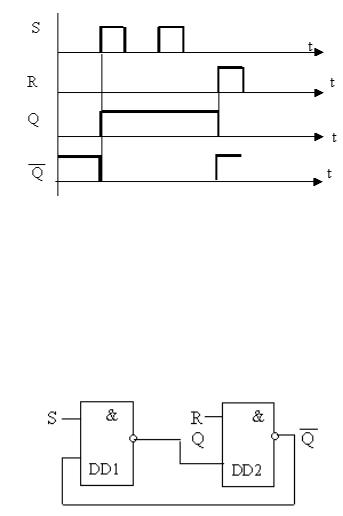

Часто можно встретить в литературе упрощенные временные диаграммы, в которых не показывают наклоны фронтов и спадов сигналов. Такие диаграммы можно использовать для определения общей картины, но для подробного анализа они мало пригодны (рис. 13.4).

Рис. 13.4. Упрощенные временные диаграммы сигналов RS-триггера

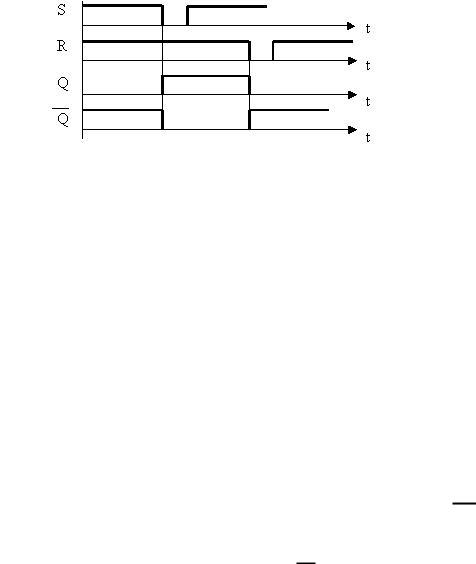

RS-триггер может быть построен не только на логических элементах ИЛИ-НЕ, но и на элементах И-НЕ (рис. 13.5), причём управление таким триггером осуществляется логическим сигналом низкого уровня.

Рис. 13.5. Структурная схема RS-триггера на логических элементах И-НЕ

Состояния триггера при различных сочетаниях входных сигналов показаны в табл. 13.2. Анализ структурной схемы и таблицы показывает, что «активным», т.е. изменяющим состояние триггера логическим уровнем в рассматриваемом триггере является уровень «0».

Таблица 13.2

Таблица состояний RS-триггера на логических элементах И-НЕ

|

t |

t+1 |

|

R |

|

S |

Qn+1 |

1 |

|

1 |

Qn |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

0 |

Х |

Упрощенные диаграммы сигналов будут выглядеть следующим образом (рис. 13.6):

Рис. 13.6. Диаграммы сигналов RS-триггера на элементах И-НЕ

Триггеры являются схемной реализацией элементарных цифровых автоматов, т.е. устройств, которые можно описать с помощью конечных множеств входных сигналов x (t) (входного алфавита), выходных сигналов (t) (выходного алфавита), функций переходов Fn, конечного множества внутренних состояний q(t) и функций выходов Fвых [19]. При этом используется понятие дискретного времени t, (t + 1), (t – 1) и т.д., т.е. моменты текущий, последующий и предыдущий (подробнее см. п. 13.7). Если текущее состояние Q (t) , то Q(t+1)

= Fn [Q (t ), x(t)], ( t ) = Fвых [Q(t), x(t)], где: x(t) – входной сигнал;

( t ) – выходной сигнал.

Например, анализируя таблицы состояний рассмотренных ранее триггеров, можно записать их функции переходов:

–RS-триггер на элементах ИЛИ-НЕ: Q(t+1) = S(t) + Q(t) R(t); RS= 0.

–RS-триггер на элементах И-НЕ: Q(t+1) = S(t) + Q(t) R(t); R+S = 1.

Функциональное назначение RS-триггера – реализация задержки

на такт или запоминание значения двоичной переменной. Рассмотренные RS-триггеры являются асинхронными, т.е. такими,

в которых переключения ЛЭ (логических элементов) происходят только как следствие изменения сигналов на входе. Физически после каждого переключения входного сигнала имеет место переходный процесс, состоящий в переключении связанных между собой ЛЭ, и этот процесс заканчивается переходом триггера в новое состояние, сохраняющееся до нового переключения. Поэтому можно условно принять временной интервал между двумя соседними переключениями на входе, равный условной единице (t = 1). Тогда к началу каждо-