Skhemotekhnika_Bassalin

.pdf

57

АП может быть автономным, т.е. не иметь информационных входов и функционировать в соответствии с реализованным в нем алгоритмом под воздействием тактовых сигналов.

Простейшими (элементарными) АП являются запоминающие элементы: конденсатор с ключевым транзистором, защелки и триггеры различных типов.

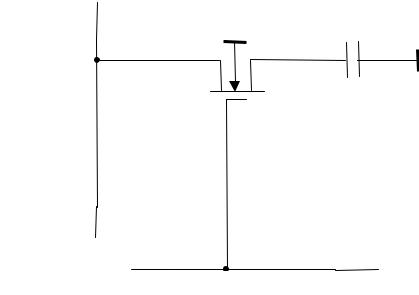

Схема конденсатора с ключевым МОП-транзистором представлена на рис. 2.26. Линия выборки, управляя затвором транзистора, обеспечивает отключение или подключение запоминающего конденсатора к линии записи-считывания.

Линия записисчитывания

Линия выборки

Рис. 2.26. Схема запоминающего элемента в виде конденсатора с ключевым МОП-транзистором

58

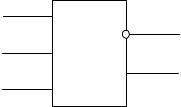

Простейшая асинхронная RS-защелка может быть построена на двух логических элементах ИЛИ-НЕ по схеме, представленной на рис. 2.27. S (Set) – вход установки защелки в единичное состояние (Q = 1). R (Reset) – вход сброса защелки в нулевое состояние (Q = 0). Таблица состояний RS-защелки и ее условное обозначение приведены на рисунках 2.28 и 2.29, соответственно.

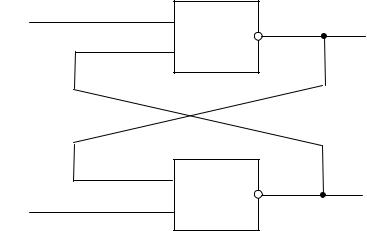

По аналогичной схеме может быть построена RS-защелка на основе логических элементов И-НЕ (рис. 2.30). Ее таблица состояний и условное обозначение представлены, соответственно, на рисунках 2.31 и 2.32.

S |

1 |

__ |

|

|

Q |

1

Q

R

Рис. 2.27. RS-защелка на логических элементах ИЛИ-НЕ

59

Sk |

|

|

|

|

_ |

|

|

Rk |

|

Qk+1 |

|

Qk+1 |

Примечание |

||

|

|

|

|

|

|

|

Запрещенная |

1 |

|

1 |

|

0 |

|

0 |

комбинация |

1 |

|

0 |

|

1 |

|

0 |

|

|

|

|

Установка в «1» |

||||

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

|

1 |

Сброс в «0» |

|

|

|

|

|

|

_ |

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

Qk |

|

Qk |

Хранение |

Рис. 2.28. Таблица состояний RS-защелки на логических элементах ИЛИ-НЕ

60

S

R

Рис.2.29. Условное обозначение RS-защелки на логических элементах ИЛИ-НЕ

61

_ |

& |

S |

Q

|

& |

_ |

_ |

|

|

|

Q |

|

R |

|

|

Рис. 2.30. RS-защелка на логических элементах И-НЕ

Синхронная RS-защелка помимо информационных входов R и S имеет вход C (Clock) для сигнала синхронизации. Его назначение: обеспечить одновременное (синхронное) изменение состояний многих защелок или выделить из информационного потока нужную часть сигнала.

Один из возможных вариантов функциональной схемы синхронной RS-защелки приведен на рис. 2.33. При C = 0 защелка находится в состоянии хранения информации, не реагируя на информационные сигналы. При C = 1 схема функционирует как асинхронная RS-защелка. Условное обозначение синхронной RSзащелки представлено на рис. 2.34.

62

_ |

_ |

|

_ |

|

Sk |

Rk |

Qk+1 |

Qk+1 |

Примечание |

|

|

|

|

Запрещенная |

0 |

0 |

1 |

1 |

комбинация |

|

|

|

|

|

0 |

1 |

1 |

0 |

Установка в «1» |

|

|

|

|

|

1 |

0 |

0 |

1 |

Сброс в «0» |

|

|

|

|

|

|

|

|

_ |

|

1 |

1 |

Qk |

Qk |

Хранение |

Рис. 2.31. Таблица состояний RS-защелки на логических элементах И-НЕ

63

S

S

R

R

Рис.2.32. Условное обозначение RS-защелки на логических элементах И-НЕ

S |

& |

|

|

|

_ |

|

S |

Q |

С |

|

|

|

R |

Q |

R |

& |

|

|

|

|

|

Рис.2.33. Синхронная RS-защелка |

|

64

S

C

R

Рис.2.34. Условное обозначение синхронной RSзащелки

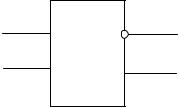

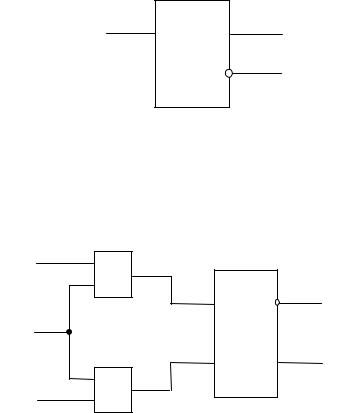

Синхронная D-защелка (схема на рис. 2.35) представляет собой память объемом 1 бит. Она обеспечивает возможность записи информации по одному входу D, когда разрешающий сигнал C принимает значение 1. Ее условное обозначение приведено на рис. 2.36.

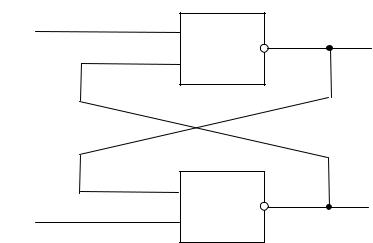

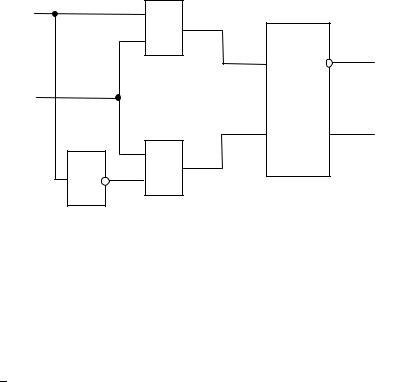

В отличие от синхронных защелок, управляемых уровнем разрешающего сигнала, триггер реагирует на информационные сигналы под воздействием перепада тактового сигнала (нарастающего или спадающего фронта импульса). Поэтому его можно назвать защелкой с динамическим управлением. Одна из возможных логических схем триггера изображена на рис. 2.37.

65

D |

& |

|

_ |

S |

Q |

С

R |

Q |

1 &

Рис.2.35. Синхронная D-защелка

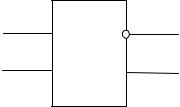

RS-триггер, представленный на рис. 2.37 управляется нарастающим фронтом тактового импульса. При C=0 RS-защелка на выходе триггера поддерживается в режиме хранения. При переходе C из «0» в «1» состояние защелки устанавливается в соответствии со значениями сигналов на информационных входах S, R , после чего информационные входы блокируются до перехода C в состояние «0». Условное обозначение триггера, управляемого нарастающим фронтом тактового импульса, приведено на рис. 2.38.

66

D

C

Рис.2.36. Условное обозначение синхронной D-защелки

На основе RS-триггера по схеме, приведенной на рис. 2.39, легко получается D-триггер, условное обозначение которого представлено на рис. 2.40.

Перечень триггерных устройств может быть дополнен так называемыми счетными триггерами (JK-триггер, T-триггер),

двухступенчатыми триггерами с различными способами управления ступенями и т.д. Информацию о них можно найти в литературе [2], [18], [22].

К наиболее распространенным типовым последовательностным узлам относятся регистры различного назначения, регистровые файлы, счетчики.

Регистр – многоразрядное (словарное) устройство, построенное из триггеров (или синхронных защелок) и дополнительных логических элементов, обеспечивающих выполнение возложенной на него функции при приеме, хранении и выдаче информации, сдвиге информации в разрядной сетке, выполнении поразрядных логических операций над словами.