Skhemotekhnika_Bassalin

.pdf

47

INVa |

|

|

|

a |

|

& |

=1 |

ENa |

|

|

|

|

|

|

|

b |

|

& |

|

ENb |

|

|

|

|

|

|

|

C0 |

|

DC |

0 |

1 |

2-4 |

||

C1 |

2 |

|

1 |

|

|

|

& |

ab |

|

|

& |

|

|

|

|

|

|

|

1 |

a b |

|

|

||

|

& |

|

|

|

|

1 F 1

1 F 1

&

&

SM |

s |

& |

|

p |

& |

|

|

Выход

переноса

Вход

переноса

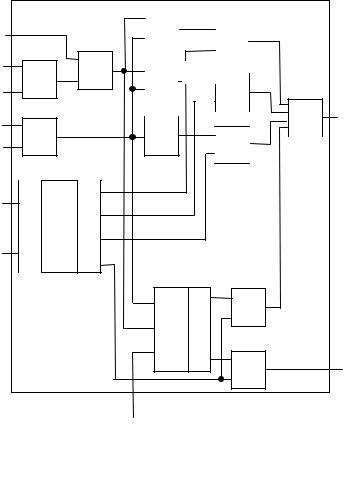

2.21. Одноразрядное АЛУ

48

INVа |

ENa |

ENb |

C0 |

C1 |

INC |

Функция (F) |

0 |

1 |

1 |

0 |

0 |

0 |

a b |

0 |

1 |

1 |

1 |

0 |

0 |

a b |

|

|

|

|

|

|

_ |

0 |

1 |

1 |

0 |

1 |

0 |

b |

0 |

1 |

1 |

1 |

1 |

0 |

a + b |

0 |

1 |

1 |

1 |

1 |

1 |

a+b+1 |

0 |

1 |

0 |

1 |

1 |

1 |

a + 1 |

1 |

1 |

0 |

1 |

1 |

1 |

- a |

1 |

1 |

1 |

1 |

1 |

1 |

b - a |

1 |

0 |

1 |

1 |

1 |

0 |

b - 1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

_ |

1 |

1 |

0 |

1 |

0 |

0 |

a |

|

|

|

|

|

|

|

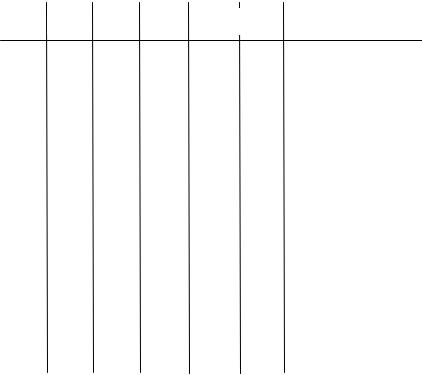

Рис. 2.22. Некоторые из комбинаций значений управляющих сигналов АЛУ

2.3. Введение в проблематику синтеза логических схем произвольной комбинационной логики

Цифровые устройства помимо типовых функциональных узлов могут иметь в своем составе комбинационные схемы

49

произвольной логики, выполняющие специфические для данного устройства функции. Синтез таких схем заключается в построении на базе определенных логических элементов и (или) типовых функциональных блоков логических структур, реализующих заданную систему функций. Логические элементы и типовые функциональные блоки, используемые для построения схемы, называются базисными (библиотечными) элементами. В совокупности они образуют базис (библиотеку) синтеза.

К функциональным блокам, которые могут выступать в качестве базисных элементов, следует отнести дешифраторы, мультиплексоры, ПЗУ (их организация будет рассмотрена в главе 4), программируемые логические матрицы.

О реализации произвольной комбинационной логики на базе дешифратора и универсальных настраиваемых логических блоках на основе мультиплексоров уже говорилось в подразделе

2.2.

Другим способом реализации произвольной комбинационной логики является логический блок табличного типа (LUT, Look-Up Table). Это память, хранящая в своих ячейках значения логической функции (или набора логических функций в случае многоразрядной ячейки). Доступ к конкретной ячейке осуществляется по адресу, в качестве которого выступает соответствующий набор аргументов воспроизводимой функции. Надо заметить, что с точки зрения выполняемой функции LUT является комбинационным блоком. Но с точки зрения реализации это цепь последовательностного типа.

Синтез комбинационных схем на вентильном уровне в заданном логическом базисе (SLC, Small Logic Cells) отличается широкой свободой поиска рациональных решений, обеспечивающих разумный компромисс между выдвигаемыми частными критериями. Таковыми, к примеру, могут быть

сложность схемы и ее быстродействие.

SLC-синтез складывается из двух основных этапов. На первом этапе решается задача оптимизации логических функций,

50

состоящая в нахождении такого их представления (двухуровневого или многоуровневого), которое бы обеспечивало необходимый компромисс между выдвинутыми критериями. При этом, критерий минимальности суммарного числа литералов в логических выражениях способствует упрощению схемы, но приводит к многоуровневой логике и, как следствие, снижению быстродействия синтезируемого устройства. С методами факторизации и декомпозиции, используемыми для получения многоуровневых представлений логических функций, а также конкретными эвристиками их реализации, можно ознакомиться по источникам [9],[19],[20]. Второй этап синтеза состоит в

реализации логических функций, т.е. построении из элементов логического базиса схемы, выполняющей исходно заданные функции. Конкретные алгоритмы, формализующие данный этап синтеза, представлены в работах [9], [21].

SLC-синтез сложных комбинационных цепей произвольной логики и реализация их как специализированных (заказных) БИС/СБИС связаны с большими материальными и временными затратами. При малой тиражируемости таких изделий данный подход оказывается экономически нецелесообразным. Как альтернатива ему рассматривается применение БИС/СБИС с программируемой и репрограммируемой структурой. Данное направление берет свое начало от программируемых логических матриц, программируемой матричной логики и базовых матричных кристаллов.

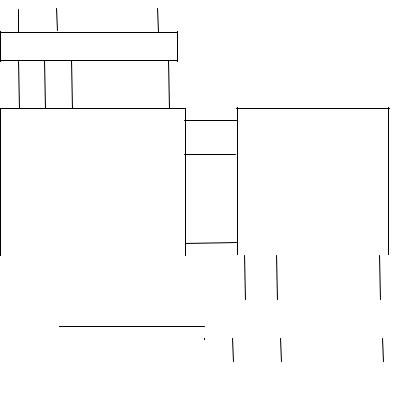

Программируемая логическая матрица (ПМЛ или PLA, Programmable Logic Array) комбинационной логики — это регулярная матричная структура, широко используемая для реализации сложной управляющей логики заказных БИС/СБИС. Схематически ее можно представить так, как показанона рис. 2.23.

Входной буфер ПЛМ принимает однофазные входные сигналы x1 , x2 , …… , xn , преобразует их в парафазные и

51

усиливает до мощности, необходимой для питания матрицы М1.

x1 |

x2 |

xn |

. . . . . . .

Входной буфер

. . . . . . .

t1

& |

1 |

t2

M1 |

tm |

|

M2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

. . . . . . . |

|

|

|

|

|

|

|

|||

OE |

|

|

Выходной буфер |

||||

OE |

|||||||

|

|

|

|||||

|

|

|

|

|

. . . . . . . |

|

|

|

|

F1 |

F2 |

FN |

|||

Рис. 2.23. Общая структура ПЛМ

Матрица М1 реализует m конъюнкций (термов) t1, t2, …. , tm от n входных переменных и (или) их отрицаний. Матрица М2 формирует N дизъюнкций от m термов. Выходной буфер

52

обеспечивает необходимую нагрузочную способность ПЛМ, возможность инвертирования реализуемых функций, а также управляемый с помощью сигнала ОЕ (Output Enable) выход на внешние шины.

Таким образом, ПЛМ реализует систему двухуровневых булевых функций, представленных в дизъюнктивной нормальной форме (ДНФ).

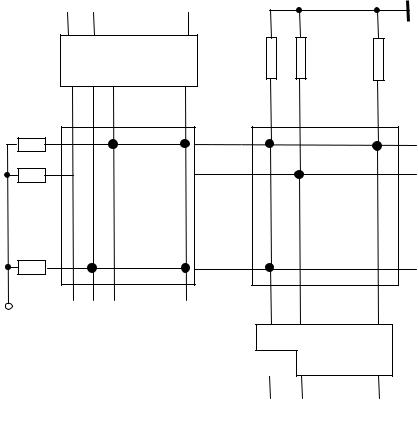

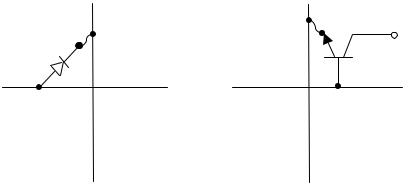

Схемотехника ПЛМ на определенном уровне детализации представлена на рис. 2.24. Вертикальные шины матрицы М1 — входные цепи конъюнкторов. Горизонтальные шины связывают выходы конъюнкторов матрицы М1 с входами дизъюнкторов матрицы М2. Вертикальные шины матрицы М2 соответствуют выходам дизъюнкторов. Соединения вертикальных и горизонтальных шин осуществляются через элементы связей, подключаемые к шинам через плавкие перемычки. В качестве элементов связей в матрице М1 используются диоды (рис. 2.25 а). Совместно с резисторами и источником питания они реализуют известные диодные схемы И. В работе этих схем задействуются только те диоды, плавкие перемычки которых не нарушены в результате программирования (сохранившиеся связи условно помечаются жирными точками, как это сделано в качестве примера на рис.2.24). Роль элементов связей в матрице М2 выполняют транзисторы (рис. 2.25 б), подключаемые по схеме эмиттерного повторителя относительно линий термов и реализующие на выходах матрицы М2 функцию ИЛИ.

В зависимости от физической организации программирования матриц различают ПЛМ, программируемые при изготовлении (заказные ПЛМ), и ПЛМ, программируемые пользователем. Программирование при изготовлении осуществляется металлизацией участков матрицы через специальную маску (шаблон). Программирование пользователем выполняется на специальном оборудовании (программаторе), например, выжиганием определенных перемычек.

53

x1 x2 |

xn |

. . . . . .

Входной буфер

. . . .

t1

t2

M1 |

М2 |

tm

. . . .

Ucc

Выходной буфер

OE

OE

OE

. . . .

F1 F2  FN

FN

Рис. 2.24. Схемотехника ПЛМ на определенном уровне детализации

54

Ucc

а) |

|

|

б) |

|

Рис. 2.25. Соединения вертикальных и горизонтальных |

||||

|

|

шин ПЛМ: |

|

|

а) для матрицы М1; |

б) для матрицы М2. |

|||

Применяя те или иные средства программирования, на |

||||

ПЛМ можно реализовать |

любую систему N |

логических |

||

функций, зависящих от |

n |

переменных и представленных в ДНФ |

||

на общем наборе из |

m |

термов. С целью |

выбора ПЛМ |

|

минимальной сложности обычно стараются сократить число термов m, используемых для представления системы функций. Т.е. решают задачу совместной минимизации системы функций, стремясь получить в результате кратчайшие (с минимальным числом термов) ДНФ реализуемых функций. Методы решения таких задач рассматриваются в работе [19]. Вопросы программирования ПЛМ, воспроизведения с их помощью

55

скобочных форм представления функций, наращивания размерности рассмотрены в источнике [2].

При воспроизведении систем логических функций, не имеющих значительных пересечений между собой по одинаковым термам, отпадает необходимость обеспечения возможности использования выходов любых конъюнкторов любыми диъюнкторами. Поэтому можно отказаться от программирования матрицы М2 (матрицы ИЛИ), жестко распределив термы по ее входам. При этом упрощается изготовление и использование схем, но теряется функциональная гибкость. Такие схемы называют схемами программируемой матричной логики (ПМЛ или PAL, Programmable Array Logic).

Очевидно, при использовании ПМЛ задача поиска представления функций с наибольшим числом общих термов теряет смысл.

К базовым структурам, положившим начало построению и развитию программируемых логических интегральных схем

(ПЛИС), наряду с ПЛМ и ПМЛ, следует также отнести базовые матричные кристаллы (БМК или MPGA, Mask Programmable Gate Arrays). БМК представляет собой матрицу регулярно расположенных на кристалле нескоммутированных (или частично скоммутированных ) компонентов (транзисторов, резисторов , логических элементов и др.). Путем формирования на кристалле межкомпонентных соединений на его основе может быть реализована любая функционально-логическая схема. При этом значительно сокращаются сроки разработки специализированных БИС/СБИС, что способствует быстрому внедрению новых архитектурных решений в современные вычислительные системы.

2.4. Функциональные узлы последовательностного типа

Функциональные узлы и устройства

последовательностного (накапливающего) типа в отличие от

56

комбинационных цепей содержат в себе элементы памяти. Поэтому их называют автоматами с памятью (АП). АП можно представить в виде двух взаимосвязанных составляющих: памяти и комбинационной цепи. Совокупность состояний всех элементов памяти определяет внутреннее состояние Q автомата. Вектор входных сигналов x в зависимости от текущего состояния АП Qk переводит его в новое состояние Qk+1 и порождает на выходе вектор сигналов y. Поведение такого автомата, называемого автоматом Мили, описывается уравнениями вида:

Qk +1 = f (Qk , x); y = ϕ (Qk , x), k = 0,1,2,.......,

где f называется функцией переходов, а ϕ - функцией выходов.

В отличие от автомата Мили, автомат Мура характеризуется зависимостью выходных сигналов только от его

состояния, т.е. описывается уравнениями вида:

Qk+1 = f (Qk , x); y = g (Qk ), k = 0,1,2,.......,

где g называют сдвинутой функцией выхода.

Для АП характерно наличие в их структуре обратных связей, посредством которых реализуются функции запоминания состояний. АП делятся на асинхронные и синхронные.

Асинхронный АП переходит из одного состояния в другое под воздействием изменений входных сигналов. Роль элементов памяти в нем выполняют элементы задержки сигналов обратных связей (сигналов состояния) или асинхронные элементы памяти (конденсатор с ключевым транзистором, асинхронные защелки и триггеры), управляемые комбинационной цепью. Сигналы состояния вместе с новым набором входных сигналов определяют следующее состояние и вектор выходных сигналов АП.

Синхронный АП меняет свое состояние под воздействием входных сигналов и сигналов состояния в строго определенные моменты времени в соответствии с частотой следования синхронизирующих импульсов тактового генератора. Для фиксации состояния автомата используются синхронные элементы памяти (конденсатор с синхронизируемым ключевым транзистором, синхронные защелки и триггеры).