Skhemotekhnika_Bassalin

.pdf25

большого, опасного для электрических элементов выходной цепи уравнительного тока.

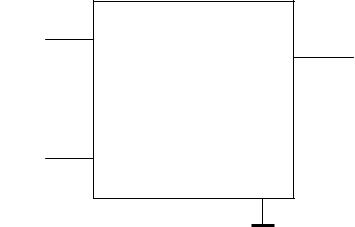

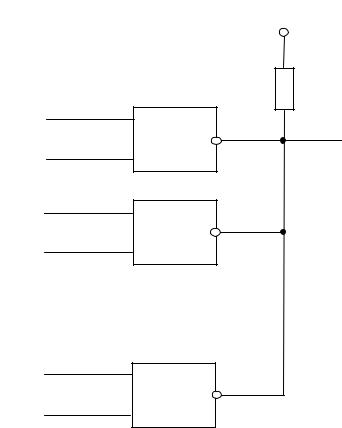

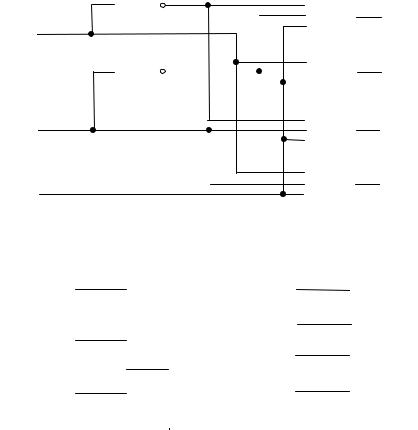

Выход с открытым коллектором заканчивается одиночным транзистором, коллектор которого не соединен ни с одним элементом внутри микросхемы (рис. 2.4). Насыщенное состояние транзистора Т соответствует логическому нулю, запертое – логической единице. Высокое напряжение при запертом транзисторе обеспечивается подключением к выходной линии внешнего резистора, соединенного с источником питания. Выходы с открытым коллектором могут быть соединены

параллельно и обеспечены |

высоким напряжением |

через |

общую внешнюю цепочку |

R - Ucc, как это показано на |

рисунке |

2.5. Такая схема соединения реализует режим поочередной работы логических элементов на общую линию: один элемент активен, остальные заперты. При разрешении одновременной активности всех элементов схема реализует так называемую

операцию монтажной логики |

|

___ ___ _____ |

____________________ |

x1 x2 x3 x4..... xn-1 xn |

= x1 x2 x3 x4 ..... xn-1 xn . |

Для запрещения работы конкретного элемента И-НЕ в магистрально-модульной структуре достаточно подать на один из его входов запрещающий сигнал ОЕ = 0. Значение сигнала ОЕ = 1 на этом входе разрешает работу элемента.

Элементы с открытым коллектором при работе в магистрально-модульных системах защищены от повреждений при ошибочном одновременном подключении к шине нескольких элементов.

Недостаток элементов с открытым коллектором состоит в большом времени задержки при переключении из 0 в 1 из-за малого тока заряда выходной емкости через сопротивление R, которое берется достаточно большим.

Выход с открытым эмиттером типичен для элементов ЭСЛ. Эти элементы обычно имеют два противофазных выхода.

26

x1

. |

F |

|

. |

Т |

|

. |

||

. . . . . |

||

. |

||

|

||

. |

|

xn

Рис. 2.4. Выход с открытым коллектором

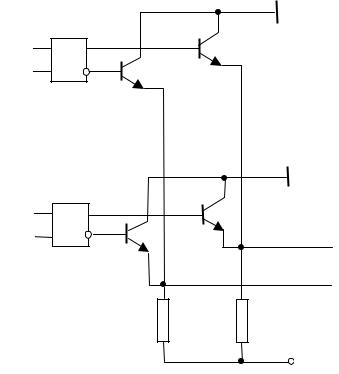

На одном из них реализуется логическая функция ИЛИ, на другом ИЛИ-НЕ. Объединение эмиттерных резисторов нескольких прямых выходов с открытым эмиттером (рис. 2.6) дает объединение всех входных переменных в единую дизъюнкцию (расширение по ИЛИ).

Соединение инверсных выходов приводит к функции

_____ _____ _ _ _ _

F = x1 x2 x3 x4 = x1 x2 x3 x4 ,

т.е. операции И-ИЛИ применительно к инверсиям входных переменных.

Схема, представленная на рисунке 2.6, известна под названием «эмиттерный дот».

x1

x2

x3

x4

xn-1

xn

27

Ucc

R

& ◊

F

& ◊

.

.

.

.

& ◊

Рис. 2.5. Параллельное соединение выходов с открытым коллектором

28

x1 1

x2

x3 |

1 |

|

x4 |

||

x1 x2 x3 x4 |

||

|

____ ____

x1 x2 x3 x4

-Ucc

Рис. 2.6. Схема «эмиттерный дот»

Если соединить прямой выход 1-го элемента с инверсным выходом 2-го элемента, то получается логическая функция

_____ _ _

F = x1 x2 x3 x4 = x1 x2 x3 x4 .

29

Элементы, имеющие выход с открытым эмиттером, для работы на магистраль не используются.

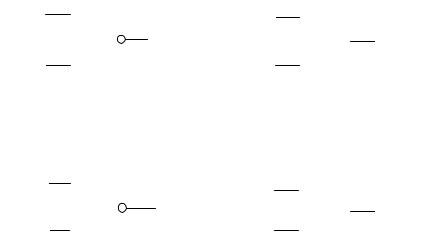

Выход с третьим состоянием помимо состояний 0 и 1 может иметь третье состояние «отключено». В третье состояние, состояние запертых обоих транзисторов (рис. 2.3), когда ток в выходной цепи пренебрежимо мал, элемент переходит под управлением специального сигнала ОЕ (Output Enable). Если ОЕ = 1, то элемент выполняет свою обычную логическую функцию. При ОЕ = 0 он переходит в состояние «отключено».

Буферные элементы с третьим состоянием используются в цифровой аппаратуре для управляемой передачи сигналов по общим линиям связи (магистралям,шинам). Их можно соединять параллельно, но с соблюдением условия

ОЕ1 + ОЕ2 +.......+ ОЕn ≤ 1 ,

т.е. при объединении n выходов в конкретный момент времени активным может быть только один из них. При этом они сохраняют такие положительные качества элементов с логическим выходом, как быстродействие и нагрузочная способность.

Различают инвертирующие и неинвертирующие буферы,

управляемые Н-активными (высокоактивными) и L-активными (низкоактивными) сигналами ОЕ (рис. 2.7).

2.2. Функциональные узлы комбинационного типа

Следующий уровень иерархии вслед за цифровыми элементами занимают функциональные узлы. Они выполняют типовые для цифровых устройств микрооперации, т.е. реализуют низший иерархический уровень внутреннего языка цифрового устройства. Функциональные узлы делятся на комбинационные и последовательностные. Комбинационные узлы (комбинационные цепи) – это устройства, выходные величины которых зависят только от текущих значений входных величин. В отличие от них,

30

последовательностные узлы содержат элементы памяти. Их реакция определяется не только вектором входных сигналов,

OE |

1 |

___ |

OE |

1 |

Вых |

|

|

Вых |

|

|

|

Вх |

|

|

Вх |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

__ |

|

|

__ |

|

|

OE |

1 |

___ |

1 |

|

|

OE |

|

||||

Вх |

|

Вых |

|

|

Вых |

|

|

Вх |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2.7. Возможные сочетания разрешающих и выходных сигналов буферных элементов

но и внутренним состоянием. Поэтому их называют автоматами с памятью.

Рассмотрение функциональных узлов начнем с типовых комбинационных цепей.

Дешифратор (Decoder, DC) осуществляет преобразование n-элементного параллельного кода в код «1 из m», у которого только в одной позиции находится единица, все остальные позиции – нулевые. Количество выходов так называемого полного дешифратора должно равняться числу всевозможных n-

31

разрядных кодовых комбинаций, т.е. m = 2 n. Схемная реализация и условное обозначение двухвходового дешифратора представлены на рис.2.8.

32

|

1 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

& |

F0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x0 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

& |

F1 |

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

& |

F2 |

|||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

|

|

|

|

|

|

|

& |

F3 |

||||

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

а) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x0 |

|

1 |

|

|

DC |

|

0 |

|

|

|

F0 |

|||

|

|

2 - 4 |

|

|

|

|

||||||||

x1 |

|

2 |

|

|

|

|

|

1 |

|

|

|

F1 |

||

|

|

|

|

|

|

2 |

|

|

|

F2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

EN |

|

EN |

|

|

|

|

|

3 |

|

|

|

F3 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.2.8. Двухвходовый дешифратор

а) схемная реализация; б) условное обозначение

33

Информационные входы дешифратора принято обозначать их двоичными весами. EN (Enable) – вход разрешения работы дешифратора. На выходе дешифратора формируются логические функции в виде системы конъюнкций, которая в случае n

информационных входов имеет вид: |

|

||

|

_ _ |

_ |

_ |

F0 |

= x0 x1 ….. xn-2 xn-1EN |

||

|

_ |

_ |

_ |

F1 |

= x0 x1 ….. xn-2 xn-1EN |

||

|

_ |

_ |

_ |

F2 |

= x0 x1 ….. xn-2 xn-1EN |

||

………………………….

_

Fm-1= x0 x1 ….. xn-2 xn-1EN

Fm = x0 x1 ….. xn-2 xn-1EN

Формируя на выходах все конъюнктивные термы, дешифратор позволяет в сочетании с элементами ИЛИ воспроизводить произвольные логические функции от n аргументов. Для этого надо подать на схемы ИЛИ выходы с конъюнкциями, входящими в СДНФ реализуемых логических функций.

Мультиплексор (MUX) выполняет функцию коммутации одного из m информационных входов x0, x1, …, xm-1 на выход F под управлением n адресных (управляющих) входов а0, а1, …, аn- 1, число которых определяется соотношением 2 n = m . Каждой

управляющей двоичной |

комбинации соответствует свой вход, |

||

подключаемый к выходу. |

|

|

|

Функционирование |

мультиплексора описывается так |

||

называемой мультиплексной формулой |

|||

_ _ |

_ _ |

_ _ |

_ |

F = x0 an-1an-2 …a1 a0 x1 an-1an-2 …a1a0 … xm-1 an-1an-2 …a1a0 ,

34

для реализации которой требуется n инверторов, m конъюнкторов и один дизъюнктор.

Схемная реализация мультиплексора для случая n = 2 и m = 4 приведена на рис. 2.9.

Его условное обозначение 2.10. Мультиплексор можно использовать для преобразования поданного на его информационные входы m-разрядного параллельного кода в последовательный, активизируя последовательно управляющие линии значениями адреса от 0 до 2 n-1.

На основе мультиплексоров можно строить универсальные логические модули (УЛМ), настраиваемые на выполнение любой логической функции от n переменных. Схема использования мультиплексора в качестве УЛМ представлена на рис.2.11.

Существует ряд способов настройки УЛМ на произвольные логические функции. Детально с ними можно ознакомиться, обратившись к источнику [2].

Демультиплексор в противоположность мультиплексору коммутирует под управлением n адресных линий единственный входной сигнал с одним из m = 2 n выходов. Данную операцию может выполнить дешифратор (рис.2.8), если на его вход разрешения (EN) подать информационный сигнал, а в качестве входного двоичного кода использовать сигналы управления. Дешифратор, имеющий вход разрешения и выполняющий функцию демультиплексора, называют дешифраторомдемультиплексором. Его условное обозначение приведено на рис.2.12.

Компаратор (CMP) – это устройство, выполняющее функции сравнения двух слов. Для слов a = an an-1 ….. a0 и n-1 ….. b0 компаратор определяет три типа отношений: отношение равенства Fa = b, отношение «больше» Fa > b , отношение «меньше» Fa < b . Признаком выполнения равенства

по i-му разряду слов является логическая функция